AT24C02芯片学习记录

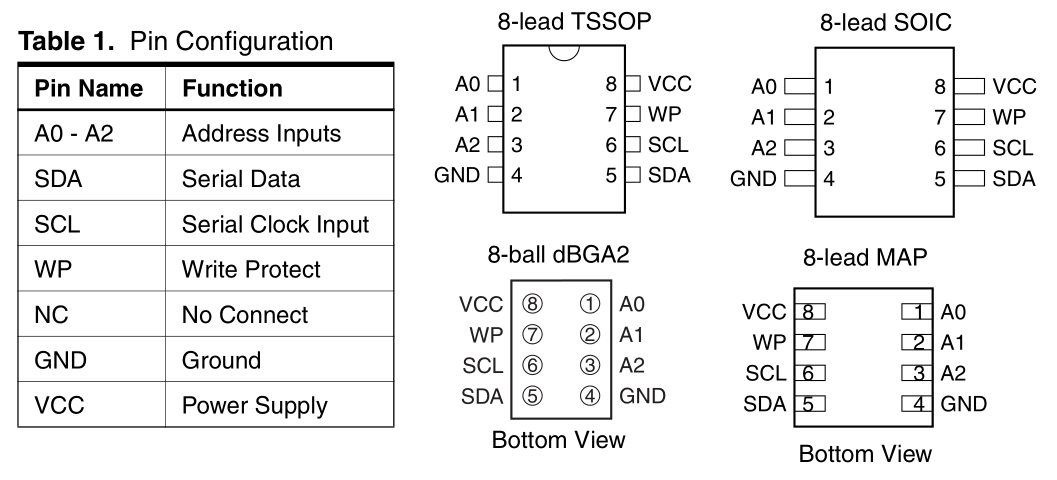

1、首先看AT24C02芯片的引脚说明

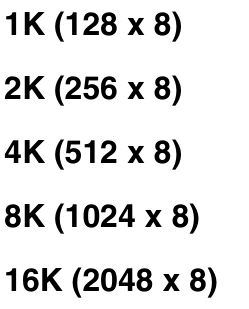

2、芯片的型号与存储容量(bit)的对应关系:

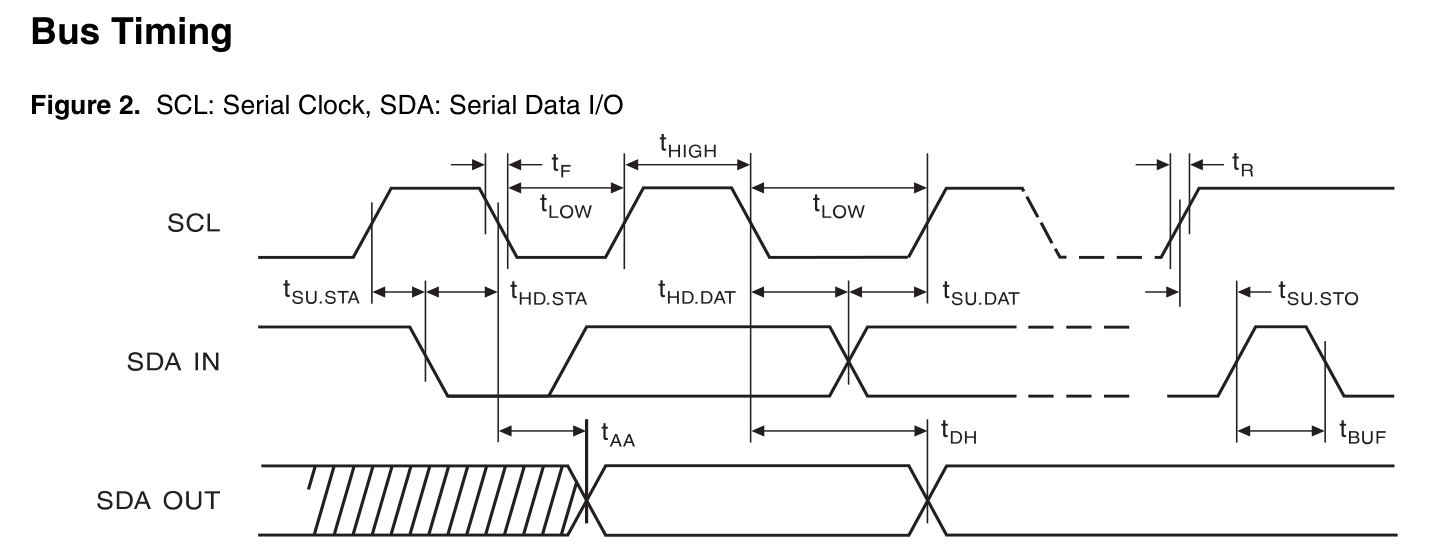

3、总线时序

我对时序的理解:

时钟线分两种:一种是外部时钟源控制时钟线低电平持续多久高电平持续多久,就像串口;

另一种是人为控制低电平持续多久,高电平持续多久,就像IIC、74HC165。

对于IIC,在数据传输的过程中,只有当SCL为低电平的时候,SDA数据才可以修改,

因此,把SCL拉为高电平时,读SDA的数据;

把SCL拉为低电平时,修改SDA的数据。

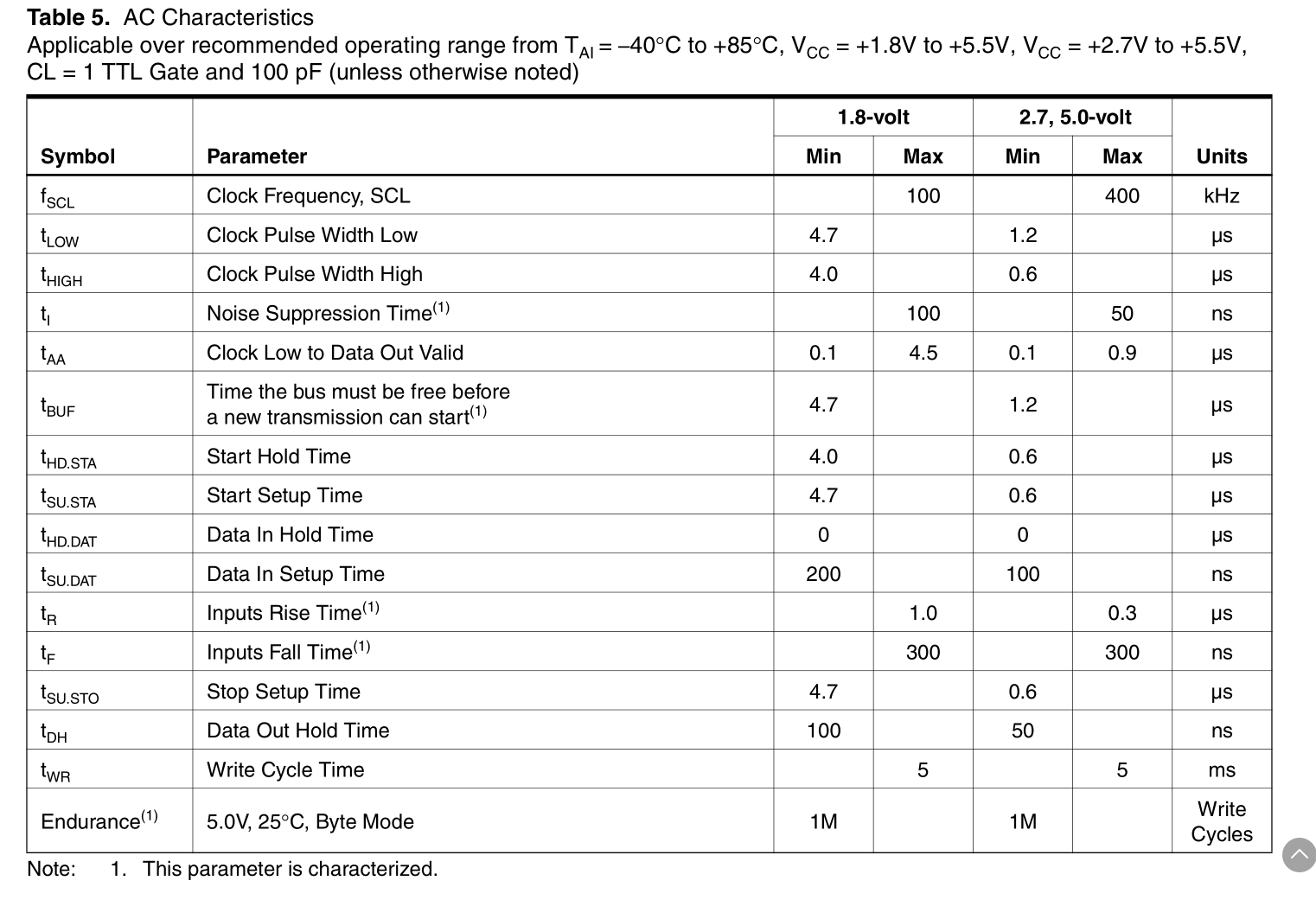

疑问:程序中,将SCL拉高或拉低都要持续一段时间,这个延迟时间有什么讲究吗?

下面这个表有对上面时序图的各种时间进行描述

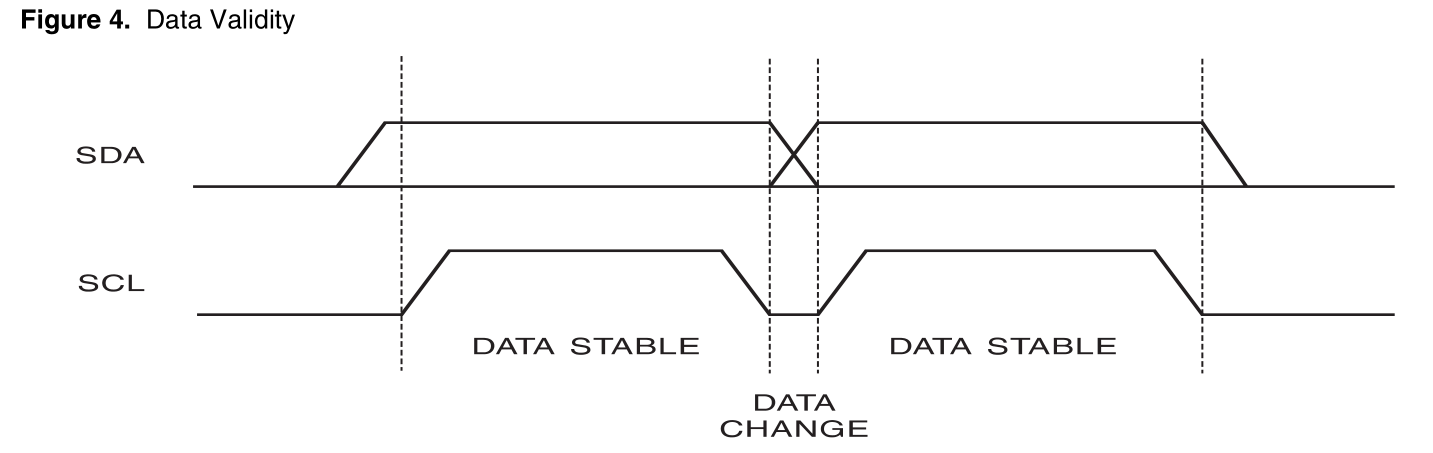

4、数据有效性(数据在什么时候可以改变)

在SCL为高电平时,SDA的输出电平不可改变;

只有在SCL为低电平时,SDA的输出电平才可以改变;

但有两种特殊情况:起始条件和结束条件,这二者SDA电平的改变都是在SCL为高电平的时候。

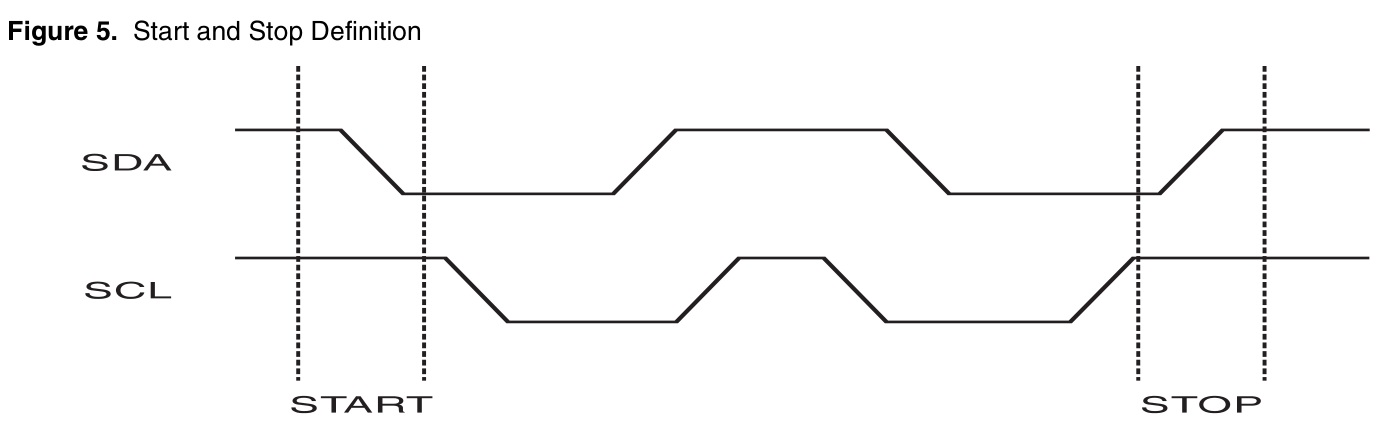

5、起始信号和结束信号

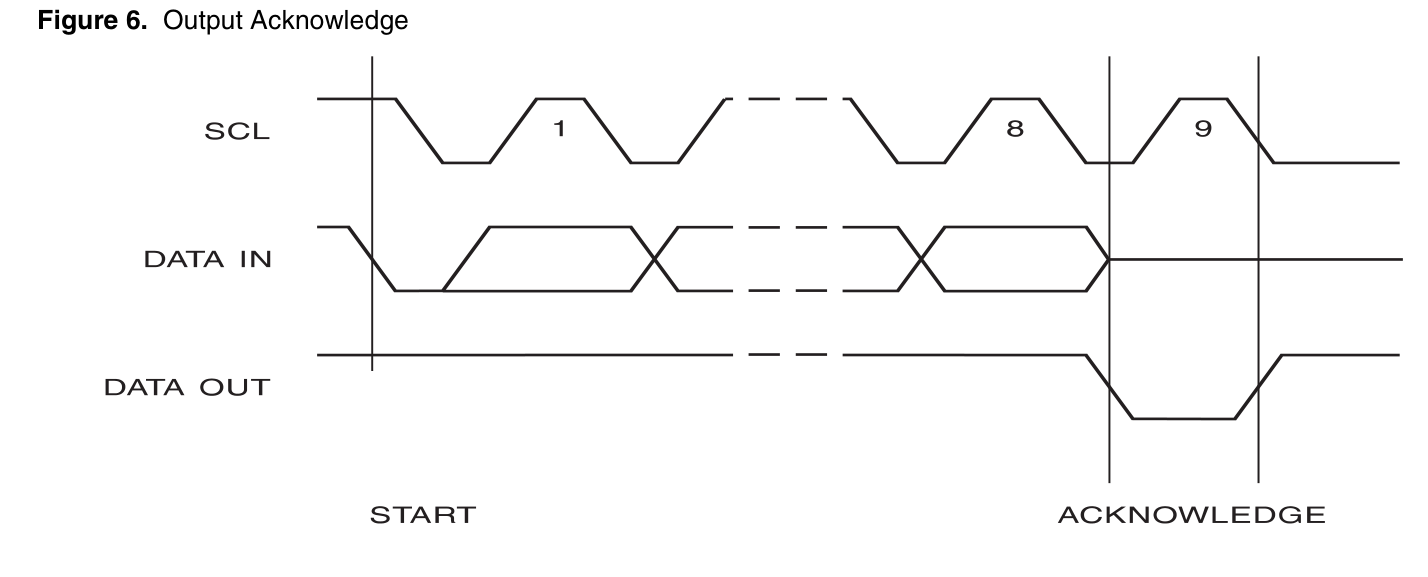

6、应答信号

我对应答信号的理解:

SDA的数据流向是双向的

当主机向从机发送8位数据后,改变SDA的数据流向,从机向主机发送一个低电平,以表示从机接收到了8位数据。

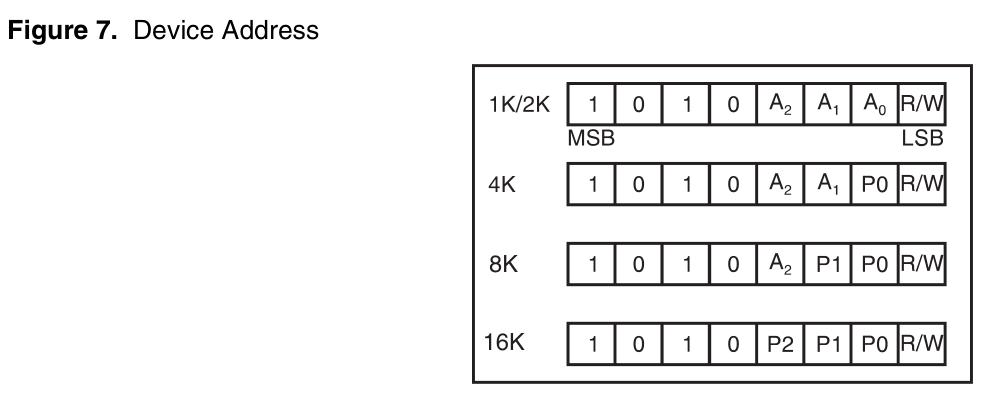

7、设备地址

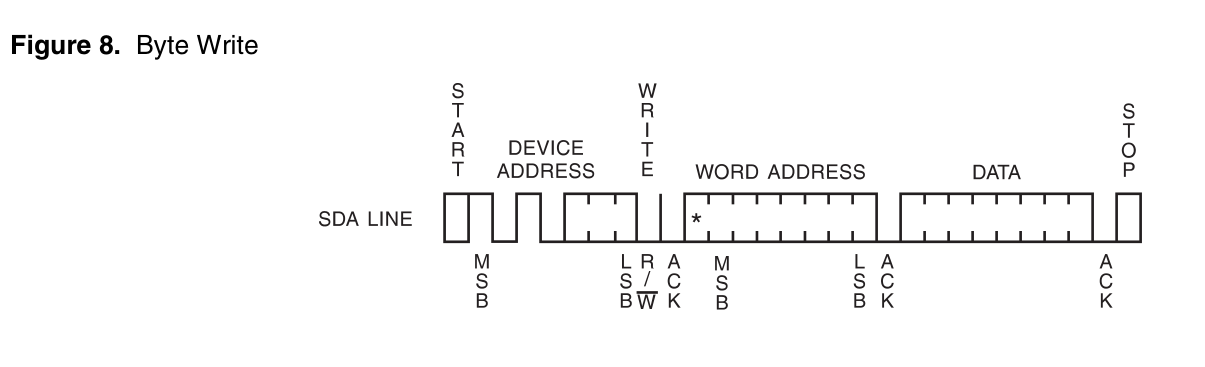

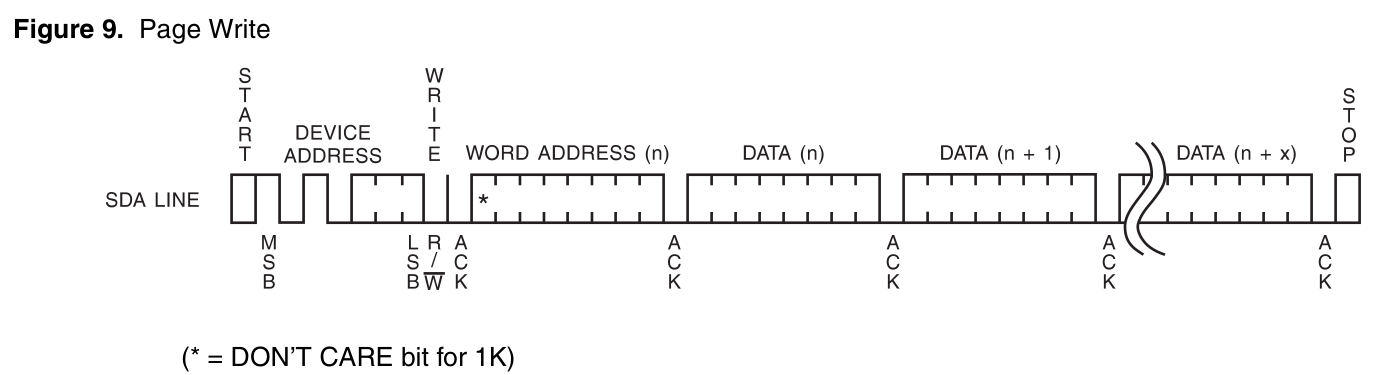

8、写操作

1)字节写操作

2)页写操作

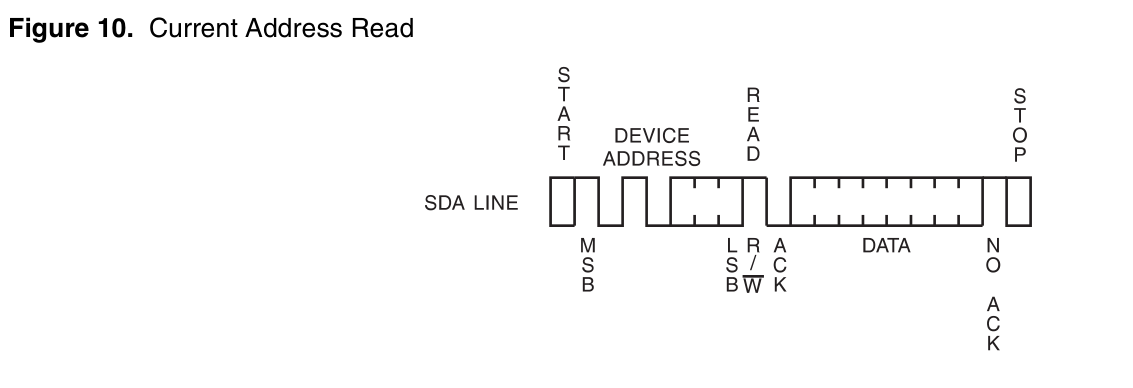

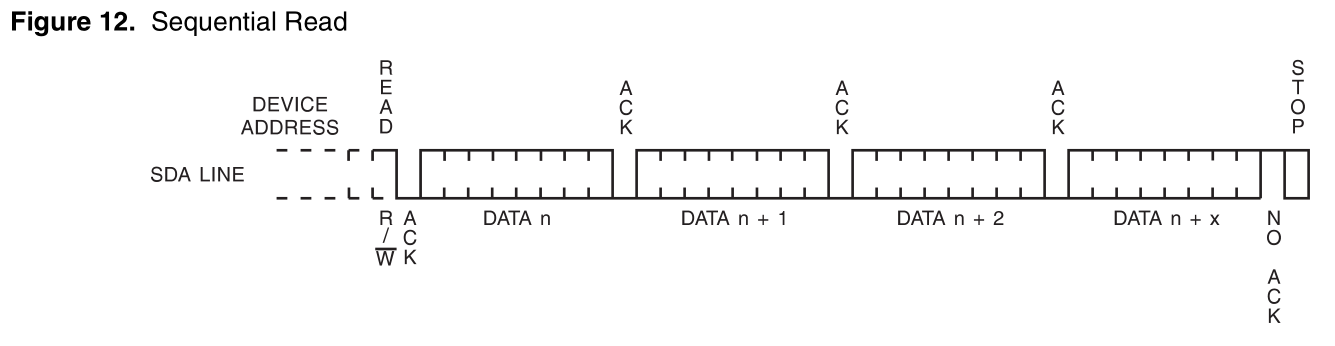

9、读操作

1)当前地址读操作

2)随机读操作

3)顺序读操作

浙公网安备 33010602011771号

浙公网安备 33010602011771号