有限状态机编码(二进制码(Binary)、格雷码(Gray)、独热码(One-Hot))

有限状态机编码对比

| 二进制码 | 格雷码 | 独热码 | |

| 编码说明 | 压缩状态编码 | 一位有效编码 | |

| 组合逻辑/触发器 | 使用最少的触发器,消耗较多的组合逻辑 | 独热码编码的最大优势在于状态比较时仅仅需要比较一个位,从而一定程度上简化了译码逻辑。虽然在需要表示同样的状态数时,独热编码占用较多的位,也就是消耗较多的触发器,但这些额外触发器占用的面积可与译码电路省下来的面积相抵消。 | |

| 适用场景 | 在CPLD中,由于器件拥有较多的地提供组合逻辑资源,所以CPLD多使用二进制编码或格雷码 | 在FPGA中,更多地提供触发器资源,所以在FPGA中多使用独热码编码。 | |

| 适用状态数目 | 对于小型设计(状态数小于4)使用二进制编码 | 大型状态机(状态数大于24)使用格雷码更高效 | 当状态数处于4-24之间时,宜采用独热码编码 |

独热码(One-Hot Encoding)

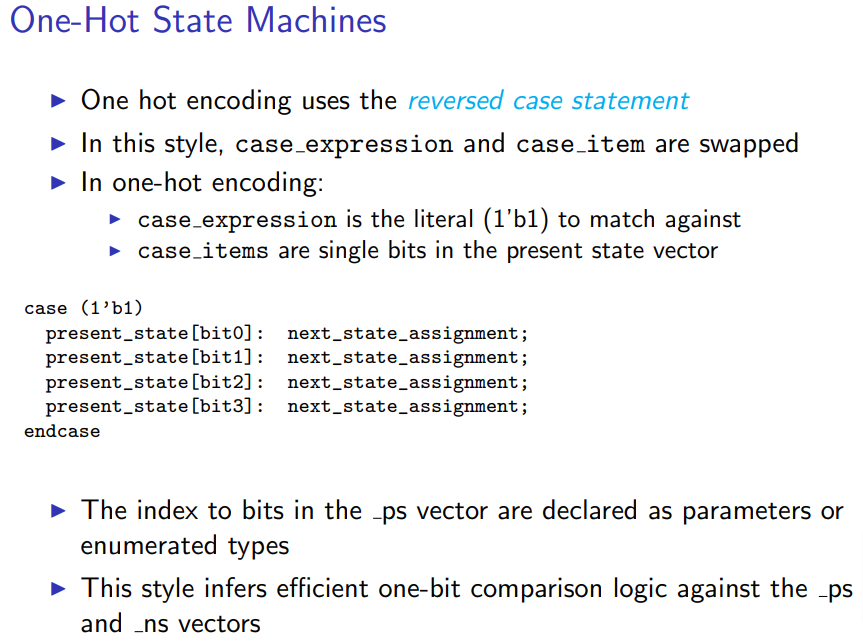

- 很多独热码使用方法都是错的,没有起到简化译码的效果

- 独热码编码的最大优势在于状态比较时仅仅需要比较一个位

There are 3 main points to making high speed state machines by one-hot encoding:

-

Use 'parallel_case' and 'full_case' directives on a 'case (1'b1)' statement

- Use state[3] style to represent the current state

- Assign next state by:

- default assignment of 0 to state vector

- fully specify all conditions of next state assignments, including staying in current state.

Simple example

//Simple example:

reg [2:0] state ;

parameter IDLE=0, RUN=1, DONE=2 ;

always @ (posedge clock or negedge resetl)

if ( ! resetl) begin

state <= 3'b001 ;

out1 <= 0 ;

end

else begin

state <= 3'b000 ;

case (1'b1) // synthesis parallel_case full_case

state[IDLE]:

if (go)

state[RUN] <= 1 ;

else

state[IDLE] <= 1 ;

state[RUN]:

if (finished)

state[DONE] <= 1 ;

else

state[RUN] <= 1 ;

state[DONE]:

state[IDLE] <= 1 ;

endcase

out1 <= state[RUN] & ! finished ;

end

full case,parallel case

Microsoft Word - CummingsSNUG1999Boston_FullParallelCase_rev1_1.doc (sunburst-design.com)

浙公网安备 33010602011771号

浙公网安备 33010602011771号