FPGA:同步复位、异步复位与异步复位同步释放

以下皆以低电平有效的复位信号为例,内容参考 @数字逻辑君Zlaker

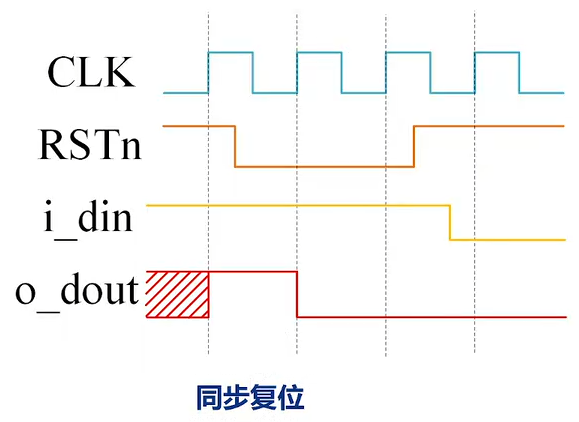

同步复位

module sync_rest(

input sys_clk,

input sys_rst_n,

input i_din,

output wire o_dout

);

reg r_dout;

assign o_dout = r_dout;//方便例化

always @(posedge sys_clk) begin

if (!sys_rst_n)

r_dout <= 1'd0;

else

r_dout <= i_din;

end

endmodule

特点说明:

当复位信号有效时,只能在时钟上升沿的时候更新,能有效避免毛刺干扰,但对复位信号的脉宽有一定的要求(至少大于一个周期)

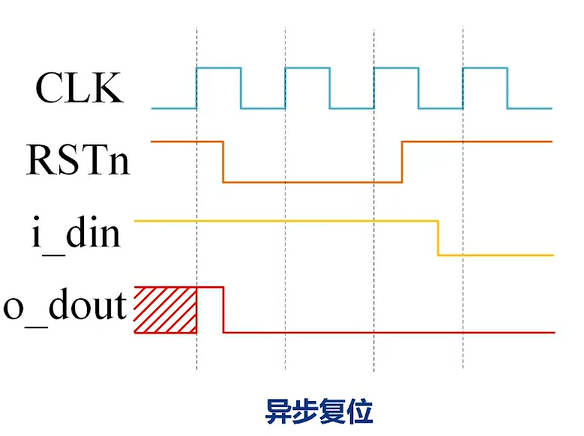

异步复位

module async_rest(

input sys_clk,

input sys_rst_n,

input i_din,

output wire o_dout

);

reg r_dout;

assign o_dout = r_dout;//方便例化

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

r_dout <= 1'd0;

else

r_dout <= i_din;

end

endmodule

特点说明:

在复位信号有效时立即更新,但是抗干扰能力弱,容易被毛刺误触发

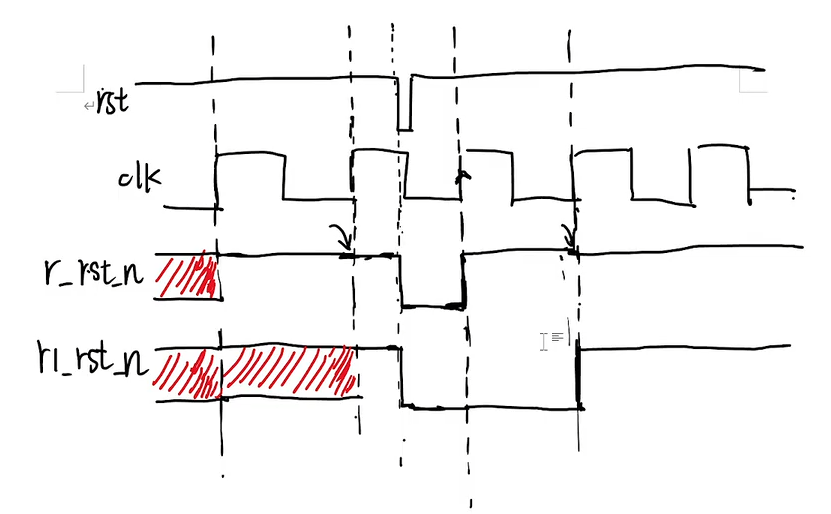

异步复位同步释放

module async_rest_sync_release(

input sys_clk,

input i_sys_async_rst_n,

output sys_rst_n

);

reg [1:0] r_sync_rest_n;

assign sys_rst_n=r_sync_rest_n[1];

always @(posedge sys_clk or negedge i_sys_async_rst_n) begin

if (!i_sys_async_rst_n)

r_sync_rest_n<=2'b00;

else begin

r_sync_rest_n[0]<=1'b1;

r_sync_rest_n[1]<=r_sync_rest_n[0];

end

end

endmodule

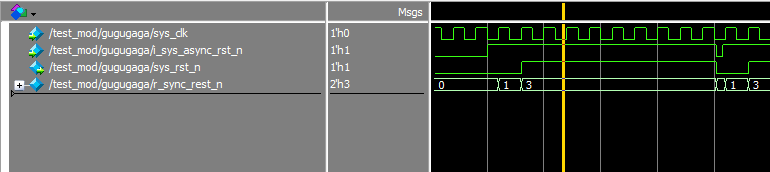

仿真

特点说明:

与异步复位类似,在复位信号有效时立即更新,但是通过寄存器打一拍拓宽了复位信号,这样同步释放后,后续的模块都可以使用同步复位,无需担心捕捉不到脉宽小的复位信号。

浙公网安备 33010602011771号

浙公网安备 33010602011771号