005:ZYNQ_AXI总线学习笔记(2)

接上期文章,继续记录AXI总线学习笔记。

9.AXI通道定义

Channel definition

Each of the independent channels consists of a set of information signals and VALID and READY signals that

provide a two-way handshake mechanism. See Basic read and write transactions on page A3-37.

AXI4和AXI_LITE的5个独立通道中,每个通道都有一组VALID and READY的握手信号。当然这些握手信号是同步于时钟ACLK。

The information source uses the VALID signal to show when valid address, data or control information is available

on the channel. The destination uses the READY signal to show when it can accept the information. Both the read

data channel and the write data channel also include a LAST signal to indicate the transfer of the final data item in

a transaction.

Information和destination并不是指主机和从机。Information是发送方,destination是接收方,理解axi一件事情,主机不一定是发送方,从机不一定接收方,主机从机发送接收没有什么关系,不要混淆,主机从机是定死的,在读写地址和数据时,发送方和接收方在转换。读数据通道和写数据通道都有LAST signal表明传输的最后一个数据。

Read and write address channels

Read and write transactions each have their own address channel. The appropriate address channel carries all of the

required address and control information for a transaction.

读写传输都有自己的地址通道其中包含了传输中需要的地址和控制信息。其中地址是起始地址。

Read data channel

The read data channel carries both the read data and the read response information from the slave to the master, and

includes:

• the data bus, that can be 8, 16, 32, 64, 128, 256, 512, or 1024 bits wide

• a read response signal indicating the completion status of the read transaction

读数据通道包含从机到主机的读数据和读响应的信息。data bus指数据位宽;读响应信号是读的完成状态。5个独立通道中响应信号是写相应信号,而读响应信号包含在读数据通道中。

Write data channel

The write data channel carries the write data from the master to the slave and includes:

• the data bus, that can be 8, 16, 32, 64, 128, 256, 512, or 1024 bits wide

• a byte lane strobe signal for every eight data bits, indicating which bytes of the data are valid.

例如在AXI_SREAM中的M_AXIS_TSTRB信号,如果数据位宽是32bit,M_AXIS_TSTRB的位宽就是4,每一位代表1Byte,可以使能当前32bit中某些字节有效。

Write data channel information is always treated as buffered, so that the master can perform write transactions

without slave acknowledgement of previous write transactions.

每次master执行写事务的时,不需要slave的承认之前的写交易?这里我理解是master写操作可以直接执行,不用考虑从机的想法。

Write response channel

A slave uses the write response channel to respond to write transactions. All write transactions require completion

signaling on the write response channel.

完成一次写事务,从机使用一个写相应来响应。所有的写事务需要一个完成信号在写响应通道上。如果传输成功,时序图上显示,会有一个OKAY的响应信号。

10. Signal Descriptions

Global signals

ACLK

ARESETn

All signals are sampled on the rising edge of the global clock.

俩个全局信号且所有信号在上升沿进行采样。

Write address channel signals-AXI4FULL

以AW开头代表写地址通道。这里列举了一些AXI4关键信号,具体的在手册中再查。

AWADDR Master Write address. The write address gives the address of the first transfer in a write

burst transaction.

主机写地址,指定突发传输的起始地址。

AWLEN Master Burst length. The burst length gives the exact number of transfers in a burst. This

information determines the number of data transfers associated with the address.

INCR:自动突发模式,在INCR模式下: Burst_Length = AxLEN[7:0] + 1;

突发长度:例如在写数据中,主机先发地址和控制信息,然后发送write data的个数,而突发大小指的是每一个write data的数据量大小

AWSIZE Master Burst size. This signal indicates the size of each transfer in the burst.

AWBURST Master Burst type. The burst type and the size information, determine how the address for

each transfer within the burst is calculated.

主机发了起始地址后,从机会根据突发类型和突发大小去计算应该传输到哪个地址。

AWVALID Master Write address valid. This signal indicates that the channel is signaling valid write

address and control information.

AWREADY Slave Write address ready. This signal indicates that the slave is ready to accept an

address and associated control signals.

从机发给主机表示从机准备好接收地址和相关控制信号。

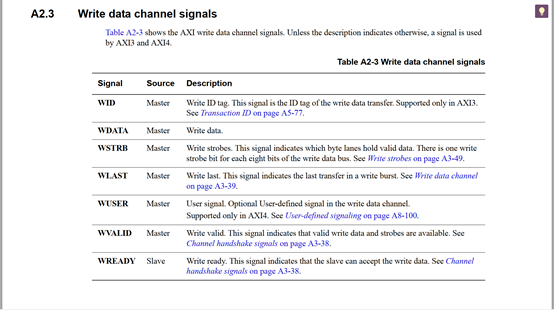

Write data channel signals

WSTRB 可以控制某个WDATA中某个字节有效。WLAST写数据时传输到最后一个数据主机将其拉高。对应的还有RLAST读最后一个数据时拉高最后一位。WUSER是用户自定义信号不需要可以不使用。每个通道都有一组最后的握手信号。

Write response channel signals

B开头都是响应信号,作为从机对写事务的响应。

Read address channel signals

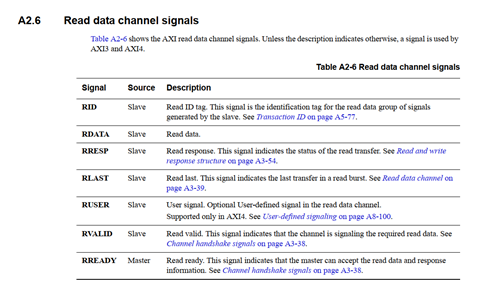

Read data channel signals

11. Burst type

AXI定义了3种突发类型:

FIXED

In a fixed burst, the address is the same for every transfer in the burst.

This burst type is used for repeated accesses to the same location such as when loading or emptying

a FIFO.

每次的地址相同。

INCR

常用模式,每次地址累加,累加大小由传输大小决定。例如每次传输的时候突发大小是4个字节则传输地址也会累加4字节。

WRAP

类似于Incr模式,在达到高地址后会回到最低地址重新累加,有点像异步fifo中的回环。

12. Single Interface Requirements

Clock

All input signals are sampled on the rising edge of ACLK.

All output signal changes must occur after the rising edge of ACLK.

Reset

During reset the following interface requirements apply:

• a master interface must drive ARVALID, AWVALID, and WVALID LOW

• a slave interface must drive RVALID and BVALID LOW

• all other signals can be driven to any value.

Handshake process

All five transaction channels use the same VALID/READY handshake process to transfer address, data, and control information. This two-way flow control mechanism means both the master and slave can control the rate at which the information moves between master and slave. The source generates the VALID signal to indicate when the address, data or control information is available. The destination generates the READY signal to indicate that it can accept the information. Transfer occurs only when both the VALID and READY signals are HIGH.

握手机制中,5个通道都有相同的握手机制传输信息。只有VALID and READY同时为高,然后被ACLK采集到,数据传输有效,至于两个信号的拉高顺序无要求。

single-headed and double-headed

• single-headed arrows point to signals that can be asserted before or after the signal at the start of the arrow

• double-headed arrows point to signals that must be asserted only after assertion of the signal at the start of

the arrow.

读传输中,ARVALID和ARREADY信号是读地址信号。而RVALID和RREADY是读数据信号。

ARVALID单箭头指向ARREADY意味着两个信号拉高无前后顺序关系。

ARVALID和ARREADY双箭头指向RVALID信号意味着必须先拉高ARVALID和ARREADY,才可以执行RVALID或者RREADY.

意思就是读传输中先要地址,才能数据。地址和数据中的握手没有先后顺序的要求。

写传输中,the master must not wait for the slave to assert AWREADY or WREADY before asserting AWVALID orWVALID. the slave must wait for both WVALID and WREADY to be asserted before asserting BVALID.

13.AXI_LITE

AXI_LITE不支持突发传输,每次传输长度1个,整个接口的信号相比AXI4少很多,更加节省资源,适用于小数据量。

我的理解意思就是AXI_LITE最多一次发送32bit或者64bit的数。AXI4最多就支持突发256个128B的数。

Bus width

AXI4-Lite has a fixed data bus width and all transactions are the same width as the data bus. The data bus width must be, either 32-bits or 64-bits

数据总线两种支持32位和64位,位宽没有AXI4灵活。下图是AXI4的支持的数据位宽。

AXI协议就到这里,内容非常多,熟悉整个时序后,我感觉不用太抠细节,在后边工程中再应用回顾。

参考资料:

ARM IHI 0022D

正点原子

浙公网安备 33010602011771号

浙公网安备 33010602011771号