译码器的实现

一、实验目的

熟悉 QuartusII 仿真软件的基本操作,并用 VHDL 语言设计一个异或门。

二、实验内容

1、熟悉 QuartusII 软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、

波形设计)

2、用 VHDL 语言设计一个异或门,最后仿真验证。

3.用 VHDL 语言设计 3-8 译码器,最后仿真实验。

4.用 VHDL 语言设计模型机译码器,最后仿真实验。

三、实验方法

1、 实验方法

采用基于 FPGA 进行数字逻辑电路设计的方法。

采用的软件工具是 Quartus II。

2、 实验步骤

1、 新建,编写源代码。

(1).选择保存项和芯片类型:【File】-【

new project wizard】-【

next】(设置文件路径+设

置 project name 为 xor_d)-【next】(设置文件名 xor_d.vhd—在【

add】)-【properties】

(

type=AHDL)

-【

next】(

family=FLEX10K;name=EPF10K10TI144-4)

-【

next】

-【

finish】

(2).新建:【

file】-【

new】(第二个 AHDL File)-【OK】

2、写好源代码,保存文件(

xor_d.vhd)。

3、编译与调试。确定源代码文件为当前工程文件,点击【

processing】-【

start compilation】

进行文件编译,编译成功。

4、波形仿真及验证。新建一个 vector waveform file。按照程序所述插入 a,b,c 三个节点(

a、

b 为输入节点,c 为输出节点)。(操作为:右击 -【

insert】-【

insert node or bus】-【

node finder】

(

pins=all;【

list】)-【>>】-【

ok】-【ok】)。任意设置 a,b 的输入波形…点击保存按钮保存。

(操作为:点击 name)-右击-【

value】-【

clock】(如设置 period=200;offset=0),同理设置

name B,保存)。然后【

start simulation】,出 name C 的输出图。

5、时序仿真或功能仿真。

6、查看 RTL Viewer:【Tools】-【

netlist viewer】-【RTL viewer】。

四、实验过程

(1) 异或门

1.编译过程

a)源代码如图(VHDL 设计)

b)编译、调试过程

c) RTL 视图

v>

d)结果分析及结论

当两个输入都为 1 或者 0 时,输出为 0;当两者输入互异时,输出为 1.

结果输出正确。

1、 波形仿真

a)波形仿真过程(详见实验步骤)

b)波形仿真波形图

c)结果分析及结论(功能仿真)

0-2.548ns:异或门,0$0=0 正确

2.548-4.012ns:A$B=1$0=1;

4.012-4.979ns:A$B=1$1=0;正确

4.979-7.498ns:A$B=0$1=1

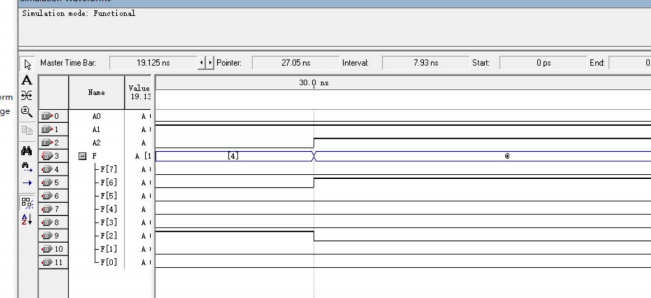

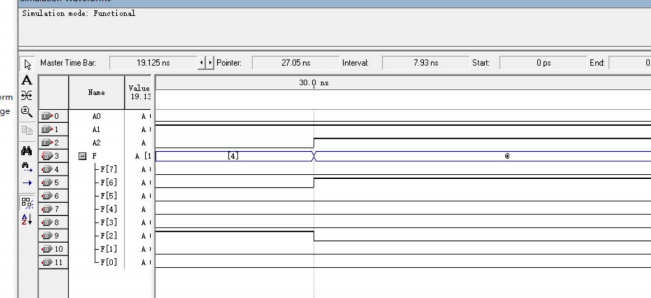

(2) 3-8 译码器

1. 编译过程

a)源代码如图(VHDL 设计)

b)编译、调试过程

c) RTL 视图

d)结果分析及结论

举例当 A0=A1=A2=0 时,输出为 0000001,;A0=A1=0,A2=1 时,输出为 0000100.

对照 RTL 视图结果正确。

2. 波形仿真

a)波形仿真过程(详见实验步骤)

b)波形仿真波形图

v>

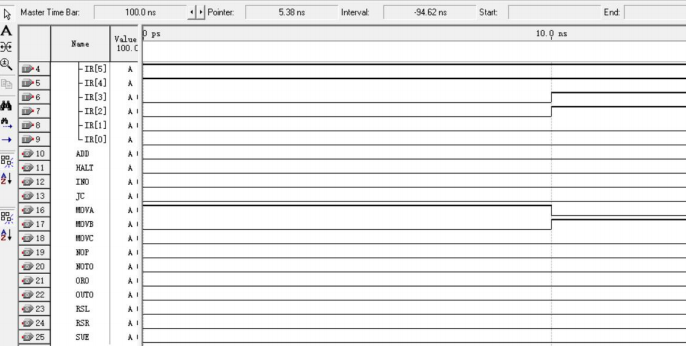

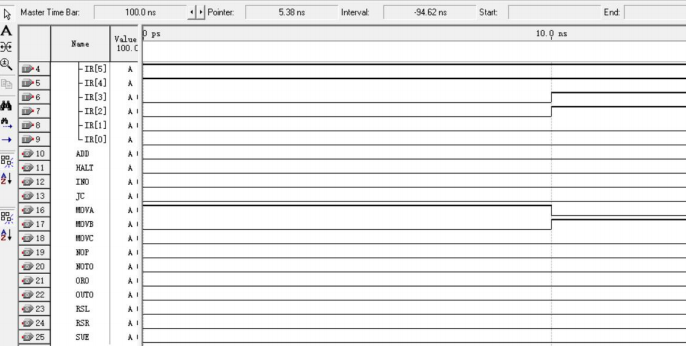

(3) 模型机译码器

1.译过程

c)源代码如图(

d)编译、调试过程(这个警告有点多哈)

c) RTL 视图

d)结果分析及结论

举例当输入为 0011 0000 时,;当输入为 0011 0001 时,;当输入为 0011 0010

时

3. 波形仿真

a) 波形仿真过程(详见实验步骤)

b) 波形仿真波形图

浙公网安备 33010602011771号

浙公网安备 33010602011771号