HDLBits(4) 8.26

2 Verilog语言

2.2 向量

2.2.8 复制操作符

将多个重复向量连接在一起时,使用复制操作符,语法为:{ 重复次数 { 向量 } },eg:

{5{1'b1}} // 5'b11111 or 5'd31 or 5'h1f

{2{a,b,c}} // {a,b,c,a,b,c}

{3'd5, {2{3'd6}}} // 9'b101_110_110.replication for 3'd6 -> concatenation for 3'b101 and 6'b110110重复操作符的应用场景之一是在有符号数的扩展,有符号数的扩展是将符号位填充待扩展的高位,具体操作是通过复制左边较小数字的符号位(最高有效位)来实现的。例如,将4'b0101扩展到8位的符号导致8'b00000101,而将4'b1101扩展到8位的符号导致8'b11111101

故若要实现题目所需要的将8 bit有符号数扩展为32 bit数,只需要assign out = {{24{in[7]}},in};

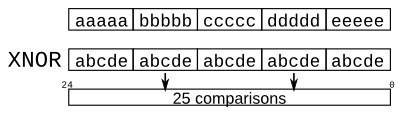

2.2.9 更多的复制操作符

assign out = ~{{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}} ^ {{5{a,b,c,d,e}}};

2.3 模块:层次结构

2.3.1 模块

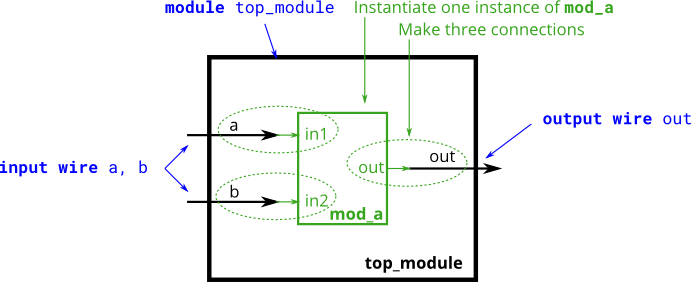

定义模块语法有两种:

一是按端口顺序mod_a instance1 ( wa, wb, wc );wa, wb, wc 分别连接到模块的 第一个端口(in1),第二个端口(in2)以及第三个端口(out)具体如下:

module mod_a (input in1 , input in2 , ouyput out);

//Module body

endmodule但这种方法存在弊端,一旦端口列表发生改变,所有模块实例化中的端口连接都需要改变,需要查找和更改模块的所有实例化以匹配新的模块

二是按端口名称mod_a instance2 ( .out(wc), .in1(wa), .in2(wb) );即将wa,wb,wc分别连接到了in1,in2,out端口。在这种方式中根据端口名称指定外部信号的连接。这样一来就和端口声明的顺序完全没有关系。一旦模块出现改动,只要修改相应的部分即可。实际上,一般都使用这种方式来进行模块实例化

2.3.2 按位置连接端口

module top_module ( input a, input b, output out );

mod_a name(a,b,out);

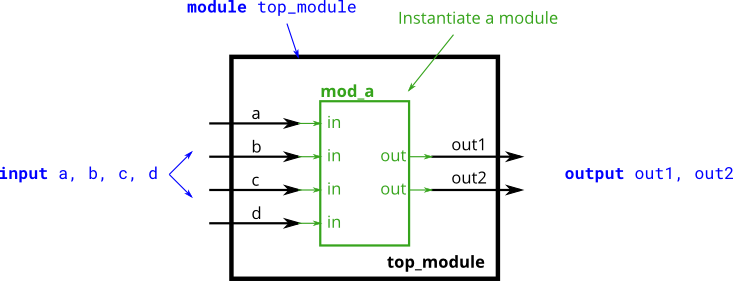

endmodule2.3.3 按名称连接端口

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a name (

.out1(out1),

.out2(out2),

.in1 (a ),

.in2 (b ),

.in3 (c ),

.in4 (d )

);

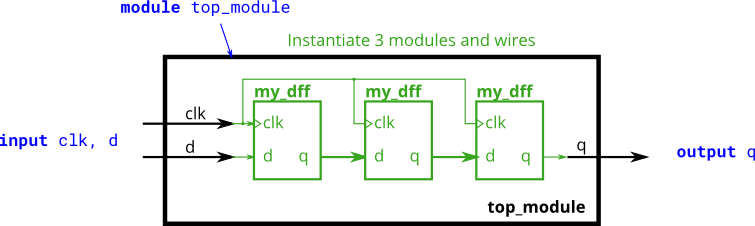

endmodule2.3.4 三模块

module top_module ( input clk, input d, output q );

wire q1,q2;

my_dff u1_my_dff (

.clk(clk),

.d(d),

.q(q1)

);

my_dff u2_my_dff (

.clk(clk),

.d(q1),

.q(q2)

);

my_dff u3_my_dff (

.clk(clk),

.d(q2),

.q(q)

);

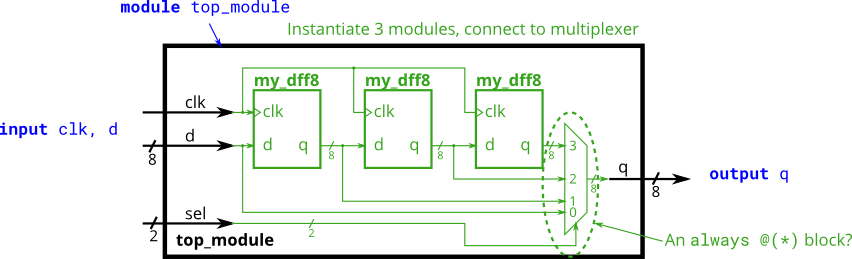

endmodule2.3.5 模块和矢量

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0]o1,o2,o3;

my_dff8 u1_my_dff (

.clk(clk),

.d(d),

.q(o1)

);

my_dff8 u2_my_dff (

.clk(clk),

.d(o1),

.q(o2)

);

my_dff8 u3_my_dff (

.clk(clk),

.d(o2),

.q(o3)

);

always @(*)

case(sel)

2'h0: q = d;

2'h1: q = o1;

2'h2: q = o2;

2'h3: q = o3;

endcase

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号