数据通路与总线结构 硬布线控制器

华中科技大学-计算机组成原理

CPU的主要功能

- 数据加工:算术运算和逻辑运算

- 程序控制:顺序控制

- 操作控制:取指译码产生执行部件所需的操作控制信号

- 时序控制:控制操作信号的产生时间和持续时间

- 异常控制:异常处理,外设交互

- 主要寄存器

| PC(Program Counter) | X86:EIP |

| IR(Instruction Register) | 可选 |

| AR(Address Register) | 可选 |

| DR(Data Register) | 可选 |

| AC(Accumulate Register) | 可选 |

| PSW(Program Status Word) | 可选,X86:EFLAGS |

- 运算器

| ALU(Arithmetic and Logic Unit) | 进行算术逻辑运算 |

| 通用寄存器组(EAX,EBX,ECX,EDX,ESI,EDI,ESP,EBP) | 存放操作数 |

| 暂存器 | 暂存从主存中读出的内容,在ALU输出端设暂存器T存放运算结果,程序员不能访问它们 |

| PSW | 保留算术逻辑运算指令或测试指令结果建立的状态信息 |

| 移位器 | 对运算结果移位,暂存器T有移位功能 |

| 计数器CT | 控制乘除运算的操作步数 |

- 控制器:

| PC | 指出下一条指令在主存中的地址 |

| IR | 保存当前执行的指令代码 |

| AR | 保存当前CPU访问的内存单元的地址 |

| DR | 暂存写入主存的指令或数据 |

| ID(Instruction Decoder) | 分别对操作码,寻址方式,地址码进行译码,向控制器提供操作信号 |

| 时序系统 | 产生时序信号 |

| 微操作信号发生器 | 根据ID、PSW的内容以及时序线的内容,产生控制信号 |

数据通路 Datapath

数据通路:CPU内部各执行部件间传送信息的路径。

通路的建立由控制信号控制,受时钟驱动。不同指令的数据通路不同,同一指令在执行的不同阶段的数据通路也不相同。

分类:

- 共享通路(总线型):主要部件都连接在公共总线上,各部件通过总线进行数据传输。

| 优点 | 缺点 |

|---|---|

| 结构简单,实现容易,早期计算机普遍使用 | 总线成为竞争资源,并发性较差,需要分时使用总线,效率低 |

- 专用通路:数据传输的双方都增加了专用的数据通路,不需要和其他设备竞争总线。可以看做多总线结构

| 优点 | 缺点 |

|---|---|

| 并发度高,性能好 | 设计复杂,成本高 |

影响时钟频率的因素

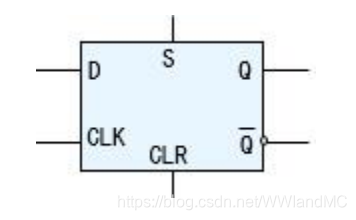

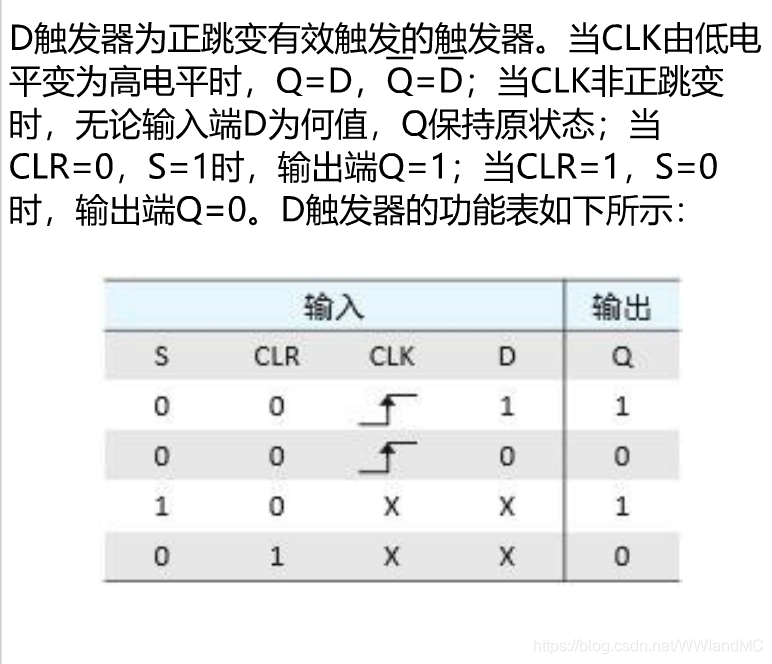

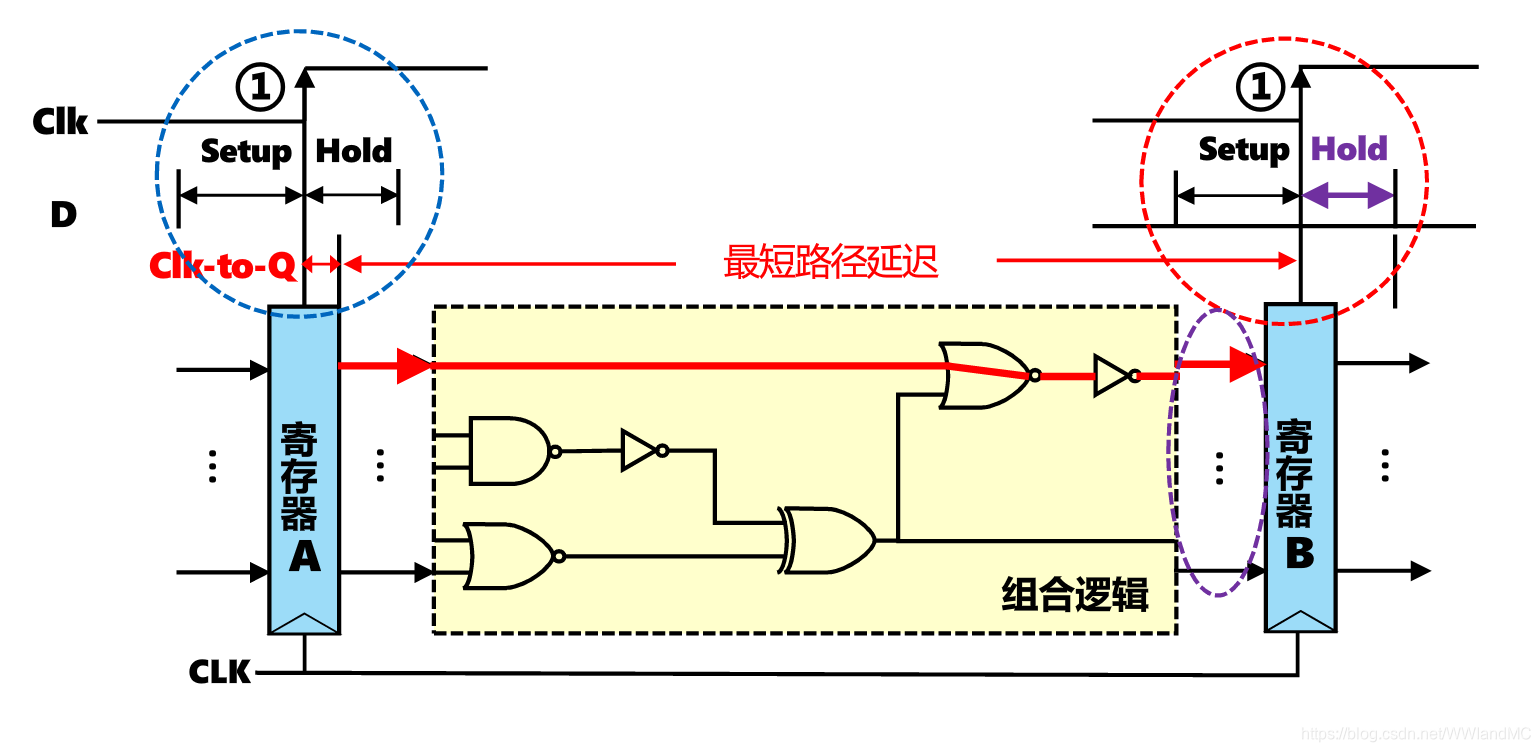

D触发器定时模型

| Setup Time | 在时钟上跳沿来临之前,输入必须保持一段稳定时间 |

| Hold Time | 时钟上跳沿到来之和,输入仍然要保持一段稳定时间 |

| 触发器延迟Cllk_to_Q | 时钟上跳沿到来之后,经过一个触发器延迟,D触发器存储的数据更新 |

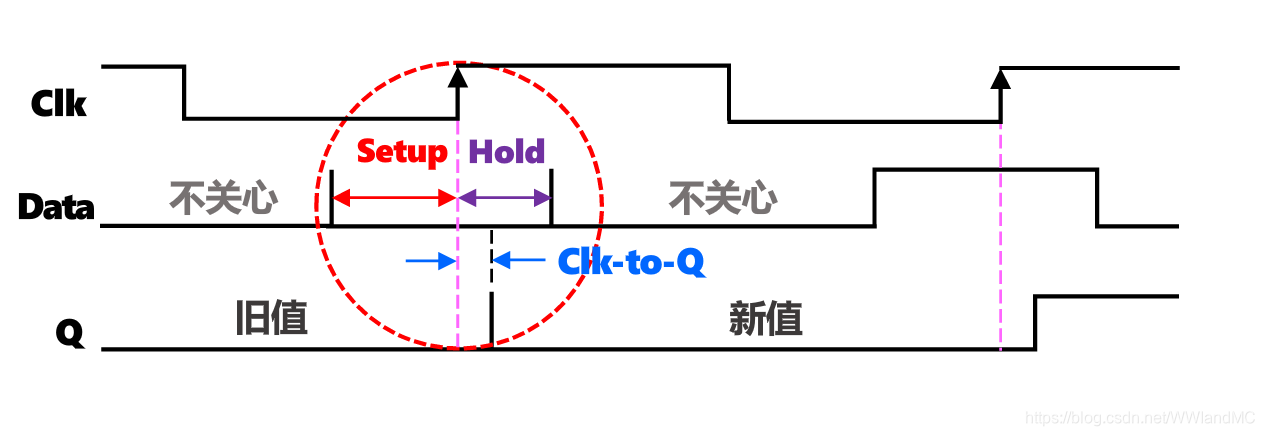

数据通路与时钟周期的关系

| 时钟周期 > Clk_to_Q + 关键路径时延(组合逻辑中路径最长的) + Setup Time | 让数据能锁存在B |

| Clk_to_Q + 最短路径时延 > Hold Time | 在B进行数据锁存的同时,A的数据进行更新并输出,会改变B的输入,破坏B的Hold Time |

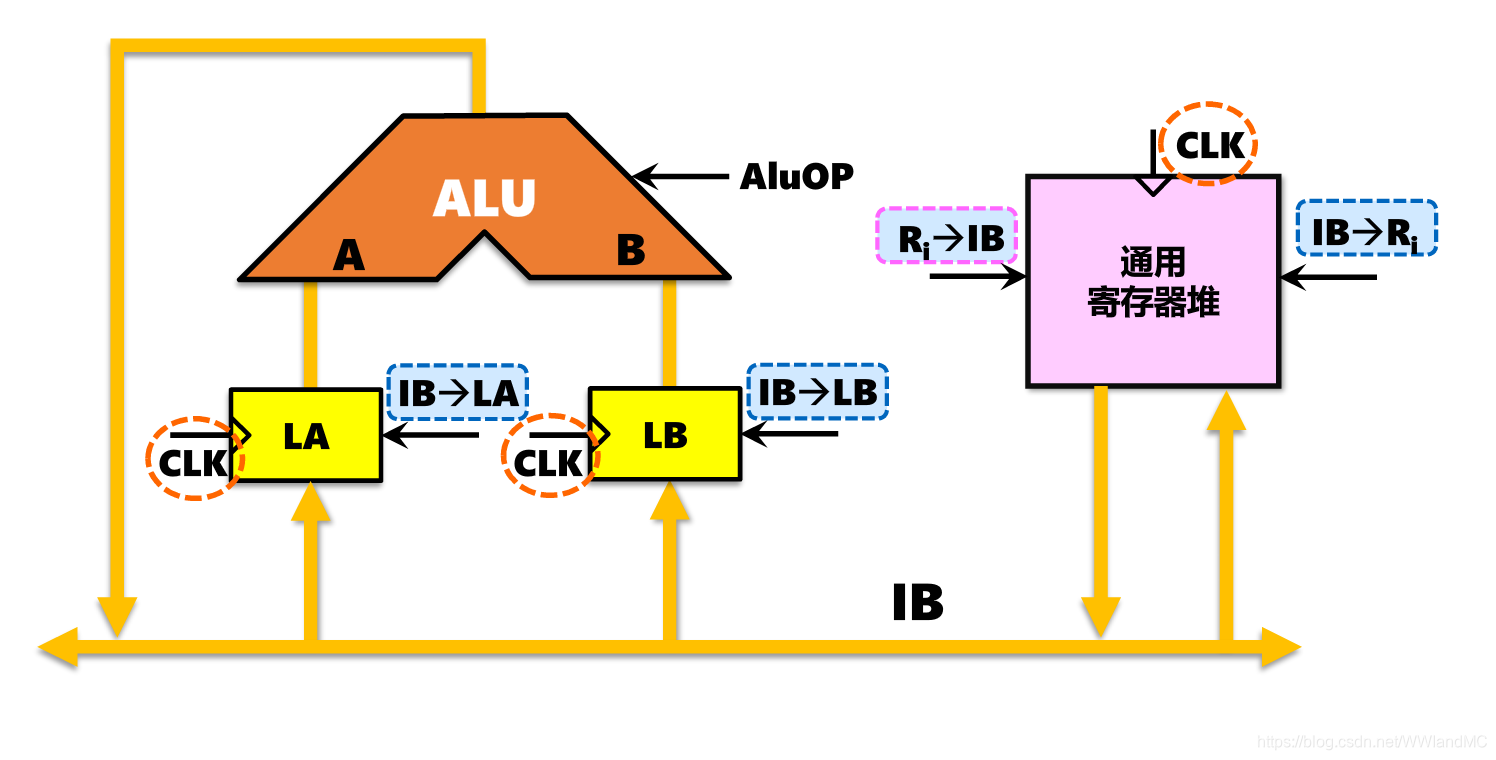

单总线结构中的Dp

一组总线无法给ALU的两个输入端提供不同的数据,为了保证运算器的时序,增加锁存器LA,LB。

一组总线无法给ALU的两个输入端提供不同的数据,为了保证运算器的时序,增加锁存器LA,LB。

IB:Internal Bus

ADD R0,R1 ;单总线结构执行ADD

- 给出R0 -> IB,寄存器R0的内容通过总线传输到LA的输入端,给出写使能信号IB -> LA,第一个时钟上跳沿到来时,数据便锁存在LA。

- 给出R1 -> IB,R1传输到LB的输入端,给出IB -> LB,第二个时钟上跳沿到来时,数据便锁存在LB。

- 给出运算操作符AluOP,ALU进行运算,运算结果传输到通用寄存器堆的输入端,给出写使能信号,第三个时钟上跳沿到来时,数据便锁存在R0中。

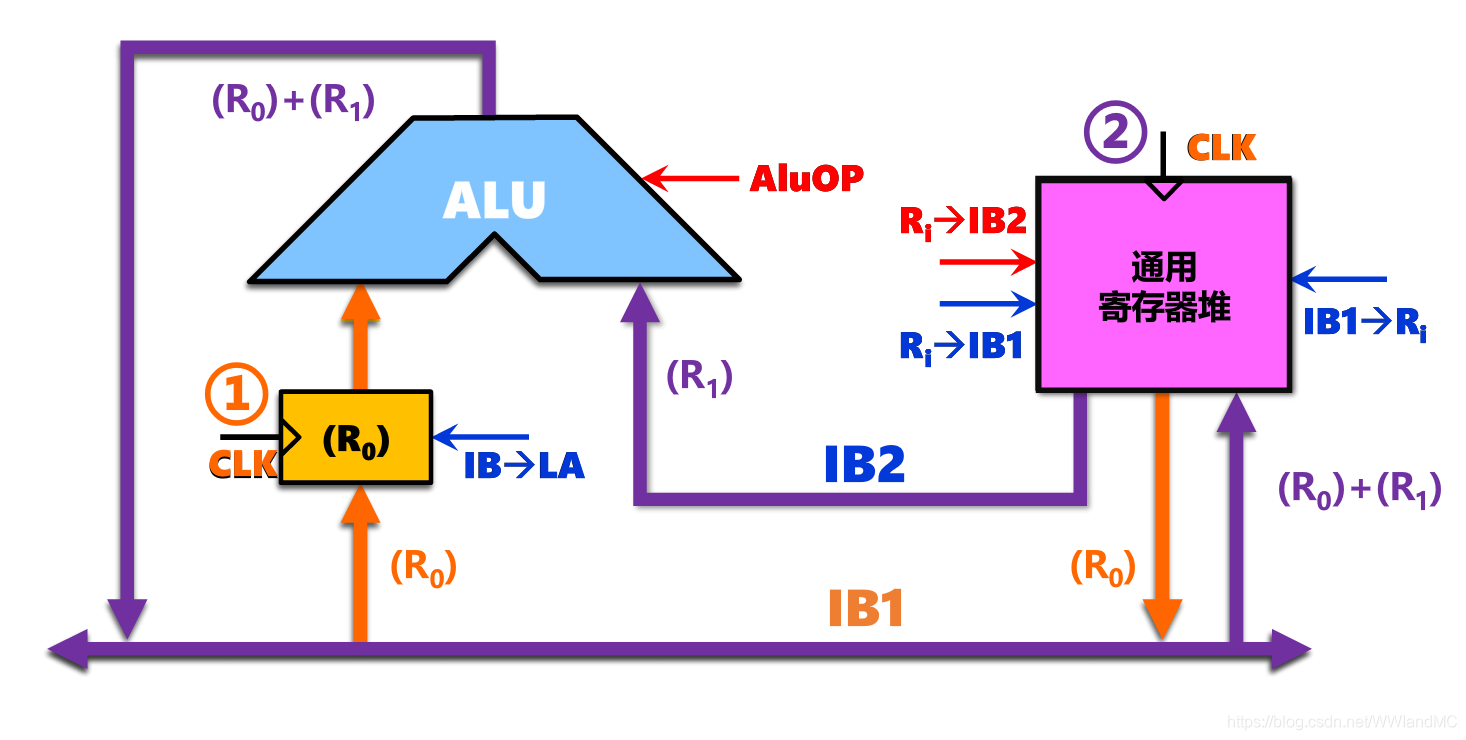

双总线结构中的Dp

ADD R0,R1 ;单总线结构执行ADD

- 给出R0 -> IB1,寄存器R0的内容通过总线传输到LA的输入端,给出写使能信号IB -> LA,第一个时钟上跳沿到来时,数据便锁存在LA。

- 给出R1 -> IB2,R1传输到ALU的输入端。给出运算操作符AluOP,ALU进行运算,运算结果传输到通用寄存器堆的输入端,给出写使能信号,第二个时钟上跳沿到来时,数据便锁存在R0中。

三总线结构中的Dp

| 单总线 | 2个锁存器,3个时钟周期 |

| 双总线 | 1个锁存器,2个时钟周期 |

| 三总线 | 0个锁存器,1个时钟周期 |

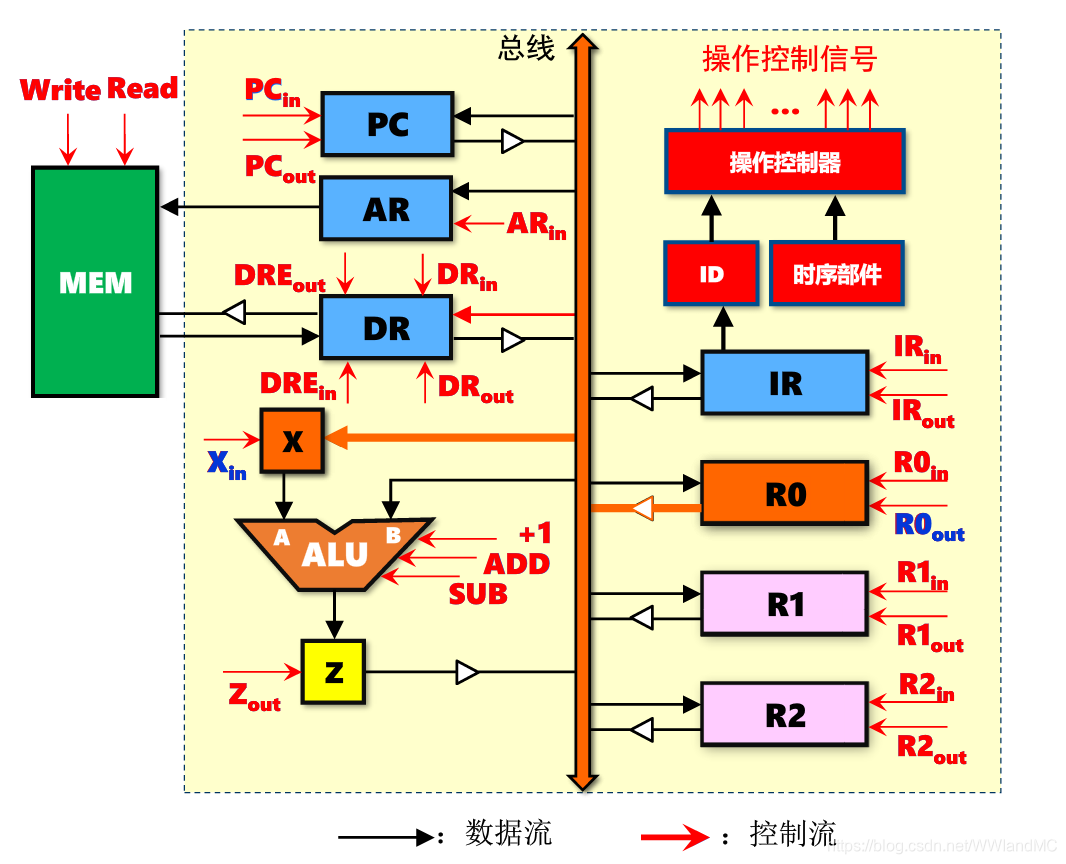

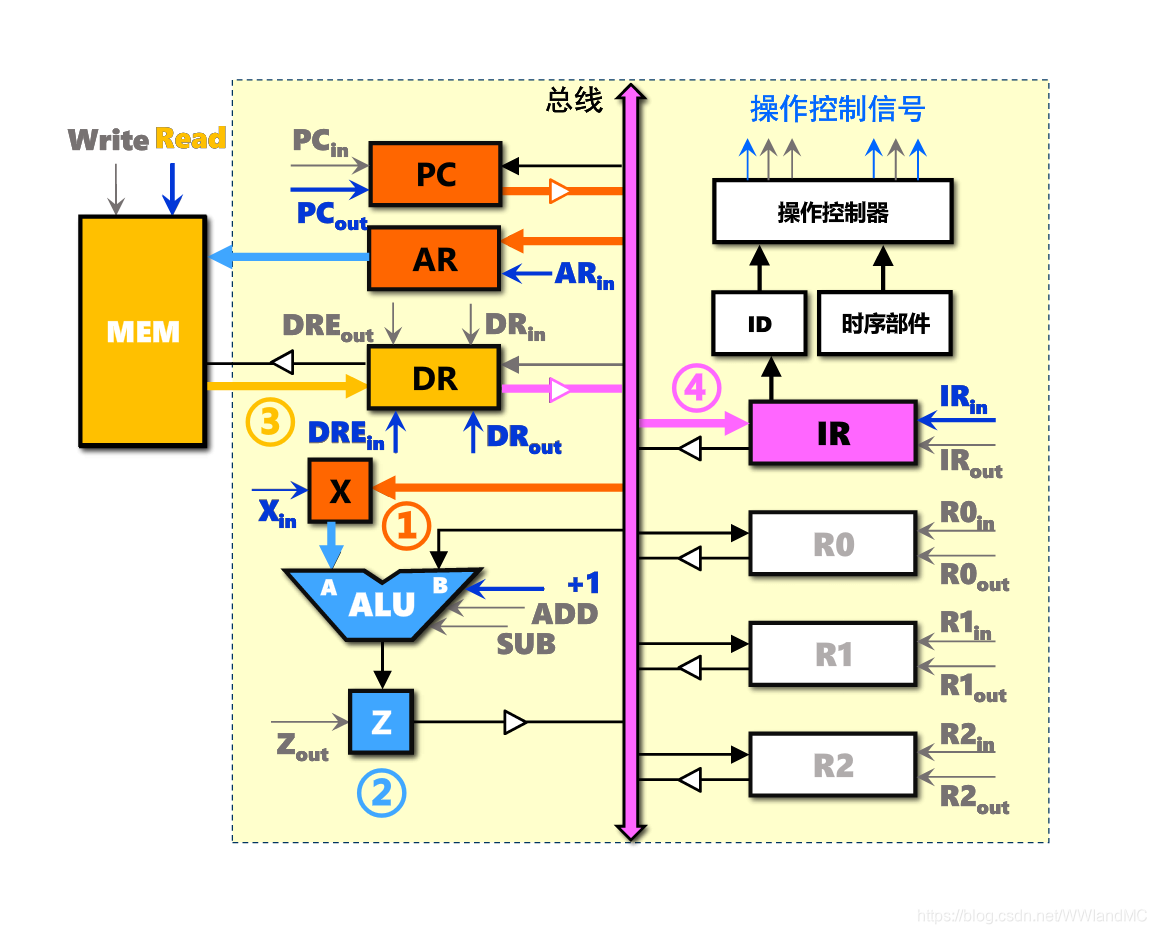

单总线结构CPU

用一组总线连接整个计算机系统的各大功能部件,各大部件之间的所有信息传送都通过这组总线。

用一组总线连接整个计算机系统的各大功能部件,各大部件之间的所有信息传送都通过这组总线。

| 控制信号 | 说明 |

|---|---|

| IRout、PCout、…R1out等一系列out信号 | 控制三态门将寄存器值输出到总线,这些信号是不能并发,同时在同一条总线上输出会造成信号的冲突(DREout除外) |

| IRin、PCin、…R1in等一系列in信号 | 控制寄存器使能端将总线数据锁存,通过时钟驱动完成 |

| +1、ADD、SUB | 运算控制信号,有互斥性 |

| Write、Read | 内存读写控制信号(时钟驱动) |

| 优点 | 缺点 |

|---|---|

| 设计简单 | 总线变成竞争资源,需要分时使用,并发度低 |

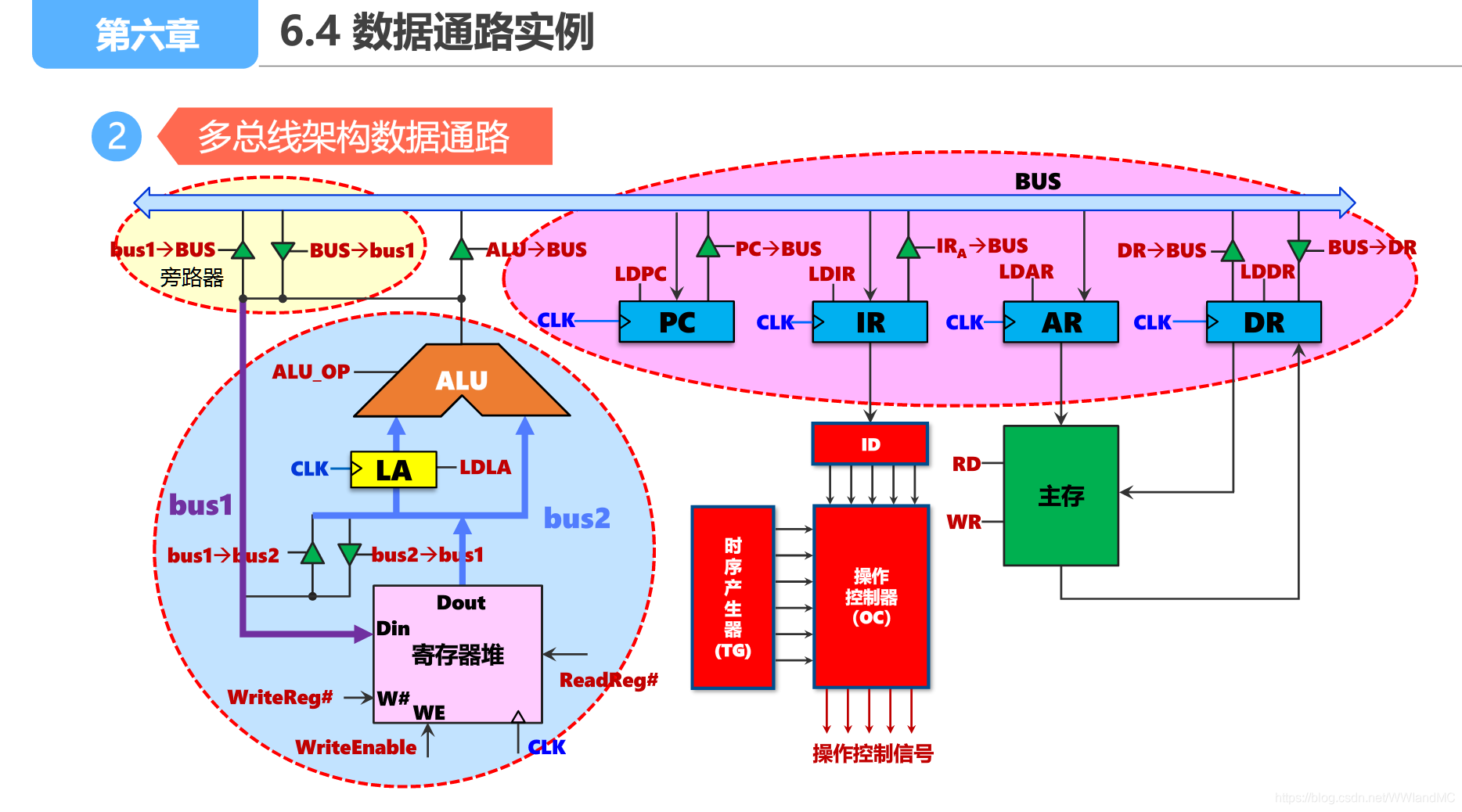

多总线结构

BUS:主存,外设接口通过系统总线AB,DB,CB与CPU相连

旁路器:两个方向相反的三态门,控制总线之间进行单向的信号传递

运算器:双总线结构,需要两个时钟周期

多总线架构CPU,取指和运算可以并发。

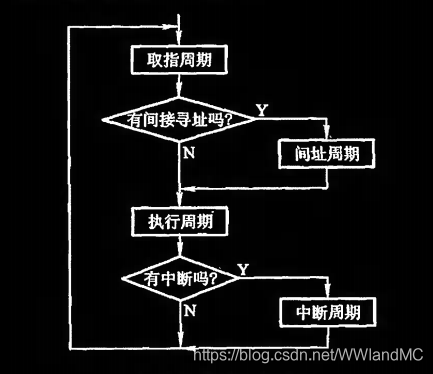

指令周期

指令执行的流程

| 取指周期 | 以PC的内容为地址访问主存,将指令从主存取出送到IR,然后PC + 1(1是指一条指令的字节长度) |

| 取操作数周期 | 由具体的寻址方式计算操作数的地址并取出操作数 |

| 执行周期 | 完成指令操作码规定的动作,包括传送结果和记录状态信息。 |

| 中断周期 | 保存当前PC的内容,待执行完中断服务后程序可以回到间断处 |

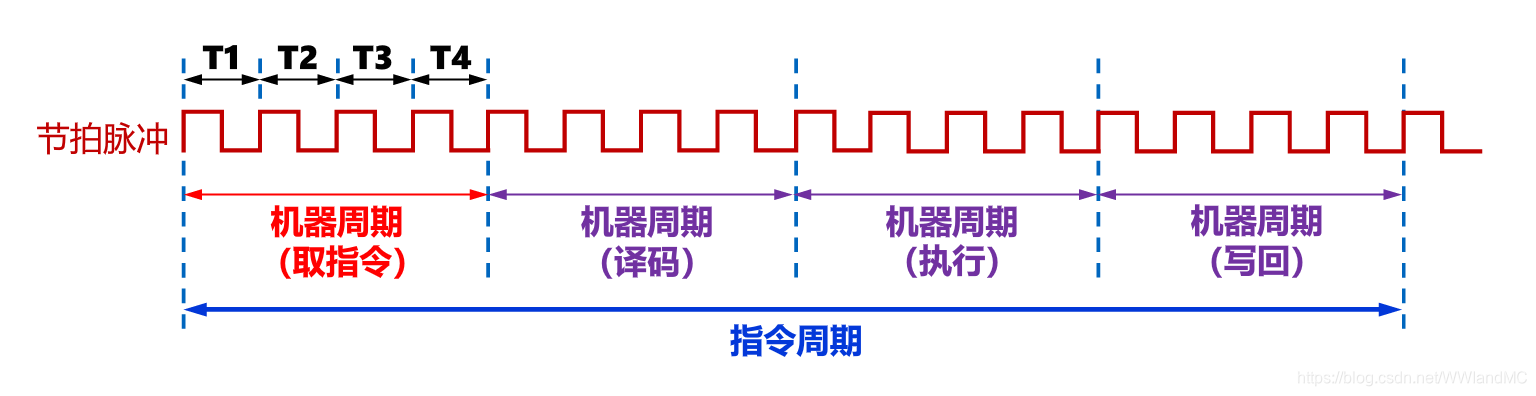

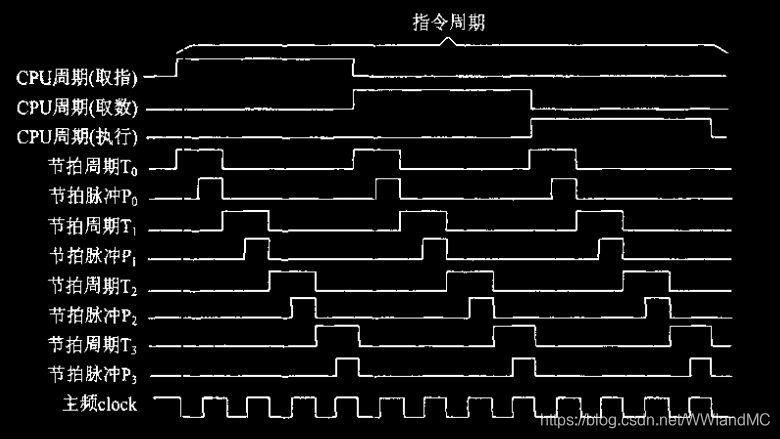

- 时间周期(T1、T2、T3、T4):能完成一次微操作(例如寄存器写入操作)

- 机器周期:从主存取出一条指令的最短时间(从Cache读的时间),可完成复杂操作

- 指令周期:完成 取值 -> 译码 -> 执行 (可能还要回写) 的时间

时序与控制

同步控制方式:

- 定长指令周期:所有指令的执行时间都是一样的。若指令的复杂程度差异很大,规定统一的指令周期会造成浪费

- 变长指令周期:指令周期长度不固定,CPU周期也不固定,含有的节拍数根据需要而定,与内存存取周期和总线周期没有固定关系。根据指令具体要求和执行步骤,确定安排几个CPU周期,以及每个CPU周期中有多少个节拍周期和节拍脉冲。

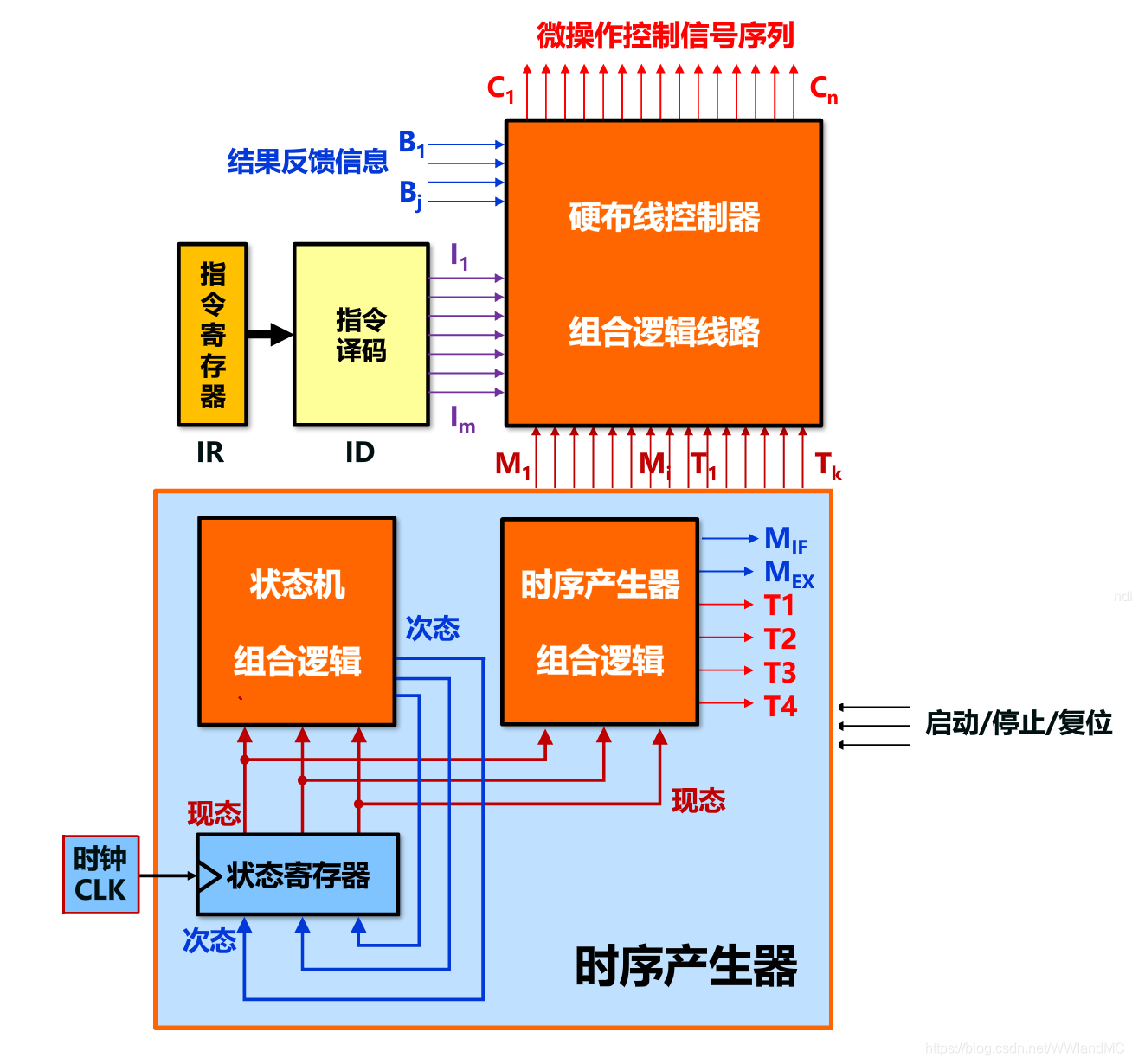

硬布线控制器

| 输入信号 | 输出信号 |

|---|---|

| 指令译码器的输出 | 一组带有时间标志的微操作控制信号 |

| 时序信号 | |

| 程序运行的结果特征和状态(反馈信号) |

设计流程:

- 根据CPU的结构写出每条指令的操作流程图并分解为微操作序列

- 选择合适的控制方式和控制时序

- 对微操作流程图安排时序,排出微操作时间表

- 根据时间表写出微操作表达式

- 根据表达式设计组合逻辑电路

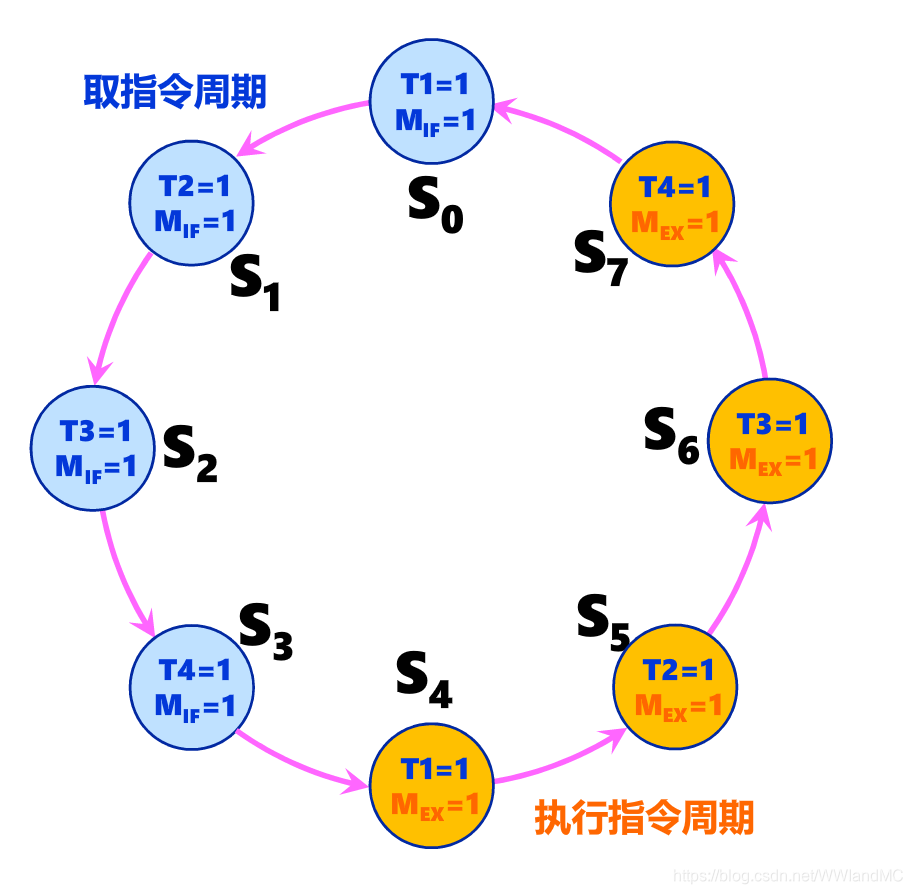

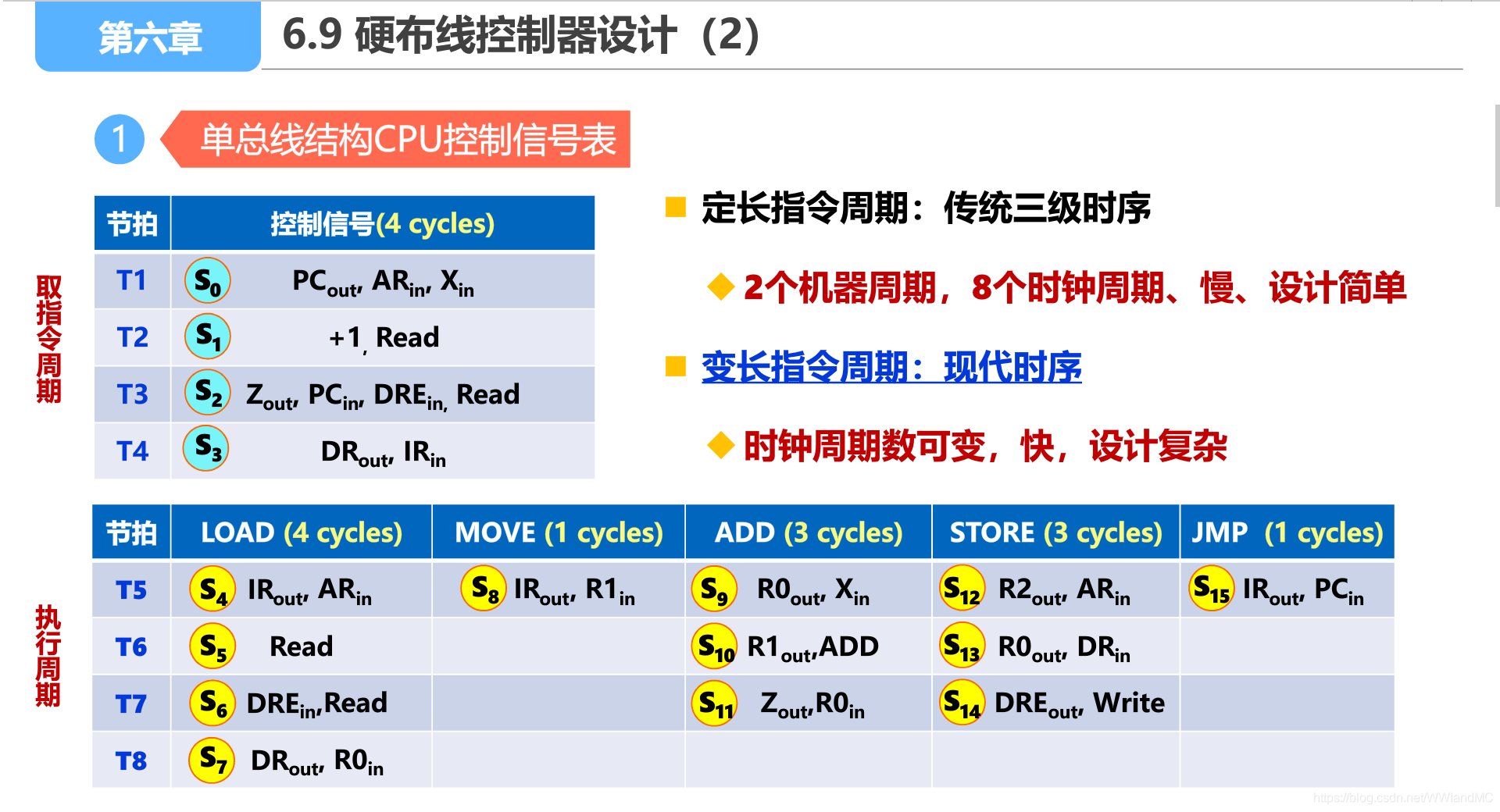

早期三级时序系统:定长指令周期

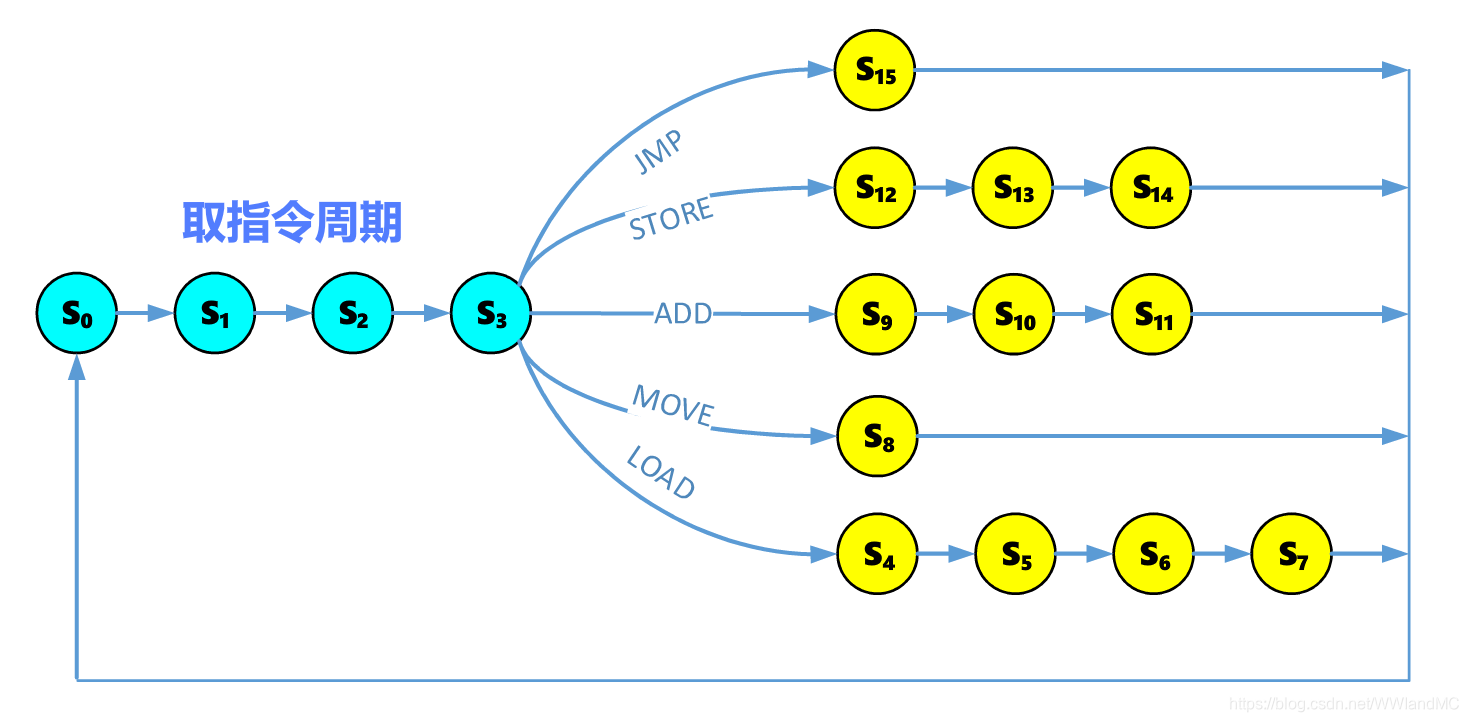

构建状态机:

状态的切换只和时钟有关。

执行周期结束后进入取指周期,S7的下一个状态是S0。

可以用状态寄存器(三位的计数器)描述,7+1溢出变回0

| 状态机的输入 |

|---|

| 时钟 |

时序产生器的作用就是循环产生周期电位、节拍电位,供控制器对信号进行时间调制。

Cn = ∑( Im & Mi & Tk & Bj)

| 优点 | 缺点 |

|---|---|

| 设计简单 | 以执行时间最长的指令进行同步,执行耗时短的指令时浪费了若干个节拍 |

| 通过周期电位和节拍电位和对应的指令译码信号进行与操作,能精准地控制信号产生的时间及其持续时间 |

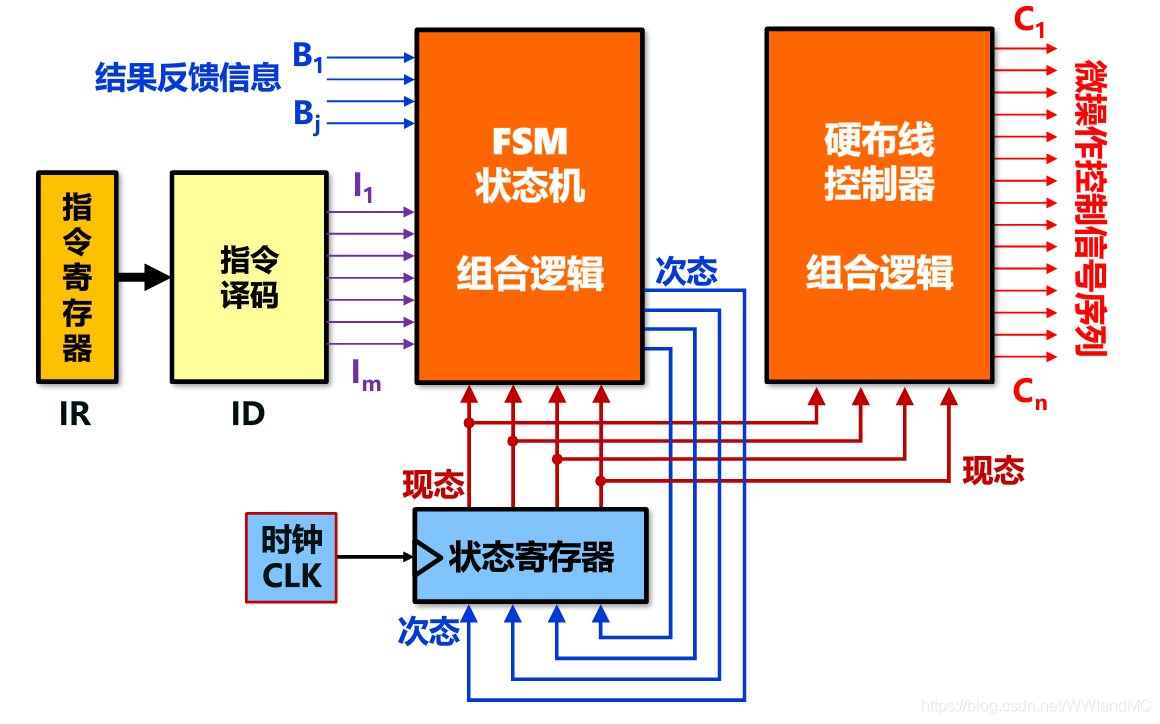

现代时序系统:变长指令周期

将所有指令在执行的不同阶段都用一个状态唯一的标识。

最终的控制信号只和状态机的现态有关。

时钟作为状态寄存器(4位计数器)的输入

| 状态机的输入 |

|---|

| 现态 |

| 指令译码信号 |

| 程序运行的结果特征和状态(反馈信号) |

状态机对现态进行加工生成次态,次态作为输入送到状态寄存器,时钟输入一次,次态就会变成现态。Cn是现态的函数。

| 优点 |

|---|

| 按照时钟脉冲进行同步,需要多少给多少 |

单总线架构CPU指令周期的数据流

LOAD R0,6#

MOV R1,10

ADD R0,R1

假设READ信号需要持续两个节拍

取指周期数据流:

- 给出PCout、ARin、Xin信号,PC内容送到AR和X

- 给出ALU的运算选择信号+1,PC值+1输出,在第二个时钟上跳沿到来时结果锁存在Z;给出READ信号,开始读主存操作

- 继续给出READ信号。给出Zout、PCin信号,将Z的值送到PC;给出DREin信号,存储器中的指令写入DR

- 给出DRout、IRin,将DR的内容写入IR,送到ID,生成操作控制信号

LOAD数据流:

- 给出IRout,ARin,寄存在IR中的地址码部分6送到AR

- 给出READ信号

- 继续给出READ信号。给出DREin,AR对应的存储单元的数据传送到DR

- 给出DRout、R0in,数据传递到总线送入到R0的输入端

MOV R1,10数据流:

- 给出IRout、R1in,指令中的地址码中的立即数写入R1

ADD数据流:

- 给出R0、Xin,R0中的值送入X

- 给出R1out信号,R1的内容通过总线传送到ALU的B端;给出ADD,运算结果在第二个时钟上跳沿到来时锁存在Z中

- 给出R0in、Zout,将结果写入R0

浙公网安备 33010602011771号

浙公网安备 33010602011771号