FPGA

2016-09-14 00:22 LUCKMONKEY00 阅读(197) 评论(0) 收藏 举报基于FPGA的等精度测频方法

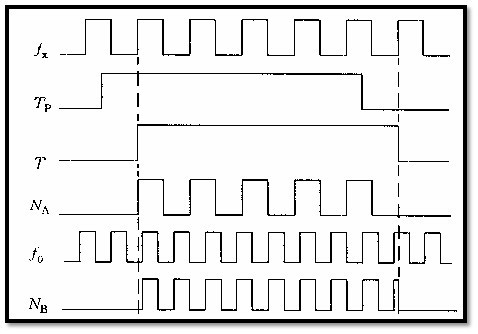

1、多周期等精度测频的时序 ![]() 预置闸门时间产生电路产生预置闸门时间TP,TP经同步电路产生与被测信号(fx)同步的实际闸门时间T。

预置闸门时间产生电路产生预置闸门时间TP,TP经同步电路产生与被测信号(fx)同步的实际闸门时间T。

主门Ⅰ与主门Ⅱ在时间T内被同时打开,计数器Ⅰ和Ⅱ分别对 fx和 f0 进行计数。

2、实现

1. 闸门信号与被测信号同步

2. 在闸门信号与被测信号的同步下降沿锁存计数值

3、Verilog硬件描述语言

/*

/*  * Copyright (C) 2009, Electric & Electronic Innovation Center of Sci. & Tech. HUST

* Copyright (C) 2009, Electric & Electronic Innovation Center of Sci. & Tech. HUST  * All Rights Reserved.

* All Rights Reserved.  *

*  * File name: mesureFreq.v

* File name: mesureFreq.v  * File description: Measure the frequency

* File description: Measure the frequency  * Operating environment: QUARTUS II 8.1,cyclone II EP2C8Q208C8N

* Operating environment: QUARTUS II 8.1,cyclone II EP2C8Q208C8N  *

*  * This version: 1.0

* This version: 1.0  * Author: lwpo2008(lwpo2008@yahoo.com.cn)

* Author: lwpo2008(lwpo2008@yahoo.com.cn)  * Previous Author: none

* Previous Author: none  * Complete date: 2009-08-20

* Complete date: 2009-08-20  *

*  */

*/  module mesureFreq (

module mesureFreq (  input fx,

input fx,  input fbase,

input fbase,  input fgate,

input fgate,  output reg[31:0] fxCnt,

output reg[31:0] fxCnt,  output reg[31:0] fbaseCnt

output reg[31:0] fbaseCnt  );

);

reg startCnt;

reg startCnt;  reg[31:0] fxCntTemp,fbaseCntTemp;

reg[31:0] fxCntTemp,fbaseCntTemp;

always @ (posedge fbase) begin

always @ (posedge fbase) begin  if(startCnt)

if(startCnt)  fbaseCntTemp <= fbaseCntTemp + 1;

fbaseCntTemp <= fbaseCntTemp + 1;  else

else  fbaseCntTemp <= 32'h00000000;

fbaseCntTemp <= 32'h00000000;  end

end

always @ (posedge fx) begin

always @ (posedge fx) begin  if(startCnt)

if(startCnt)  fxCntTemp <= fxCntTemp + 1;

fxCntTemp <= fxCntTemp + 1;  else

else  fxCntTemp <= 32'h00000000;

fxCntTemp <= 32'h00000000;  end

end

//synchronous fgate

//synchronous fgate  always @ (posedge fx) begin

always @ (posedge fx) begin  if(fgate)

if(fgate)  startCnt <= 1'b1;

startCnt <= 1'b1;  else

else  startCnt <= 1'b0;

startCnt <= 1'b0;  end

end

//output

//output  always @ (negedge startCnt) begin

always @ (negedge startCnt) begin  fxCnt <= fxCntTemp;

fxCnt <= fxCntTemp;  fbaseCnt <= fbaseCntTemp;

fbaseCnt <= fbaseCntTemp;  end

end

endmodule

endmodule

预置闸门时间产生电路产生预置闸门时间TP,TP经同步电路产生与被测信号(fx)同步的实际闸门时间T。

预置闸门时间产生电路产生预置闸门时间TP,TP经同步电路产生与被测信号(fx)同步的实际闸门时间T。

工程文件:

工程文件:

浙公网安备 33010602011771号

浙公网安备 33010602011771号