[408][自用] 计算机组成原理知识点串接

2️⃣: 数据的表示与运算

数制与编码

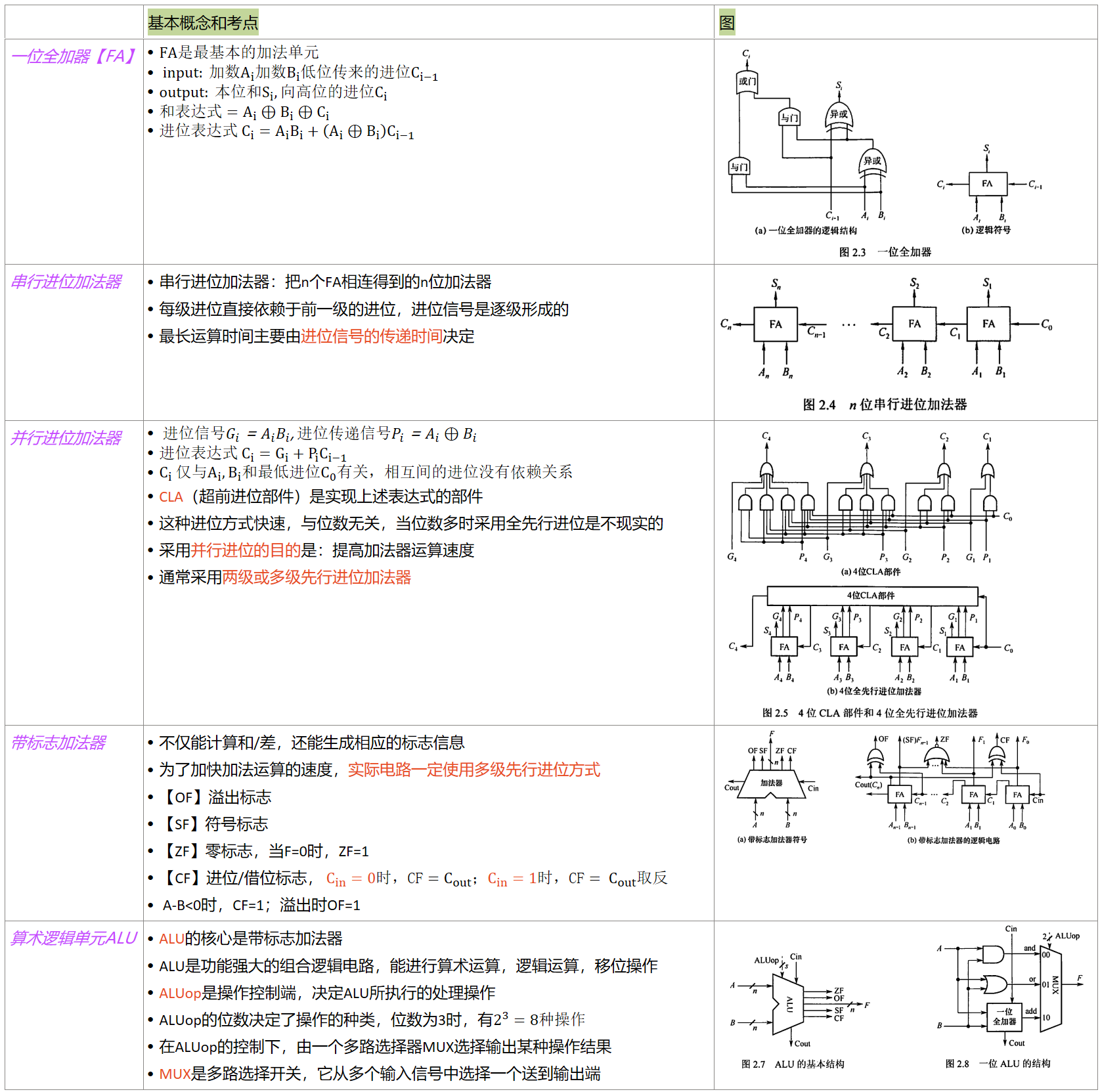

运算方法与运算电路

基本运算部件

定点数

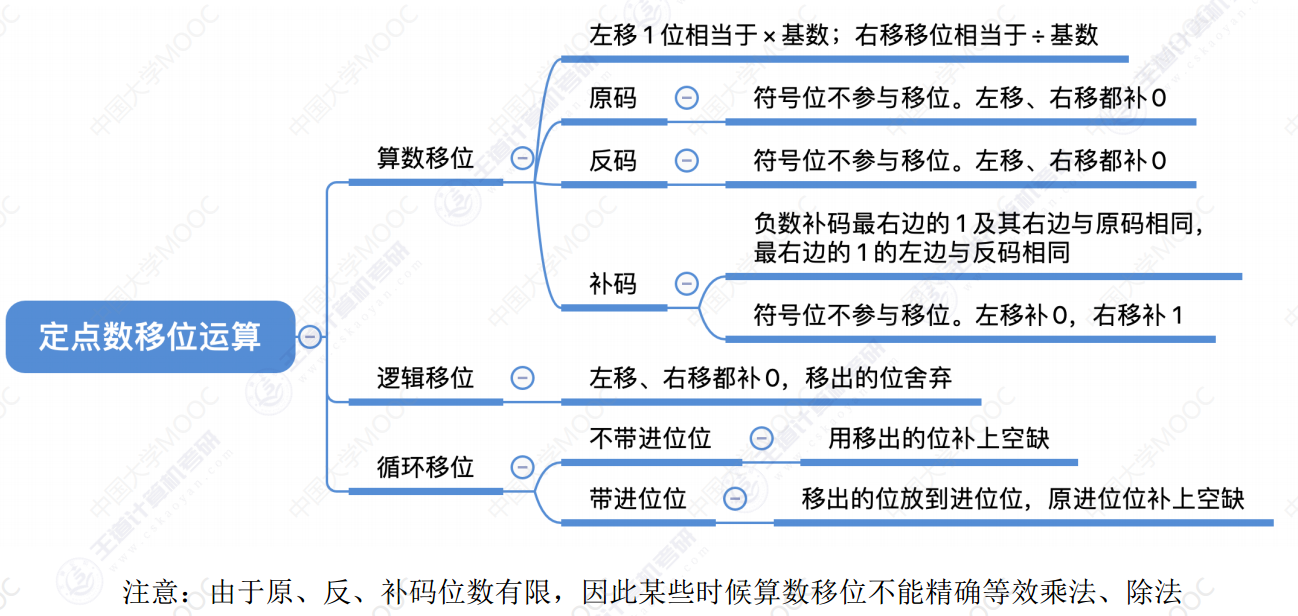

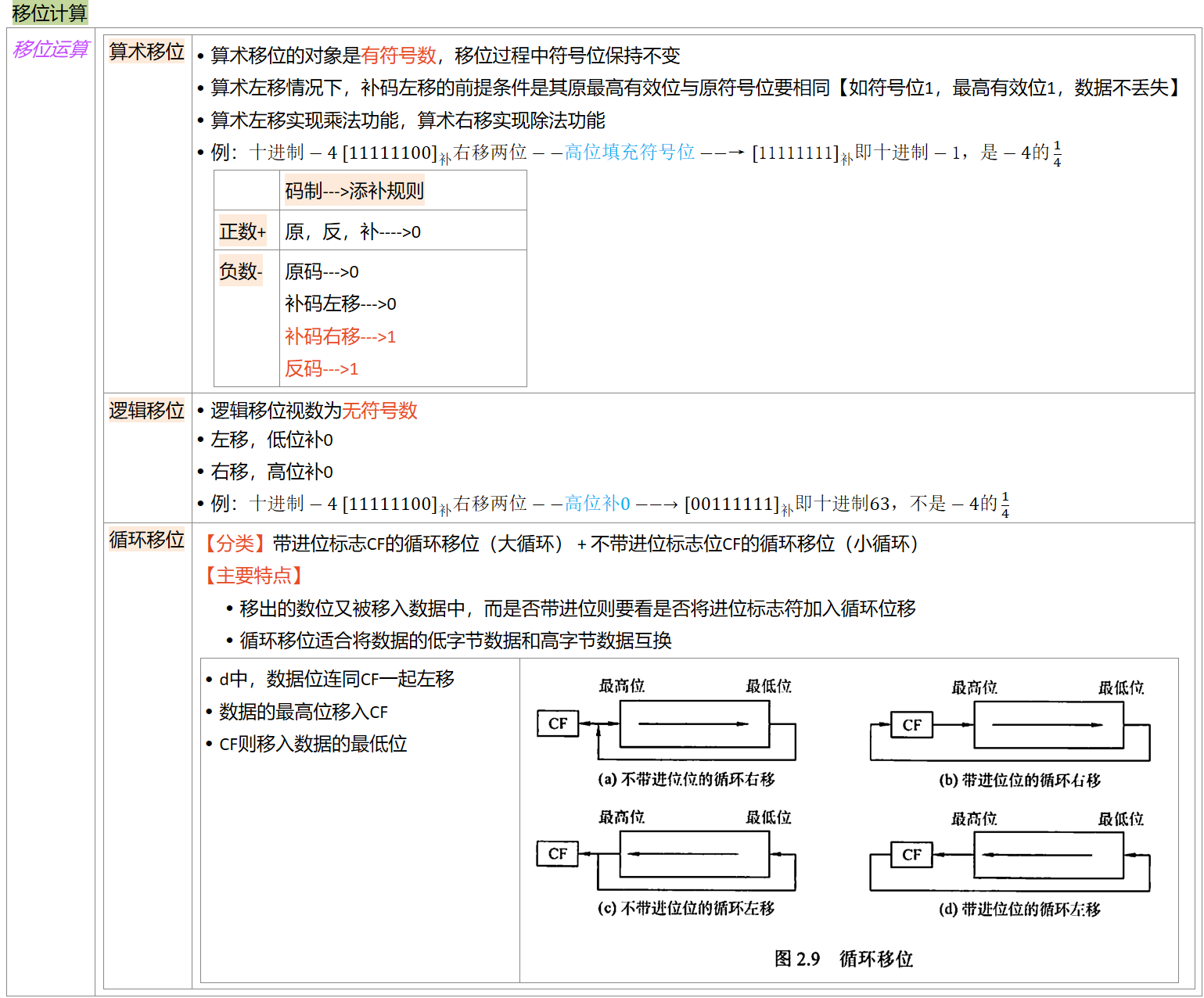

定点数的移位运算

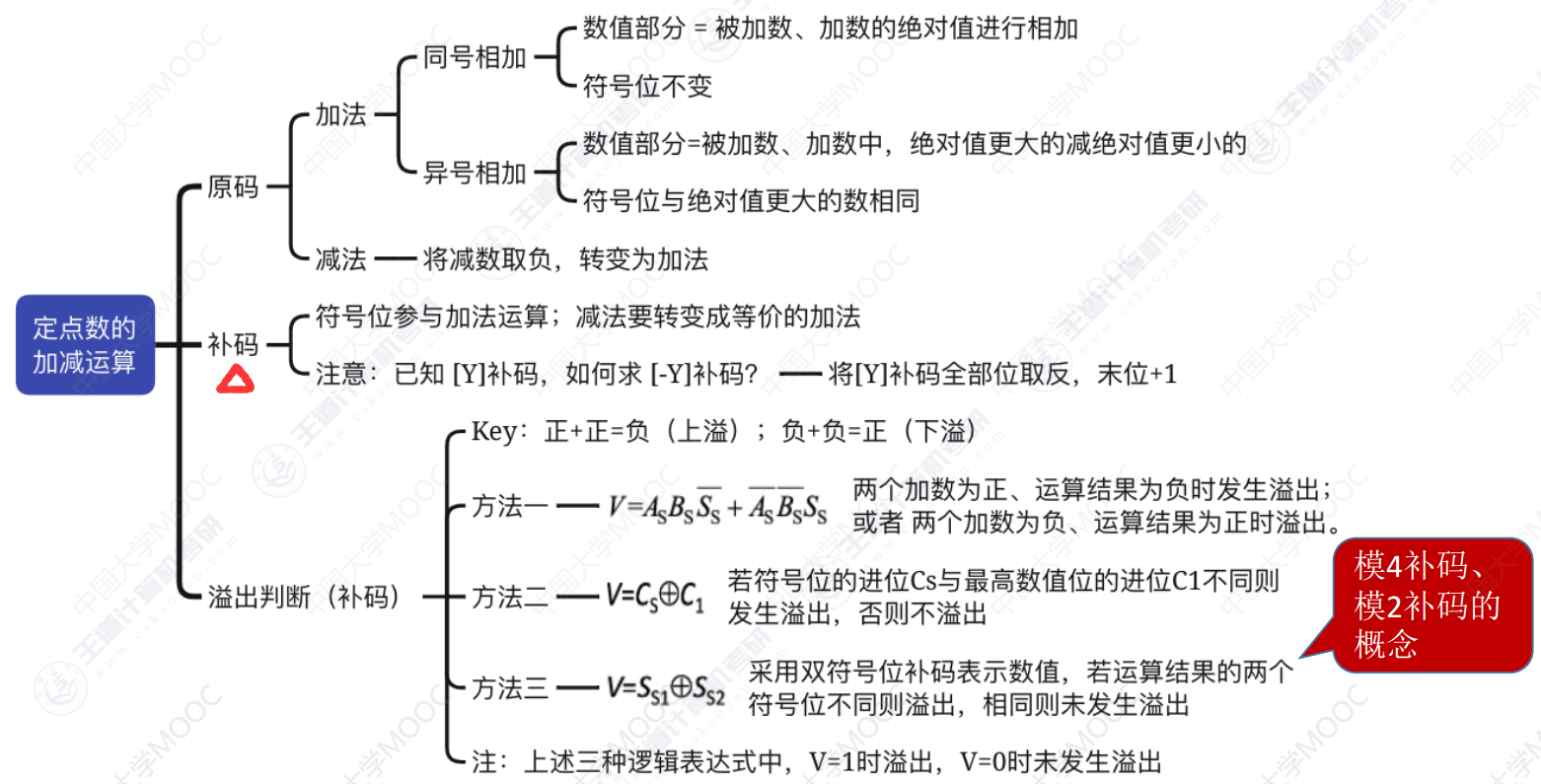

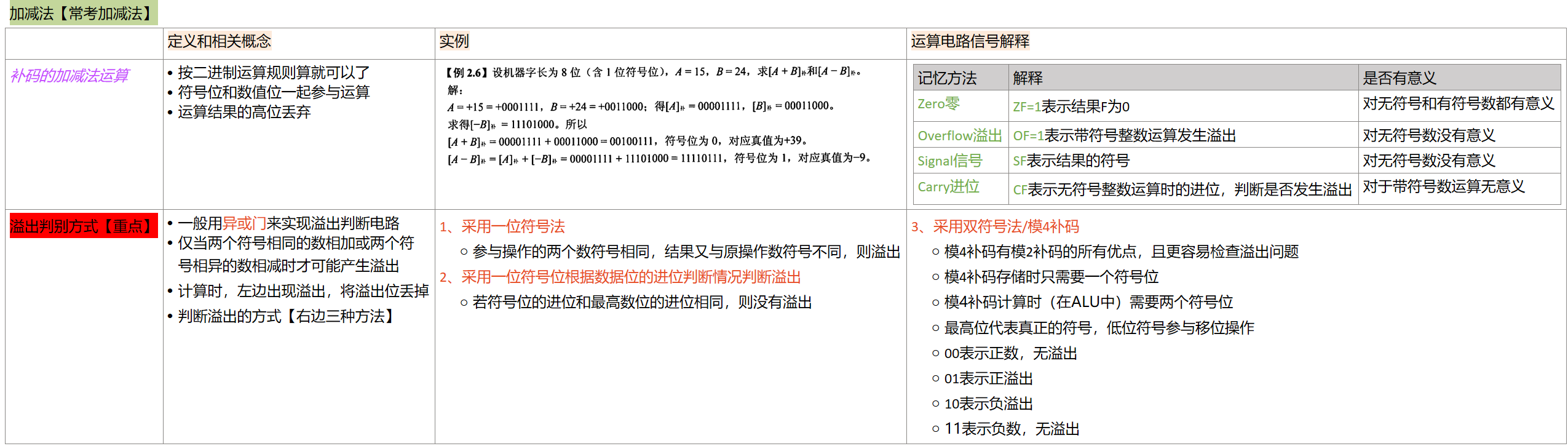

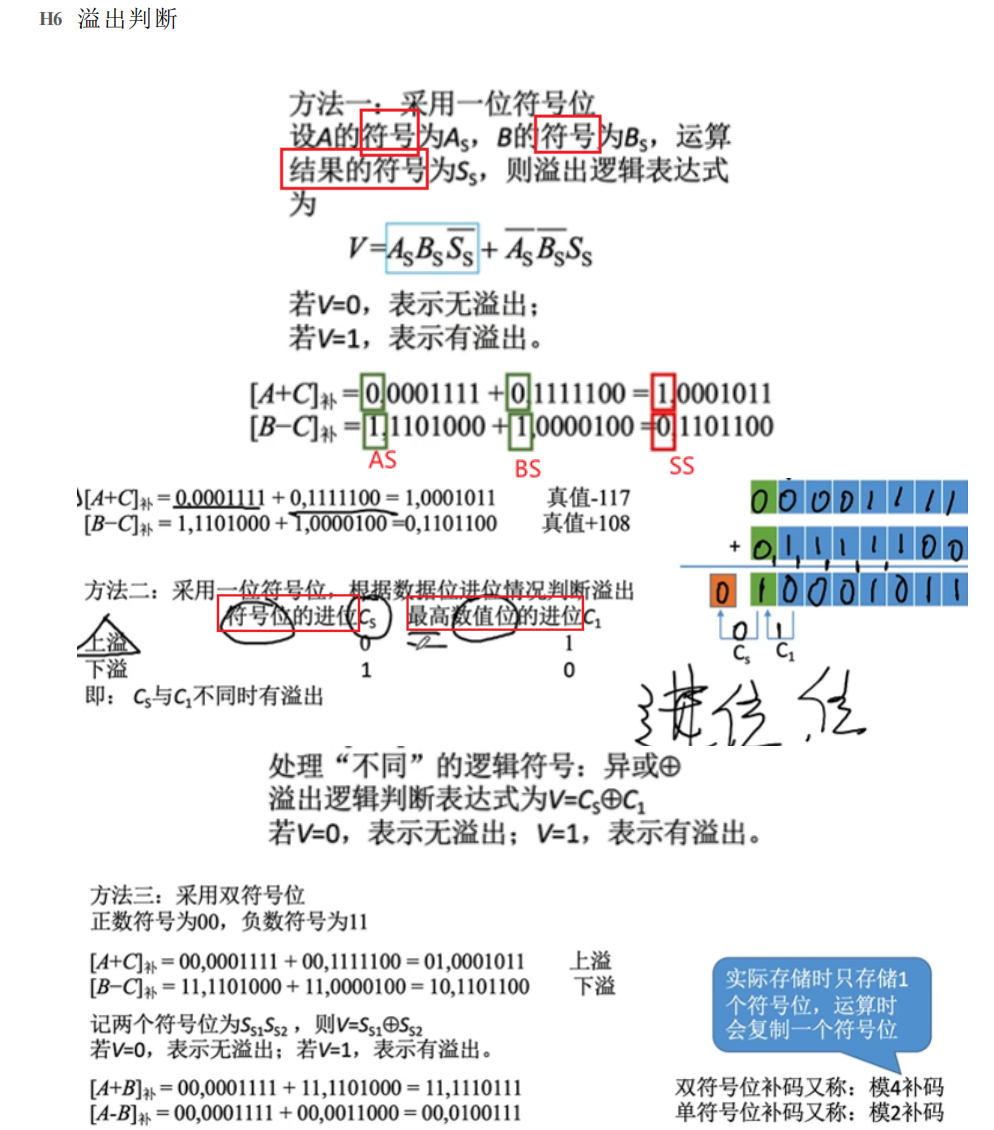

定点数的加减运算与溢出判断

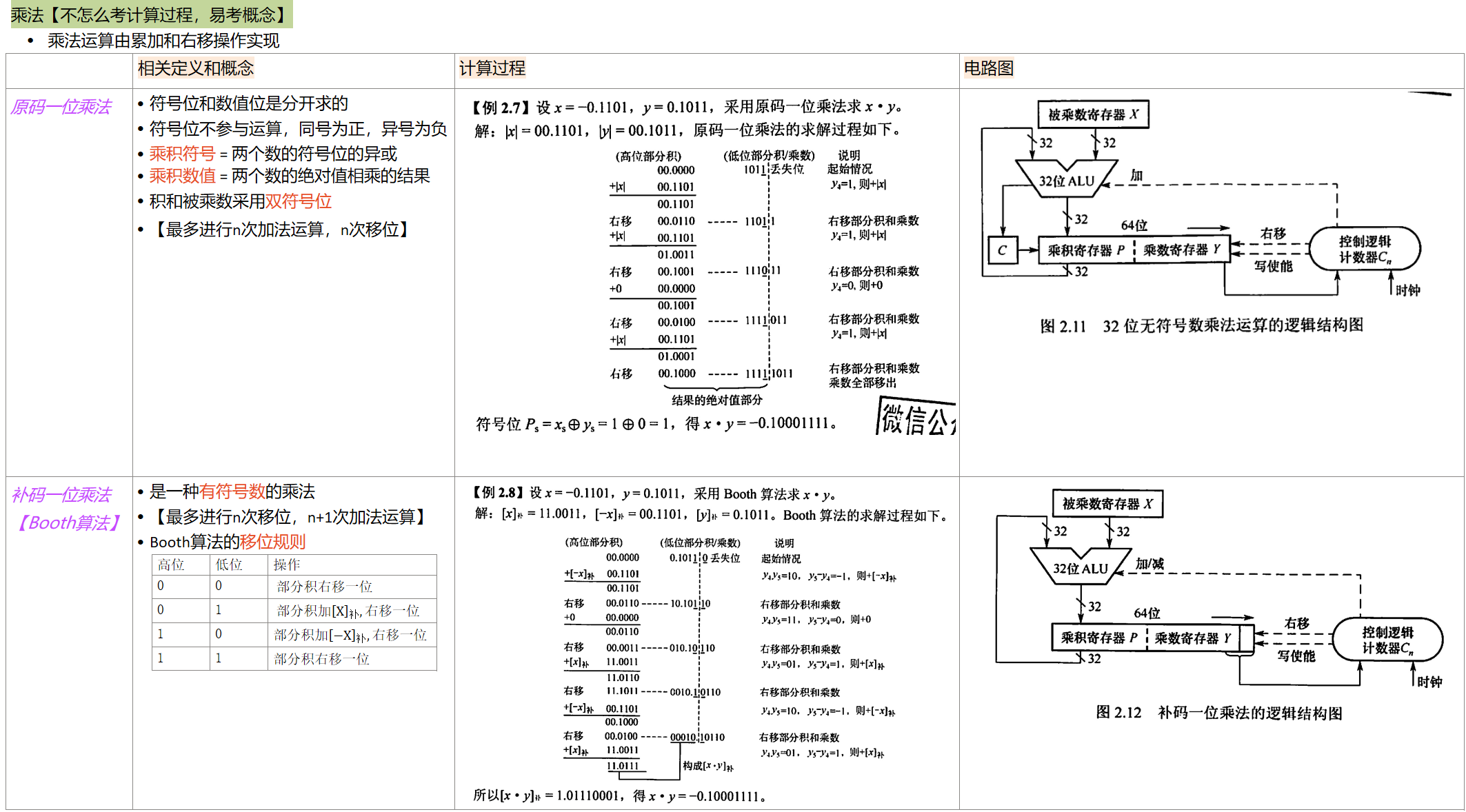

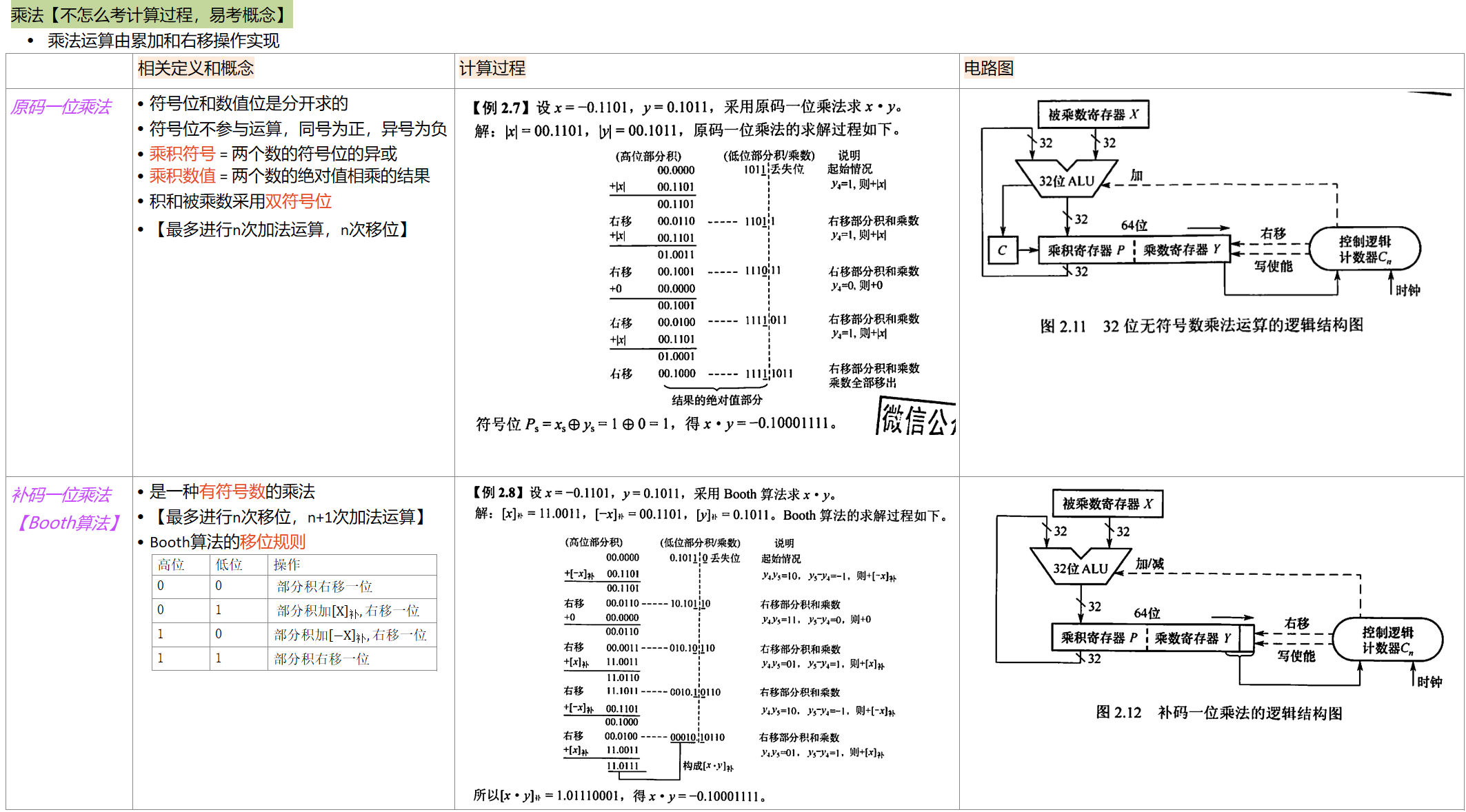

定点数的乘法运算

原码一位乘法

补码一位乘法

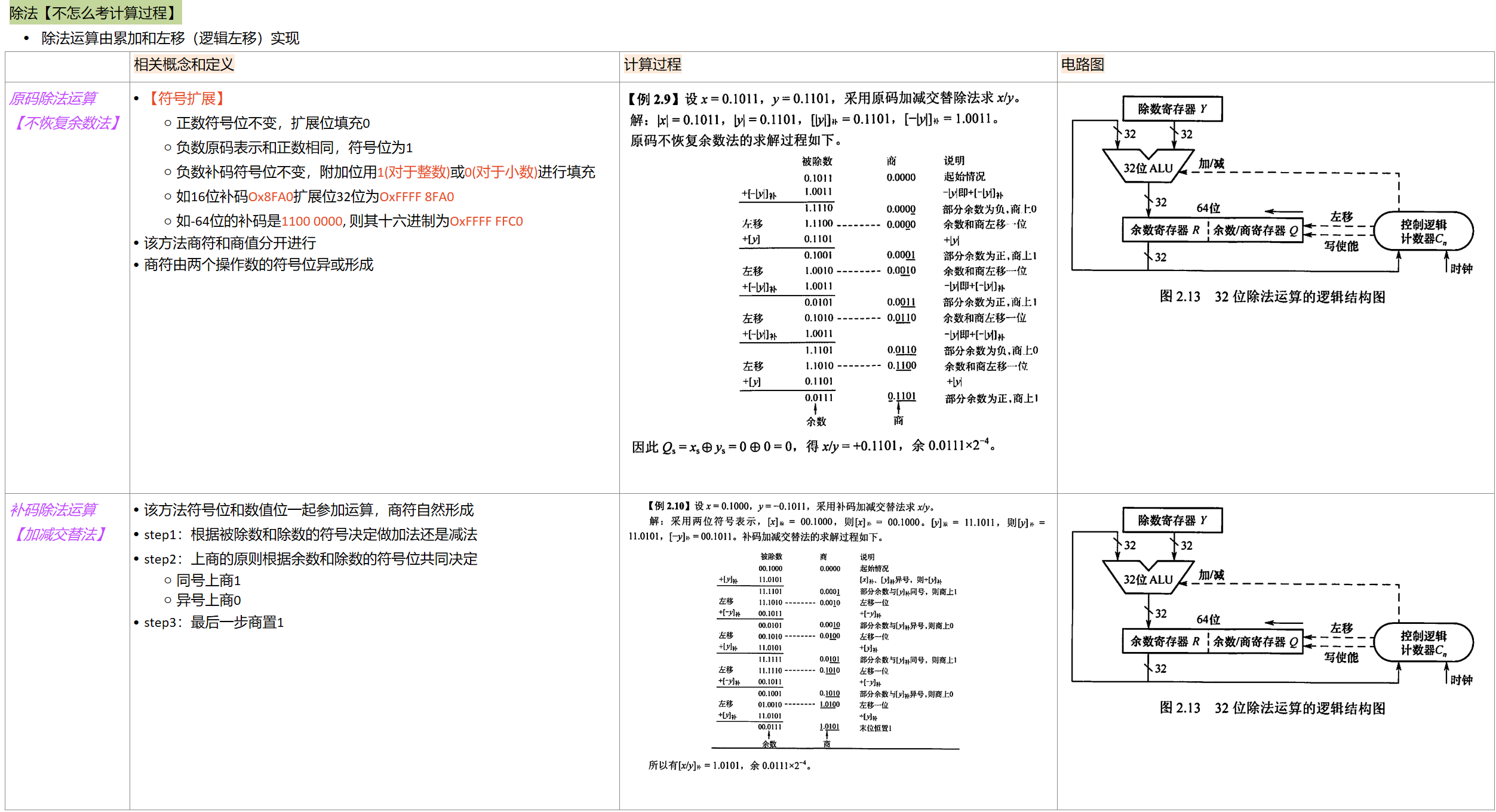

定点数的除法运算

原码除法:恢复余数法

原码除法:加减交替法(不恢复余数法)

补码除法:加减交替法

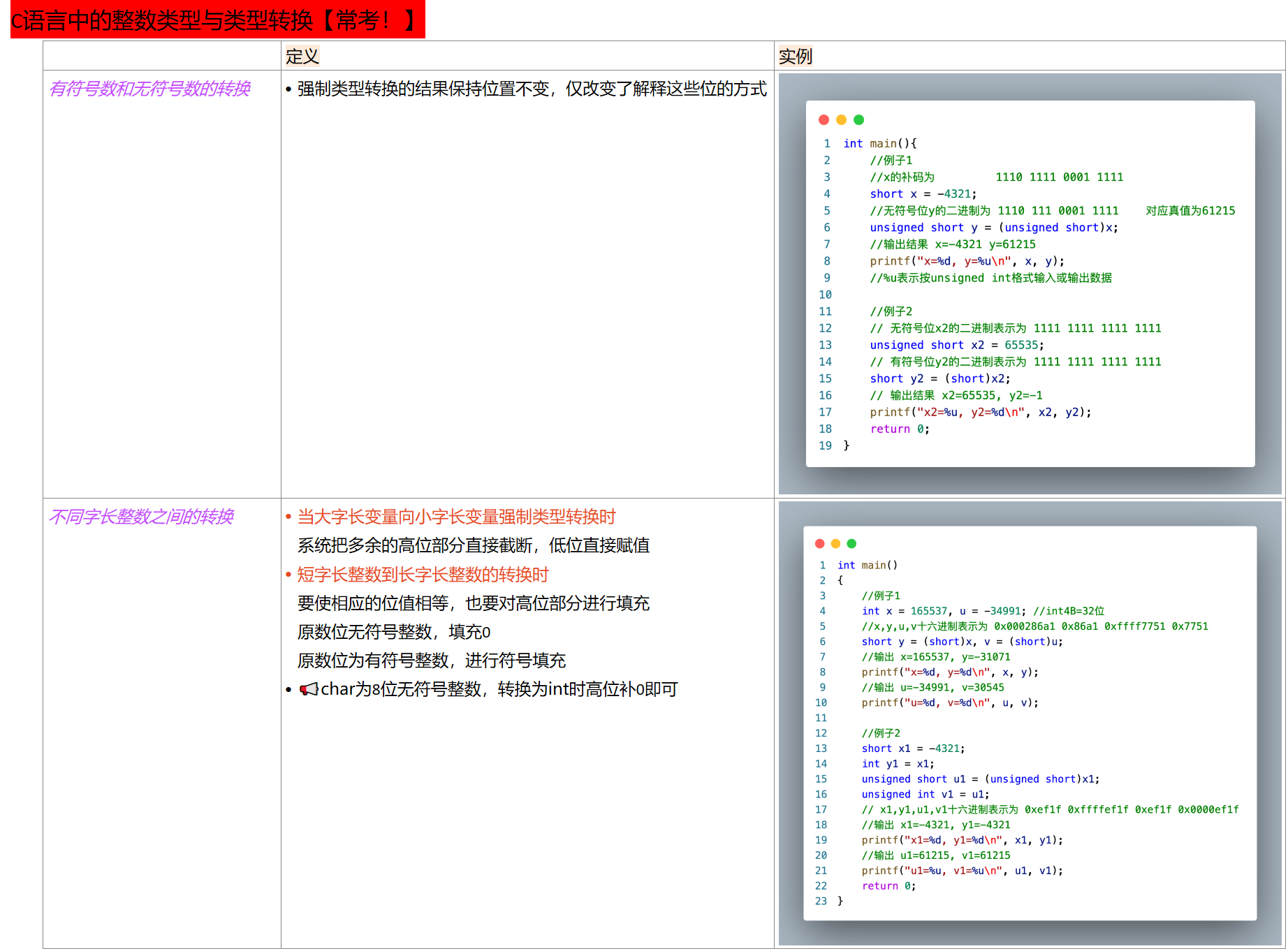

C语言中的整数类型与类型转换【常考!】

数据的存储与排列

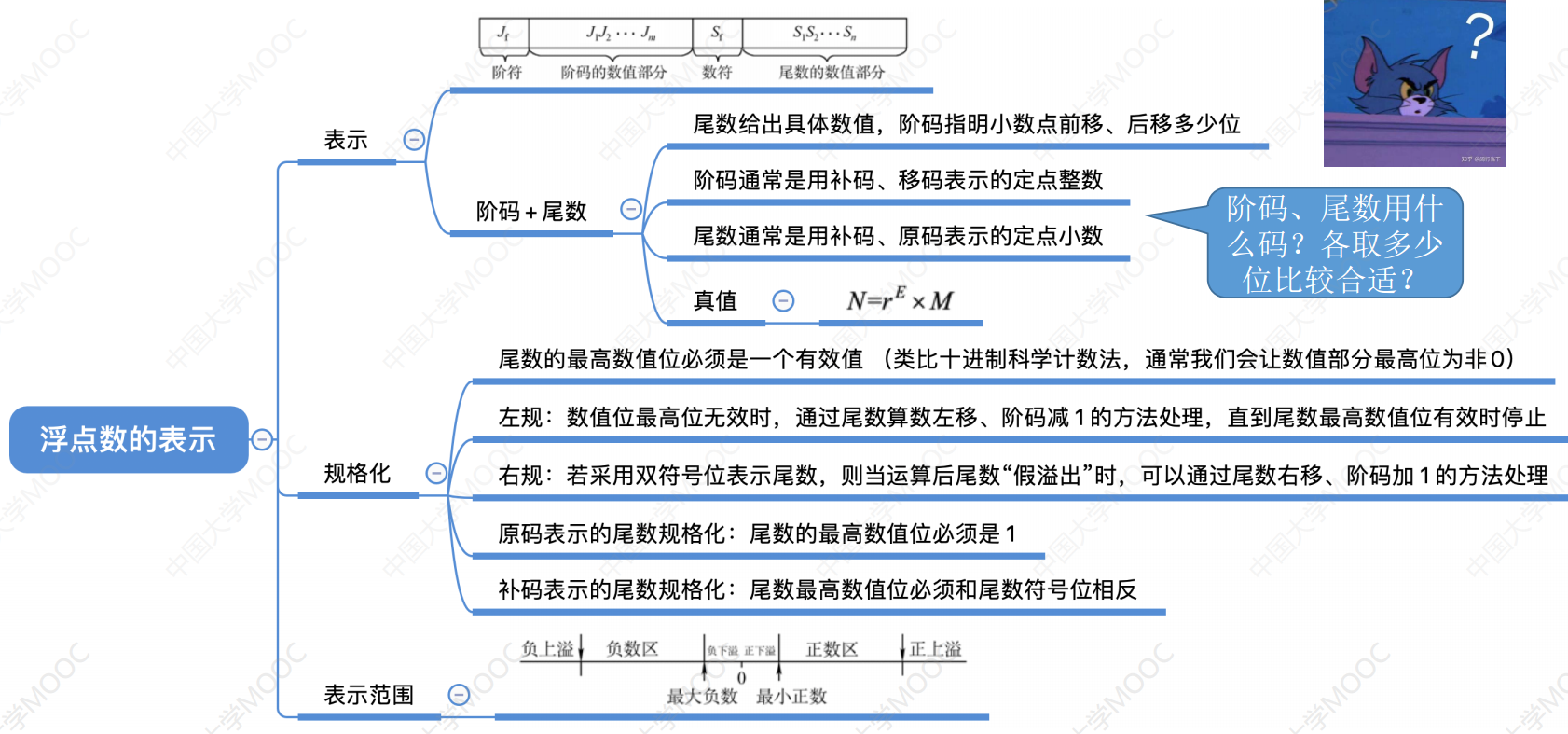

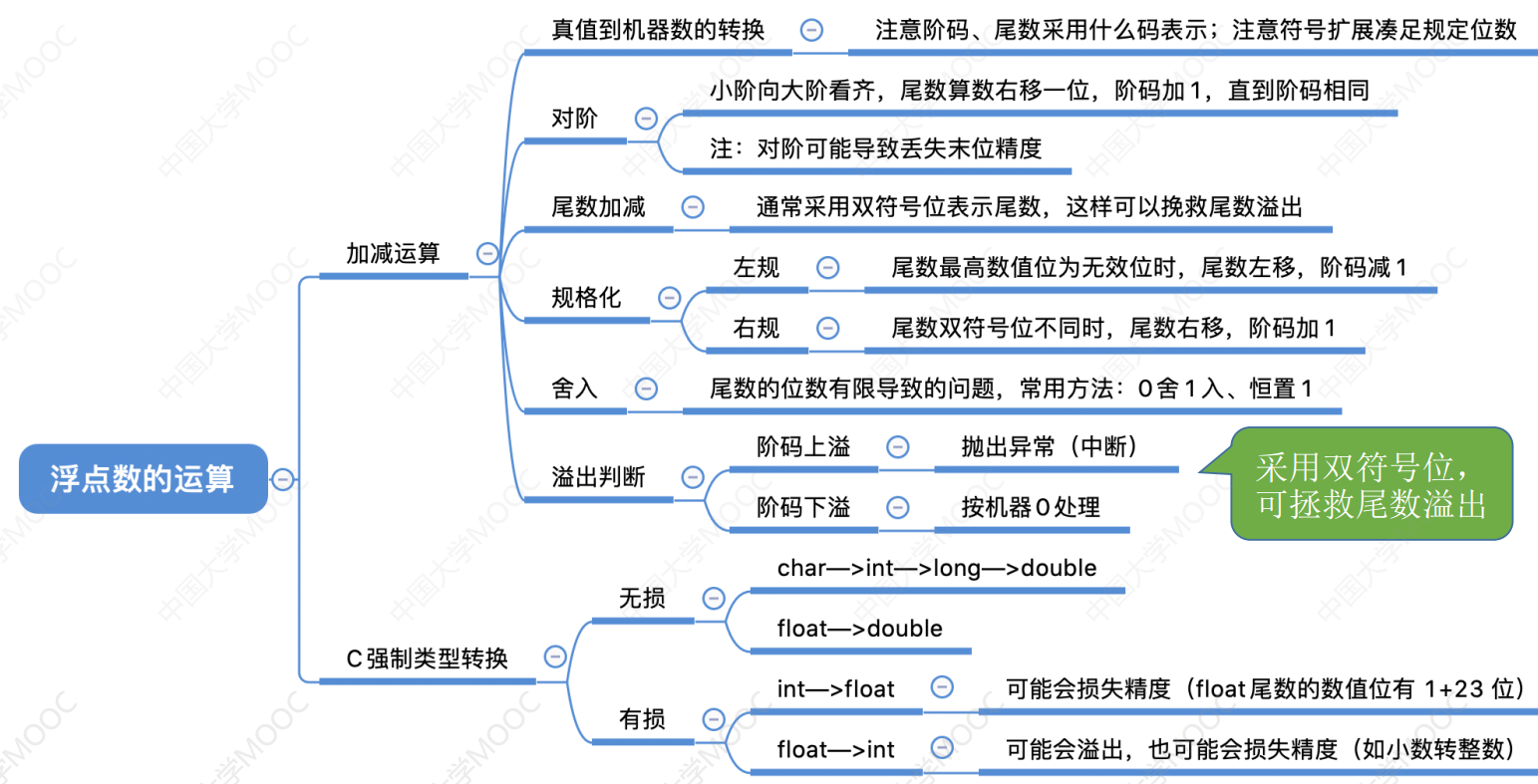

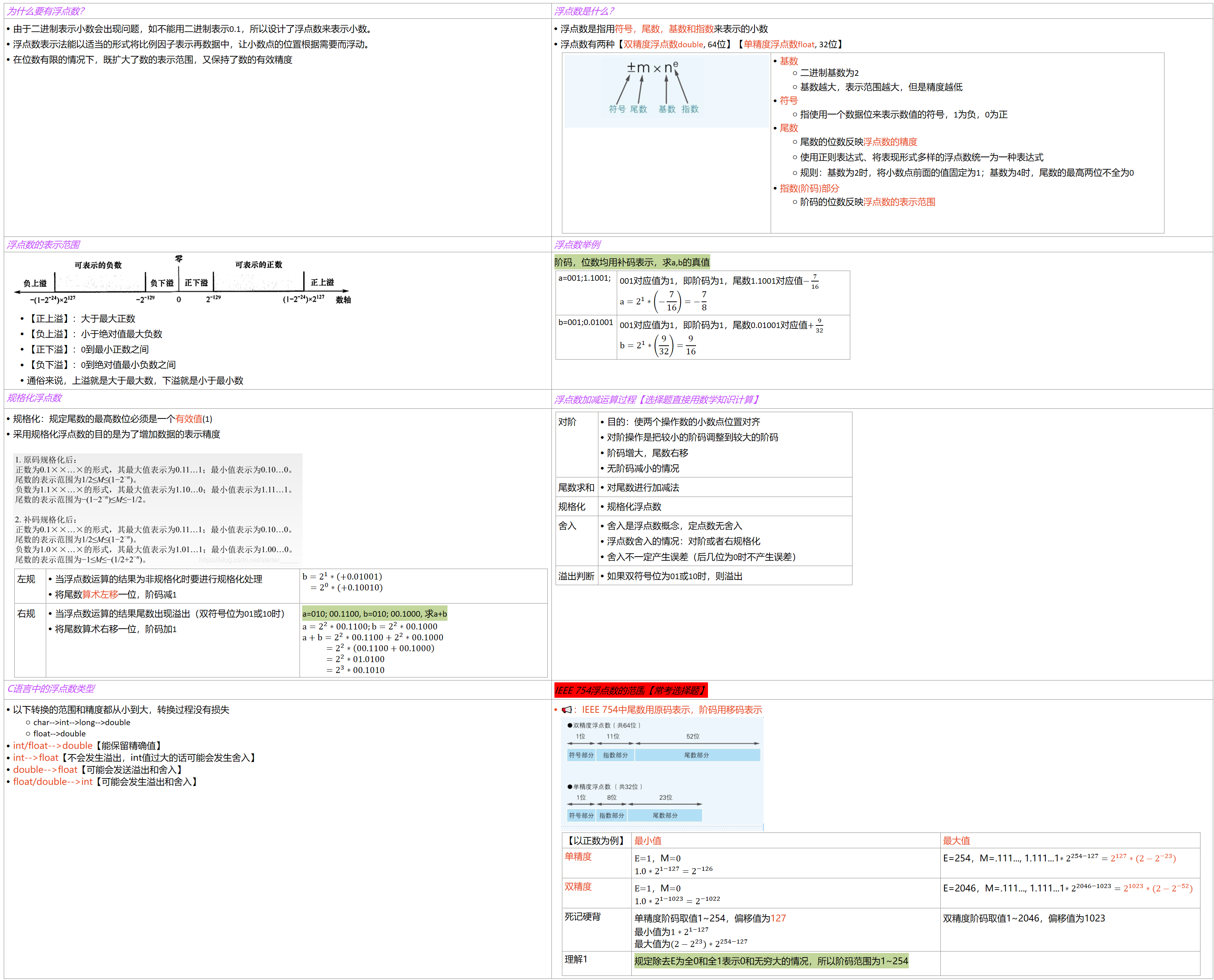

浮点数的表示与运算

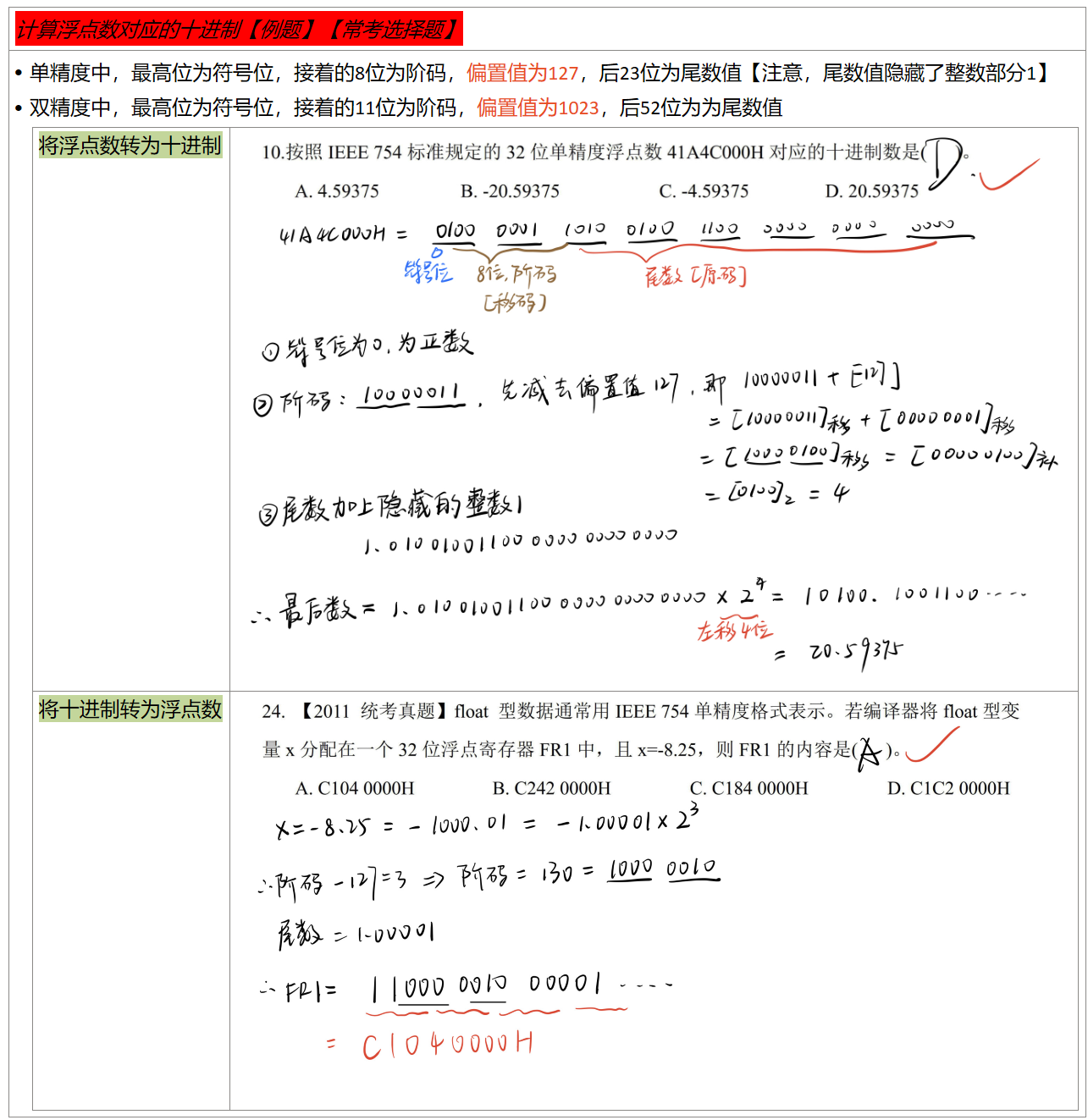

计算浮点数对应的十进制

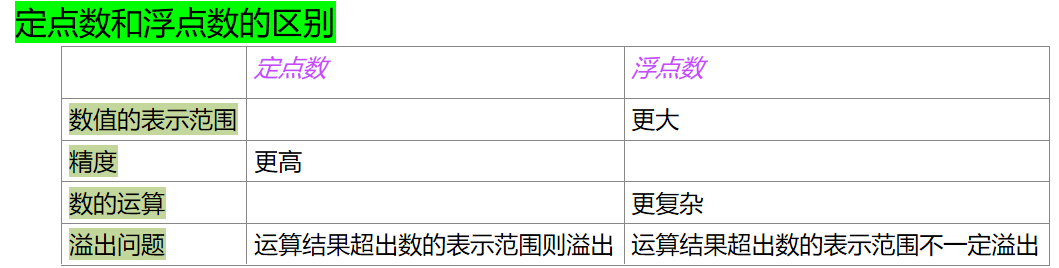

定点数vs浮点数

3️⃣: 存储系统

主存储器

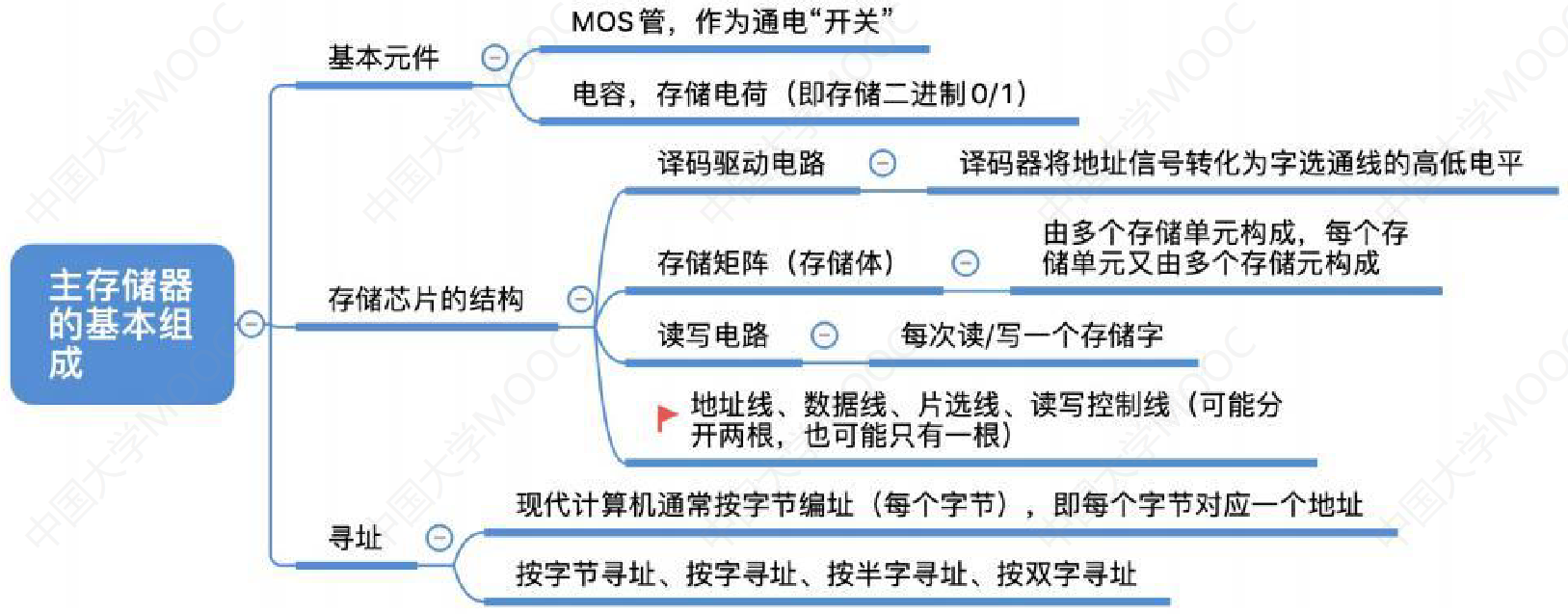

主存储器的基本组成

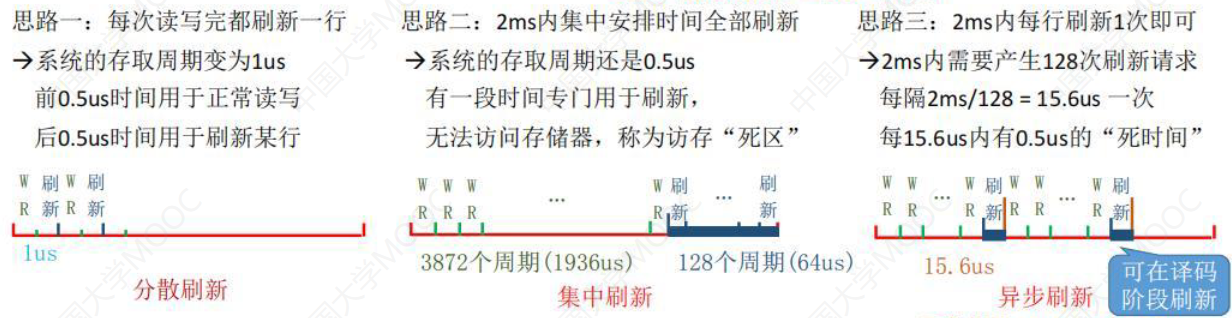

SRAM和DRAM

栅极电容与双稳态触发器

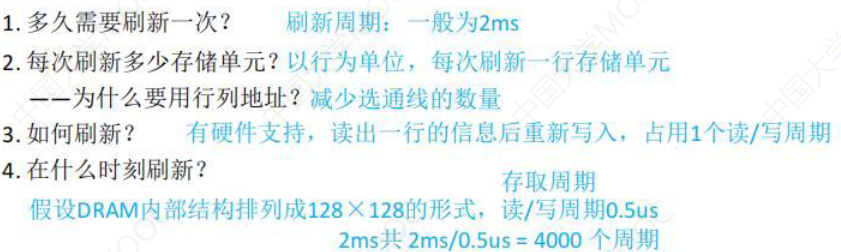

DRAM的刷新 分散/集中/异步

【计组】简单理解集中式刷新、分散式刷新、异步式刷新

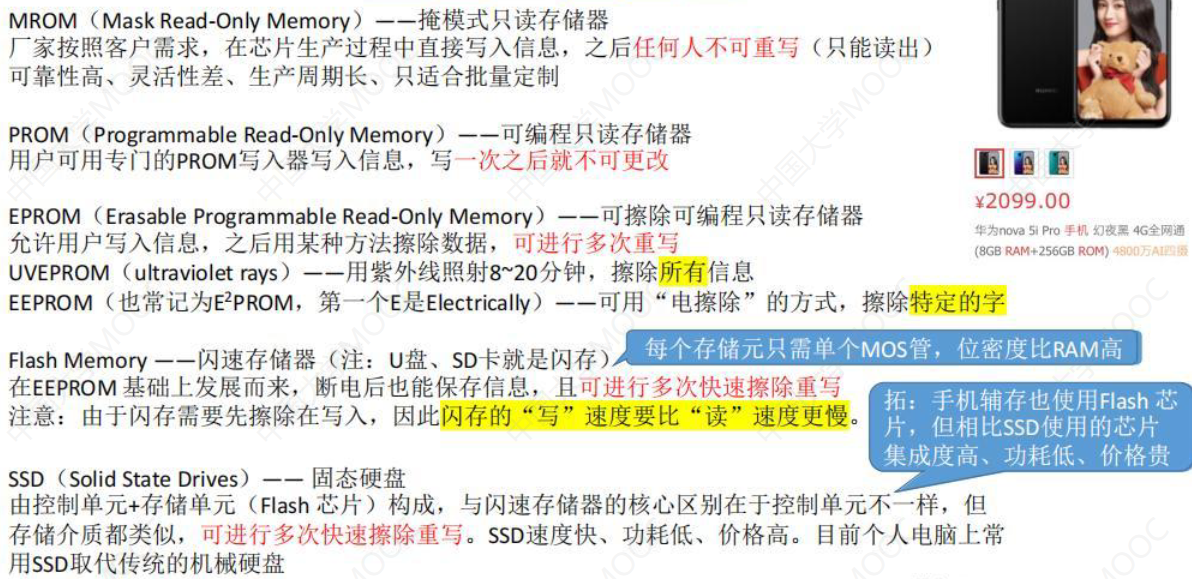

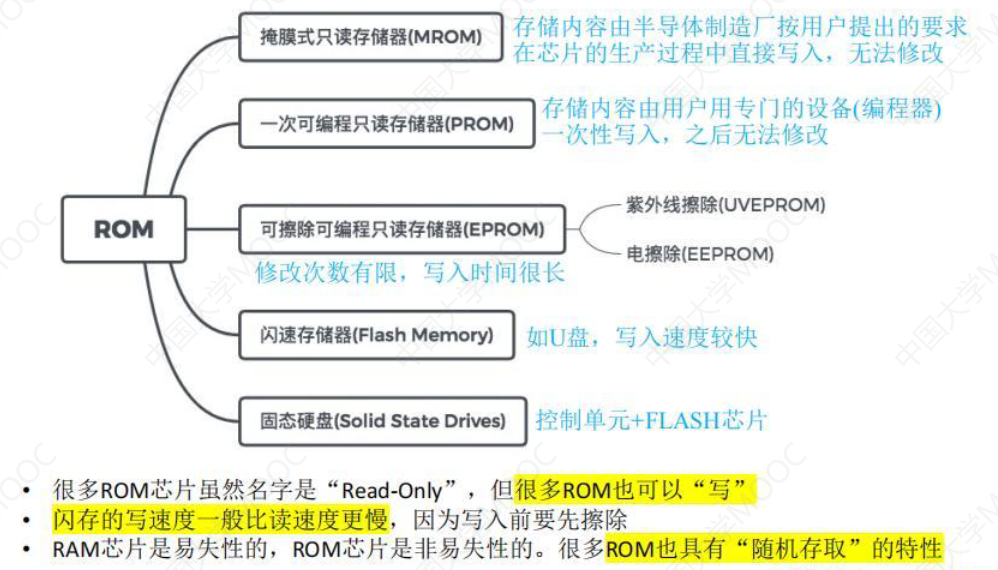

只读存储器ROM

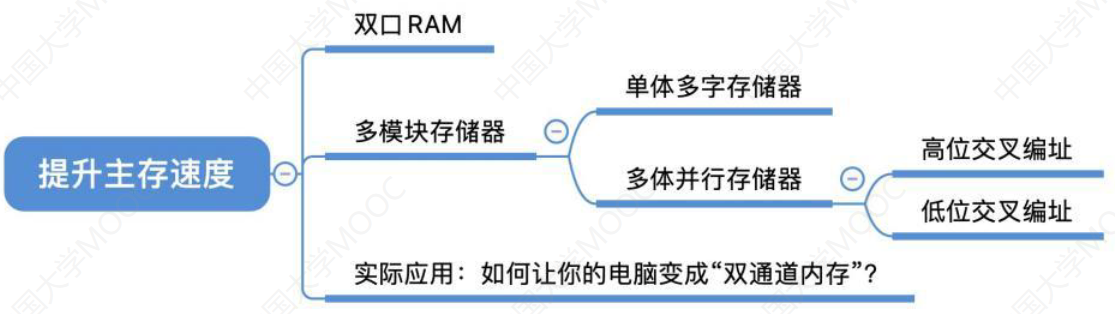

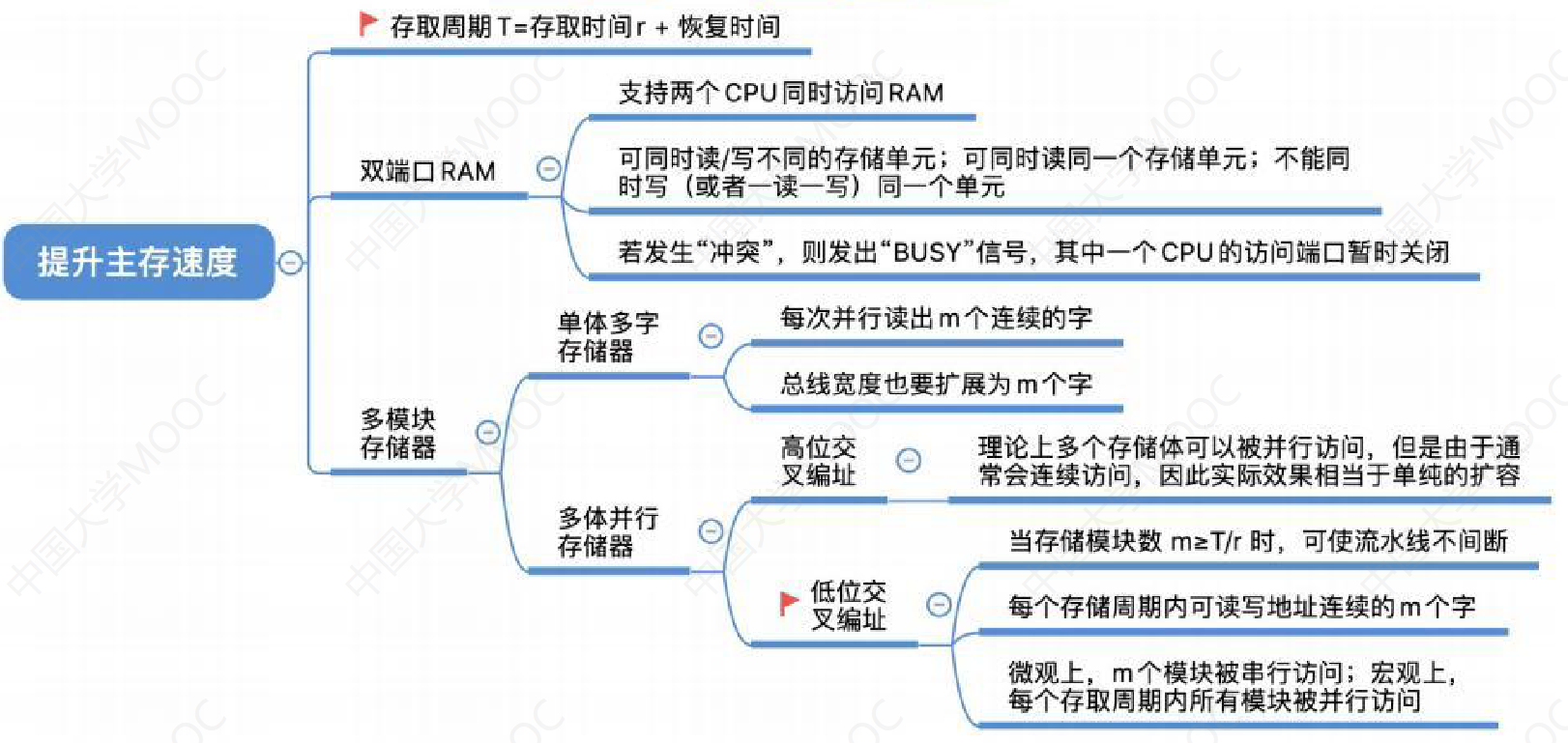

多模块存储器

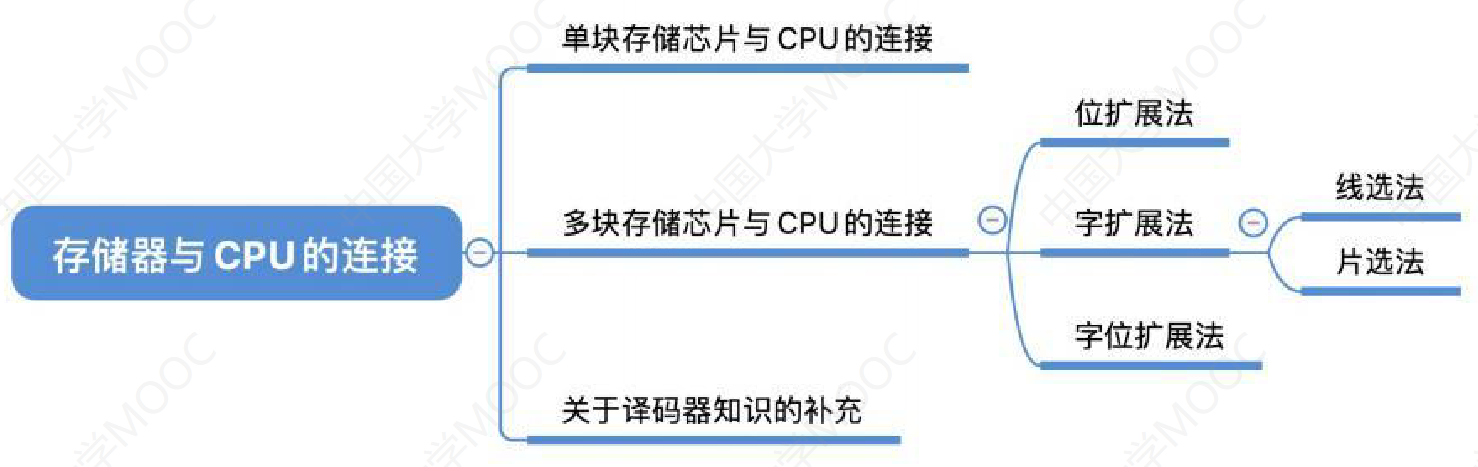

主存储器与CPU的连接

外部存储器

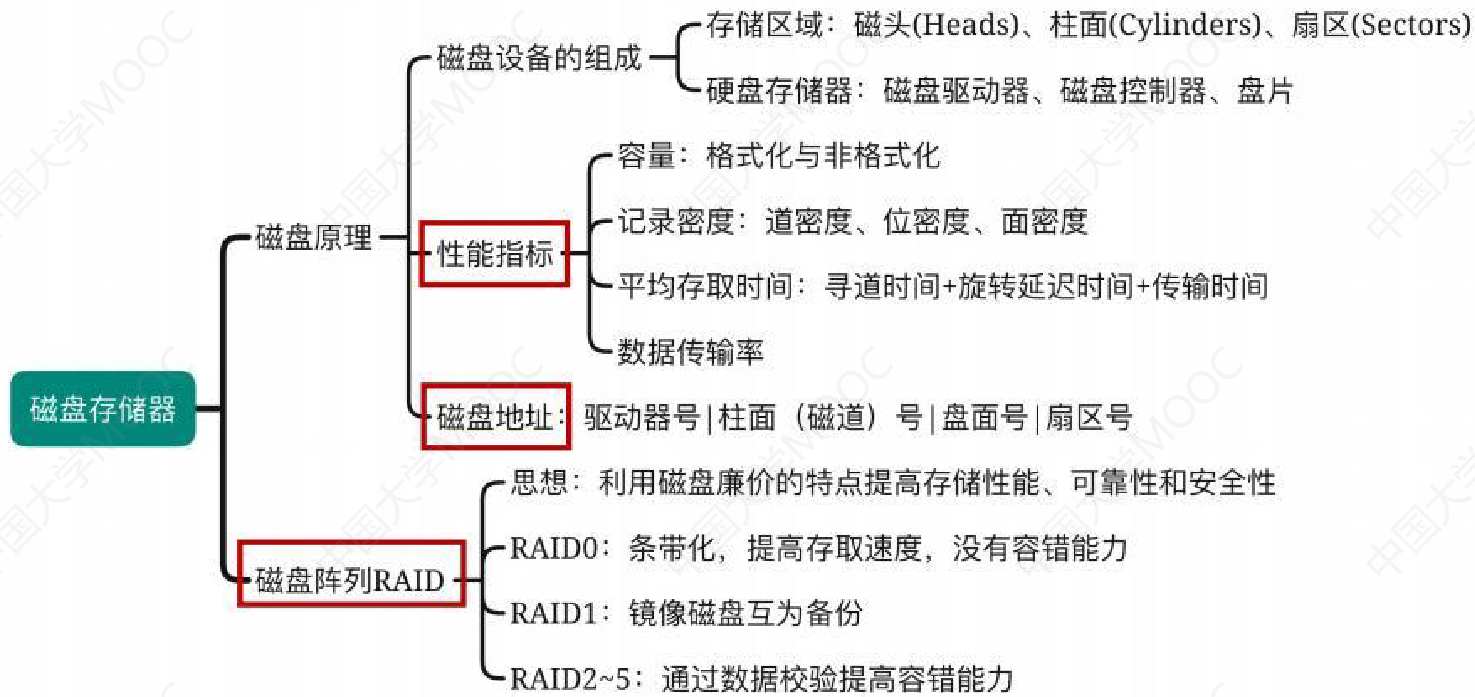

磁盘存储器

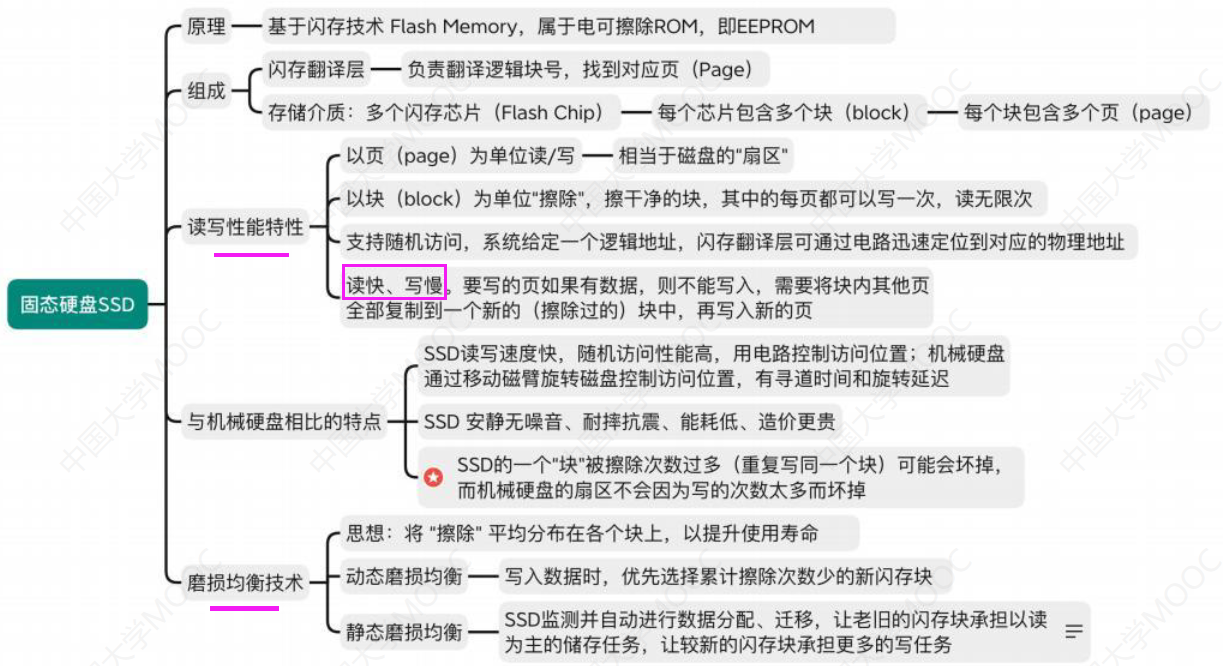

固态硬盘SSD

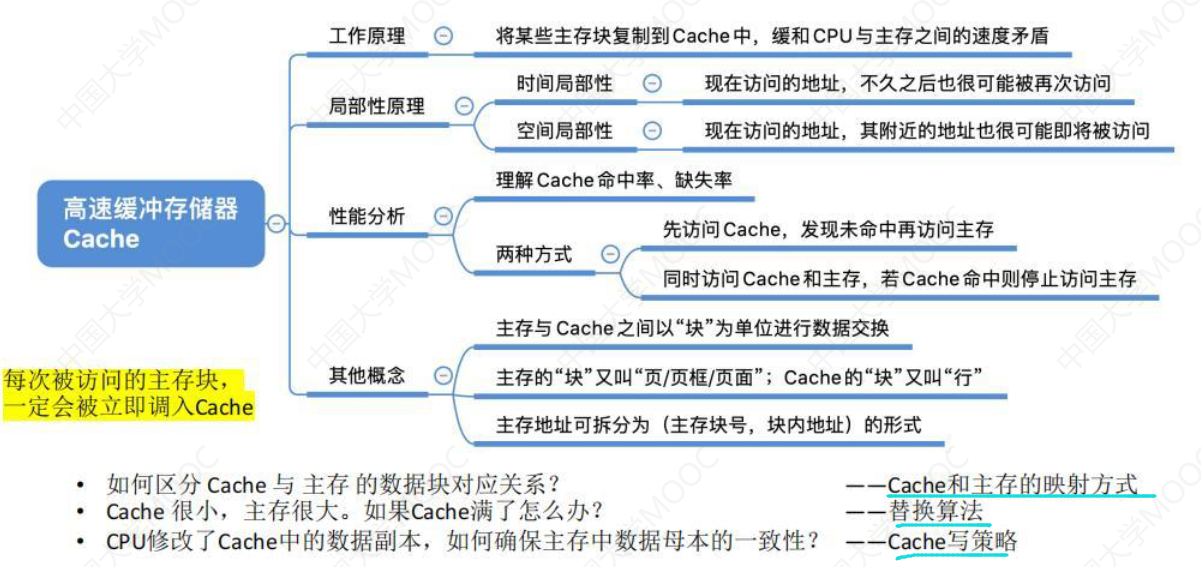

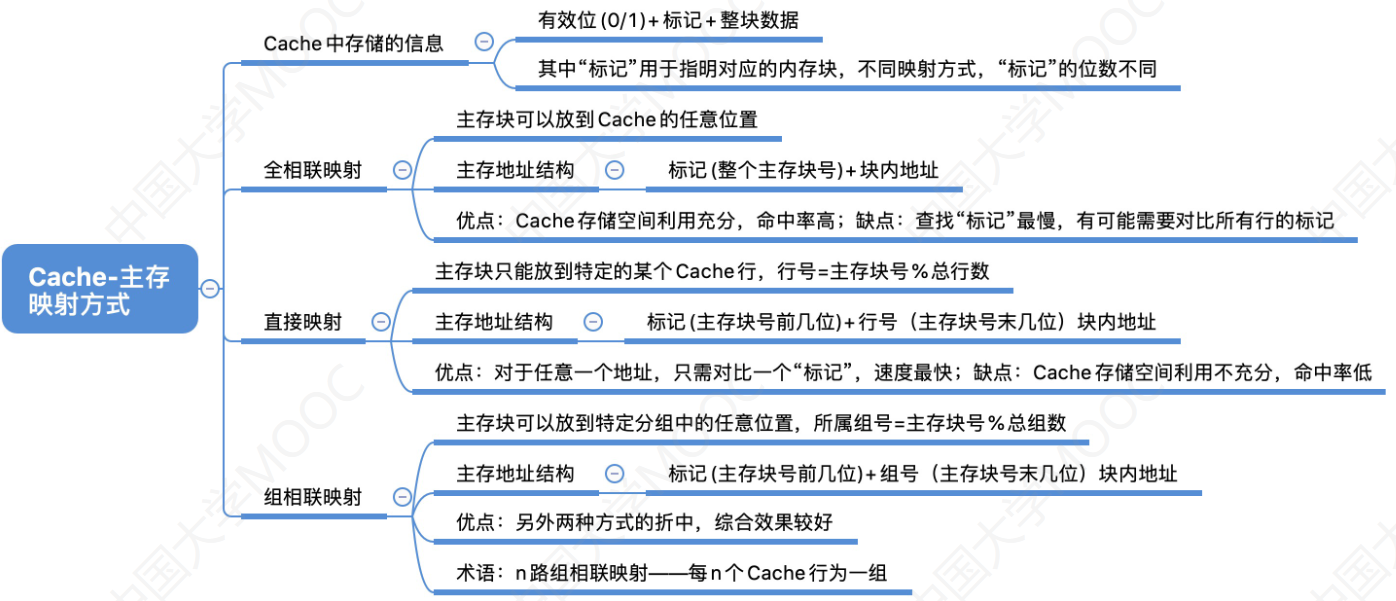

高速缓冲存储器

Cache 基本原理基本概念

Cache和主存的映射方式

Cache中主存块的替换算法

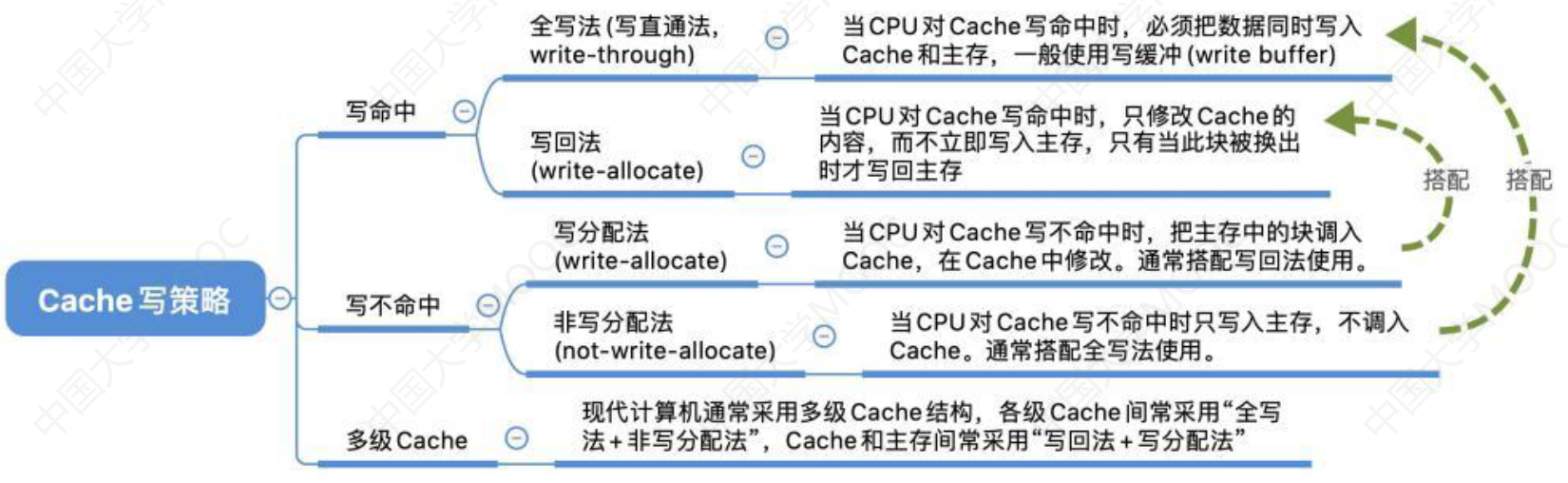

Cache写策略

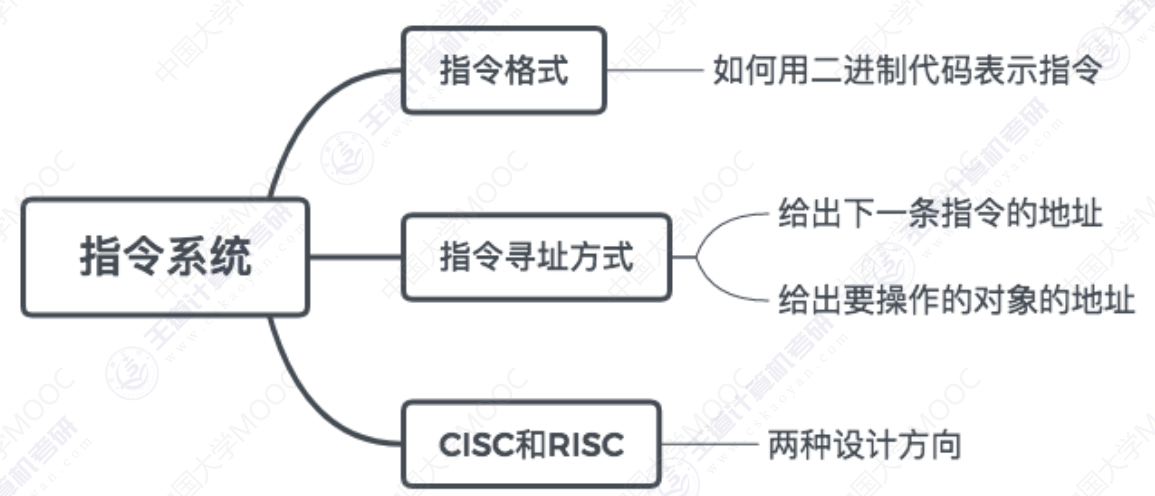

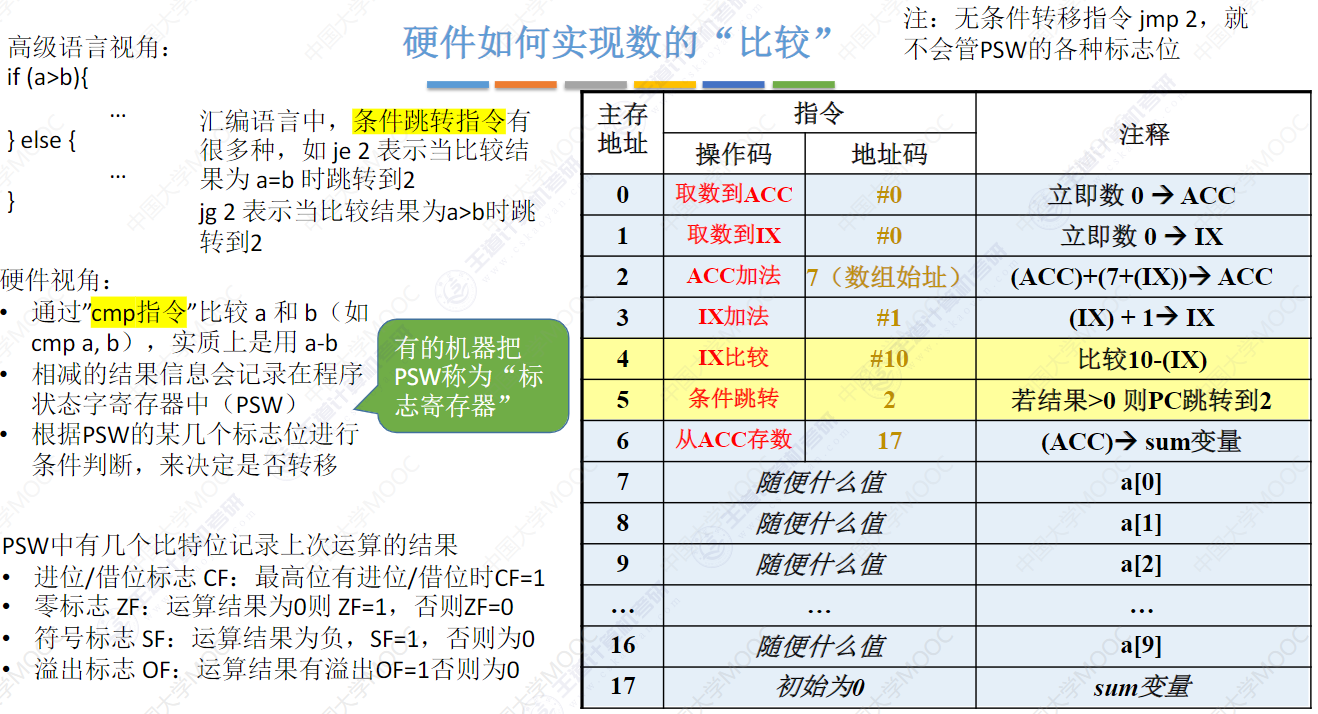

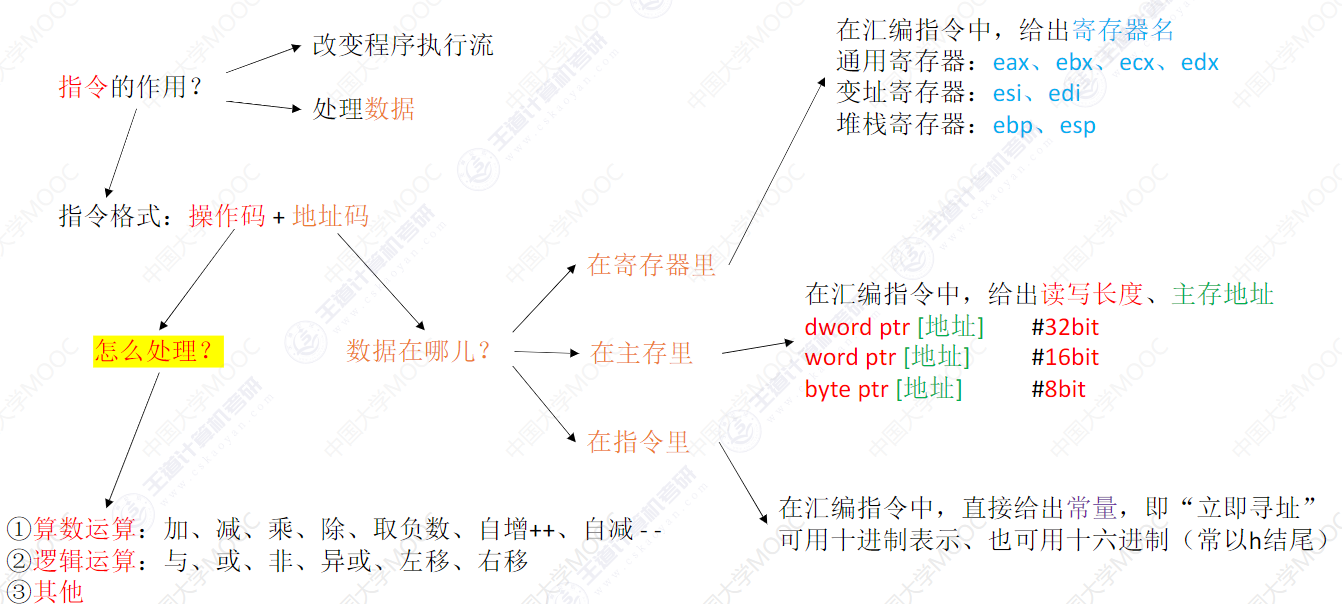

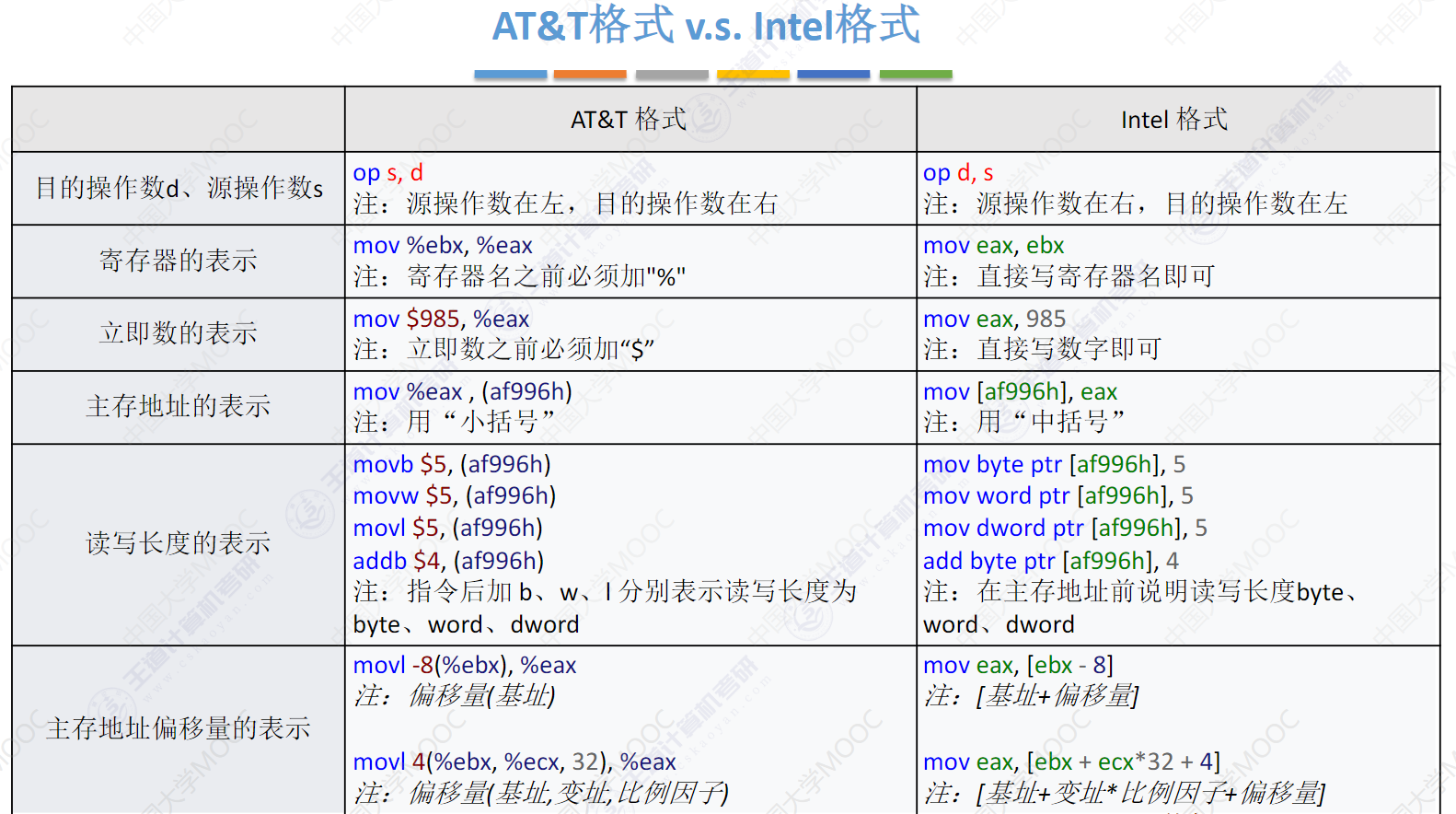

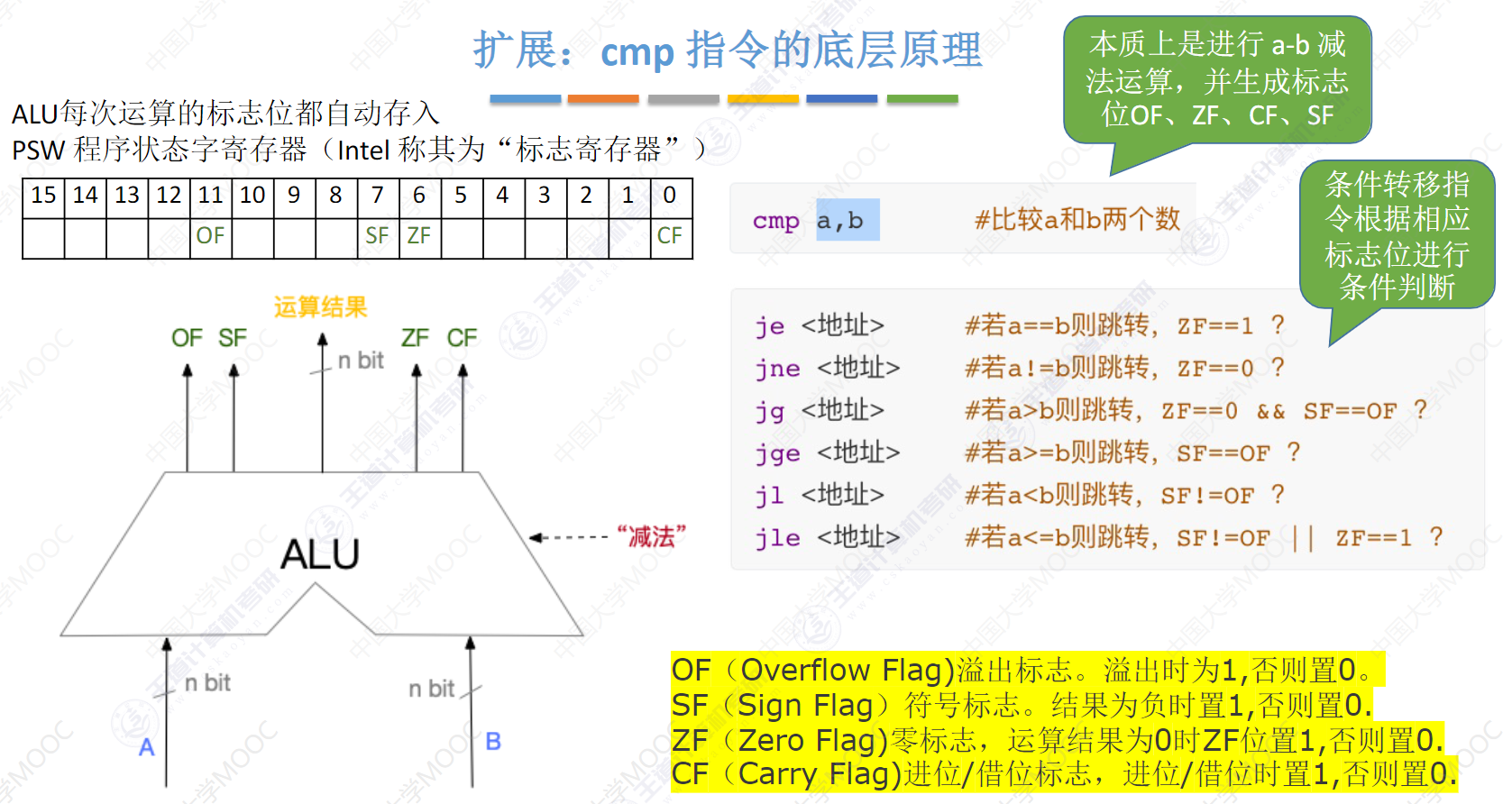

4️⃣: 指令系统

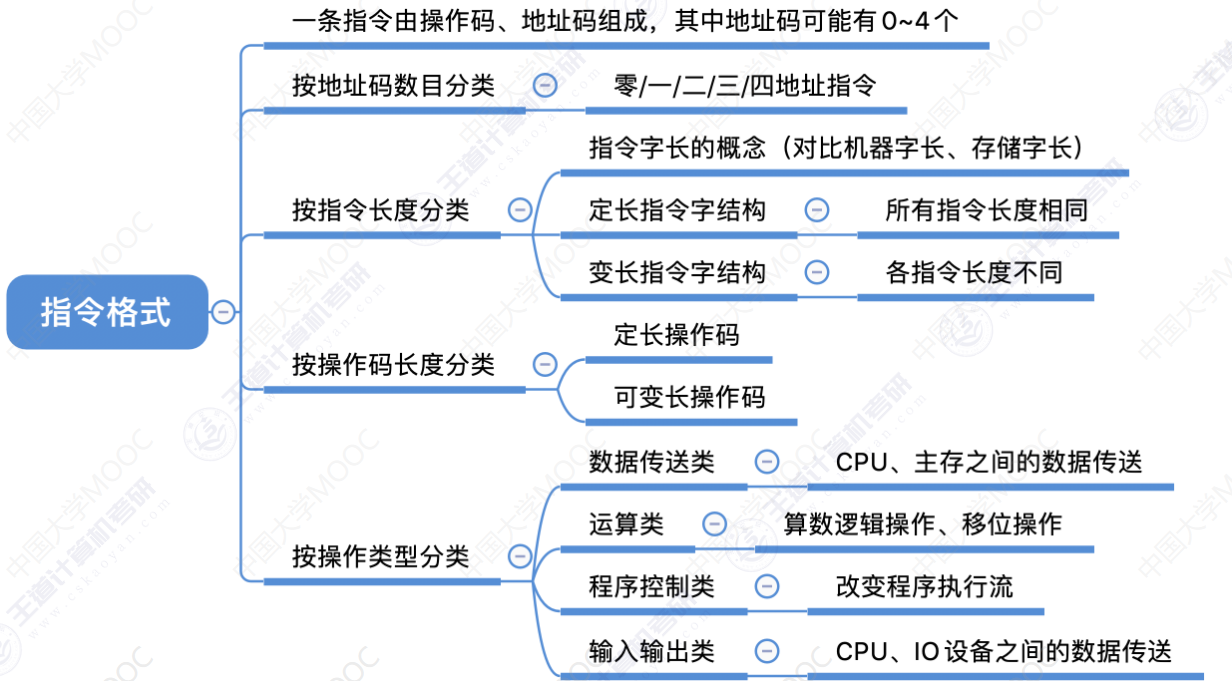

指令系统格式

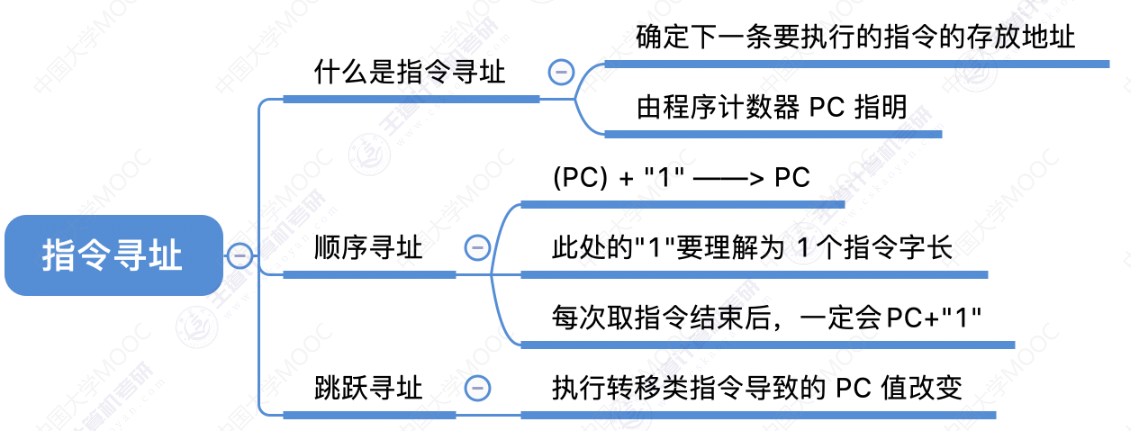

指令的寻址方式

机器级代码表示

CISC,RISC

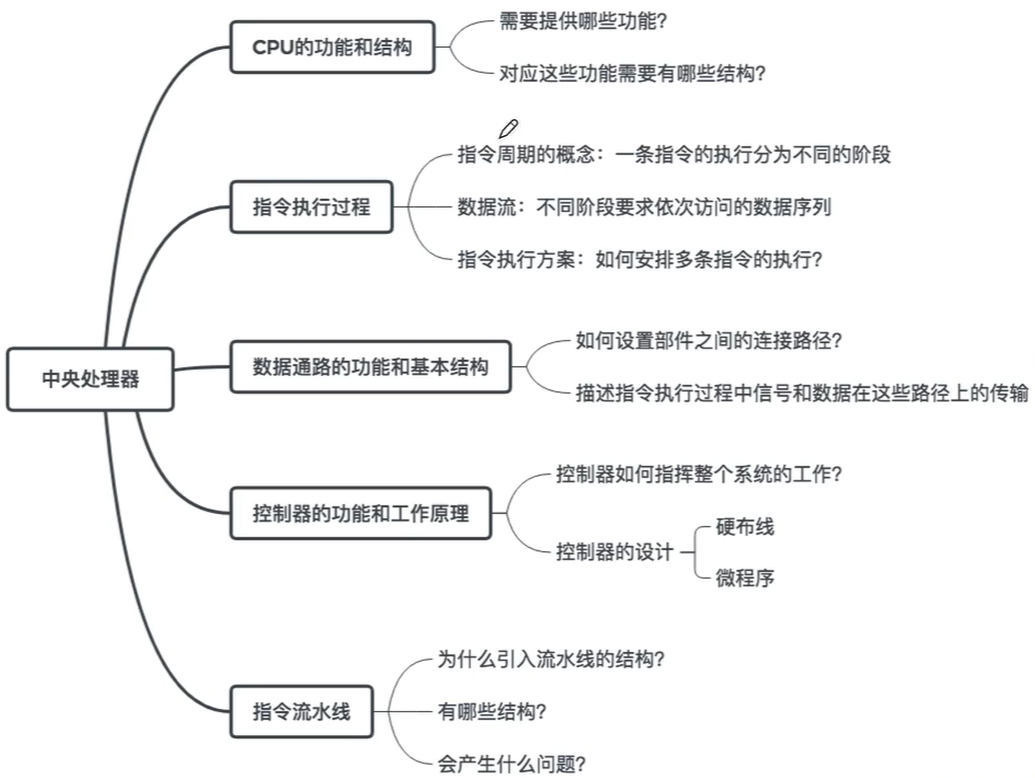

5️⃣: 中央处理器

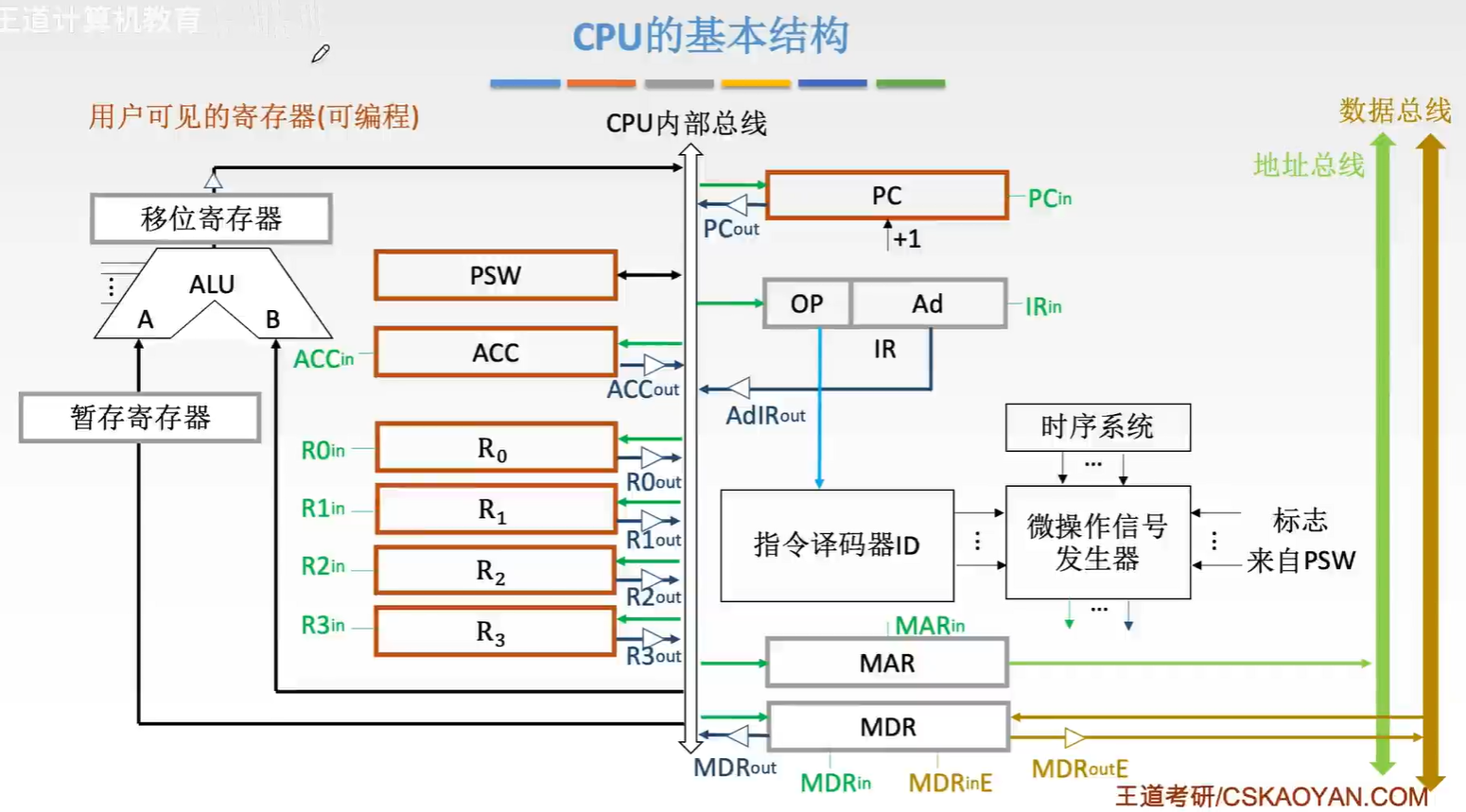

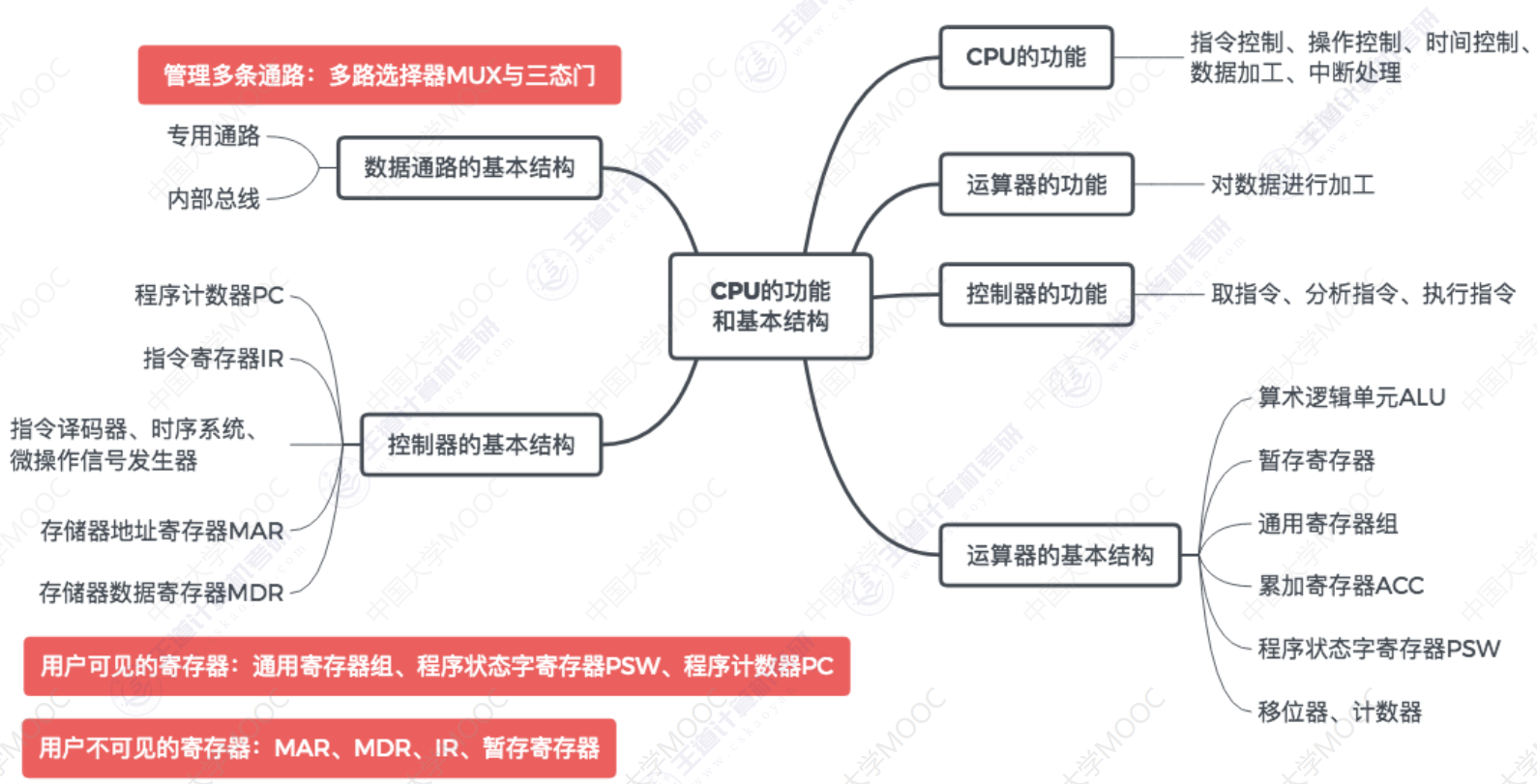

CPU的基本结构

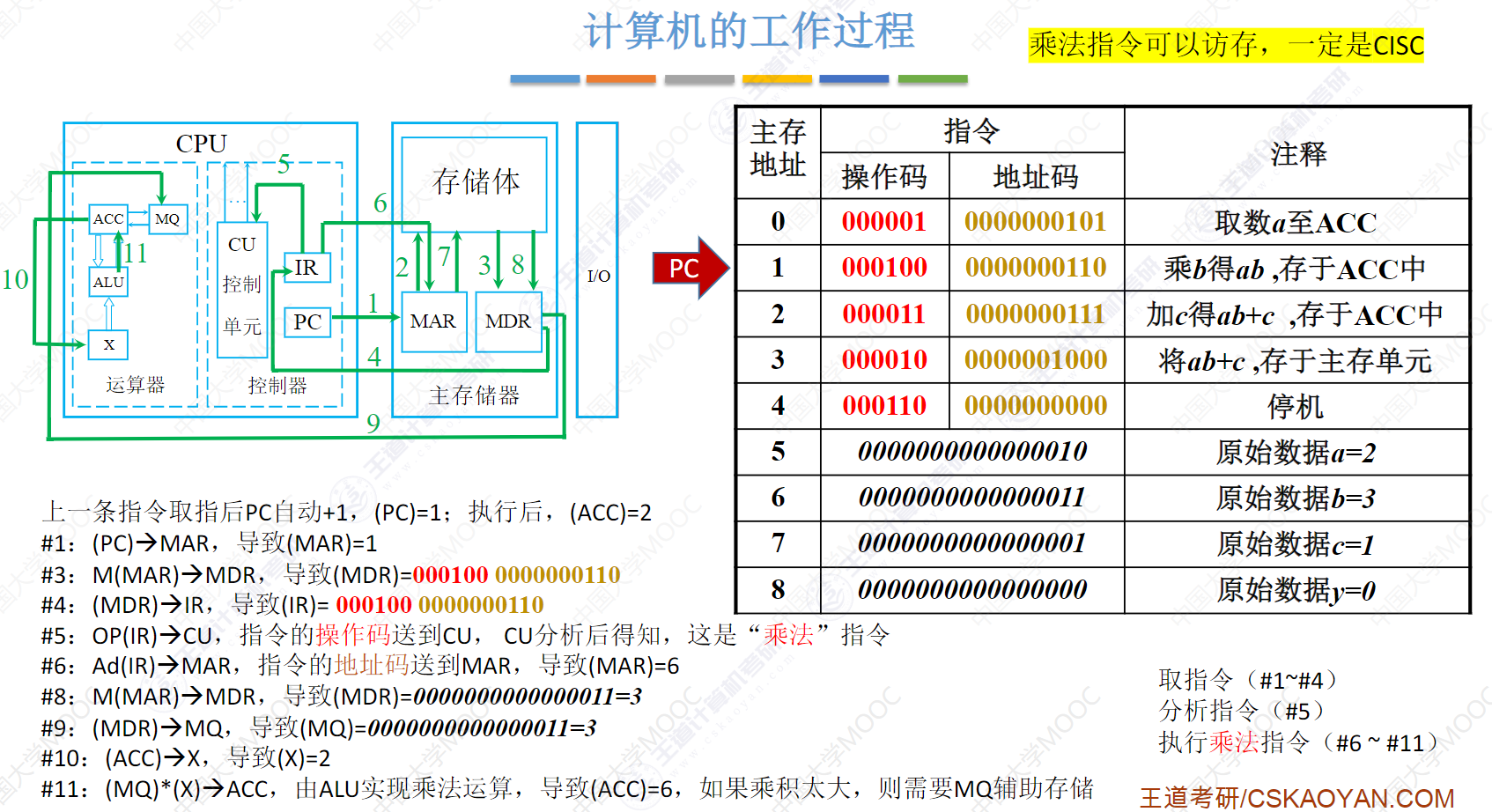

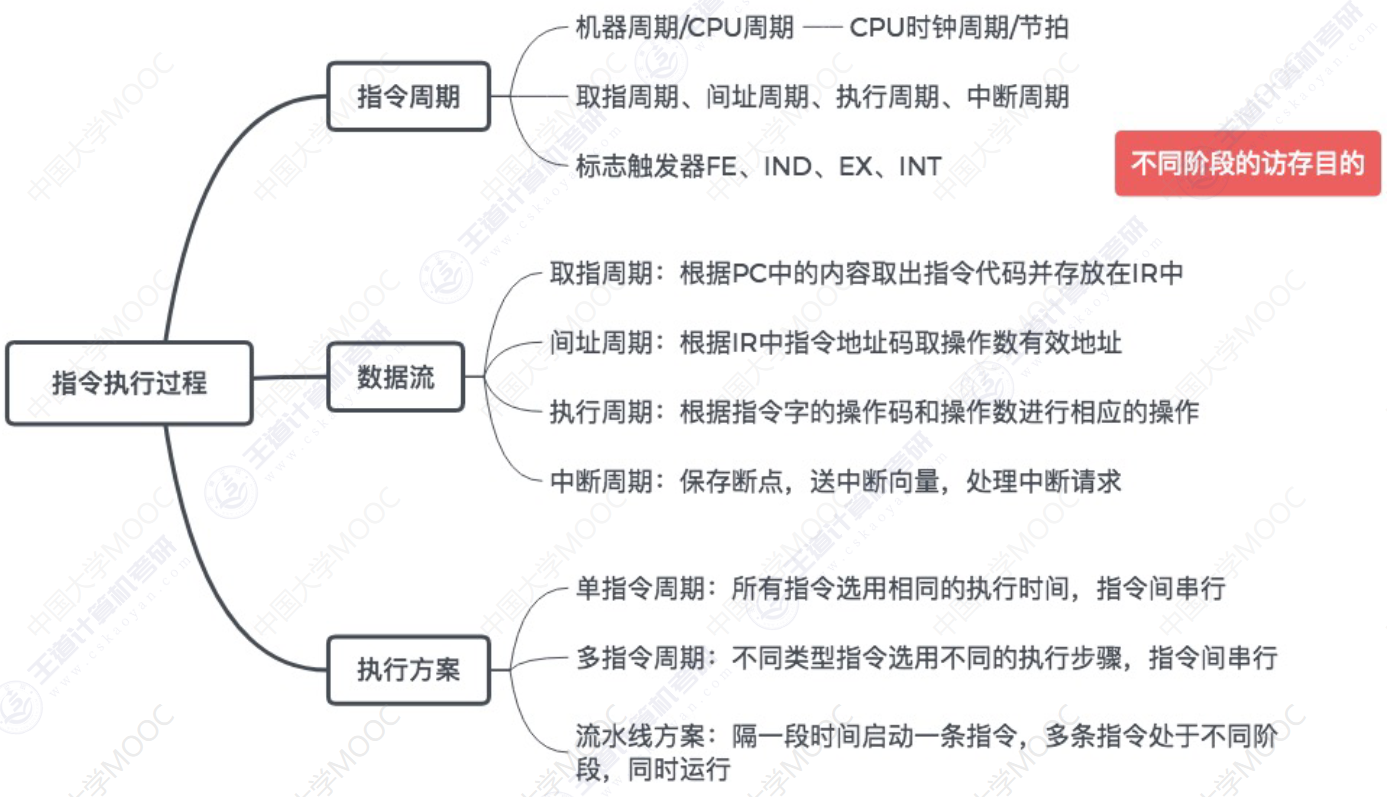

指令执行过程

📖指令周期的数据流(取值、间址、执行、中断周期)

点击查看

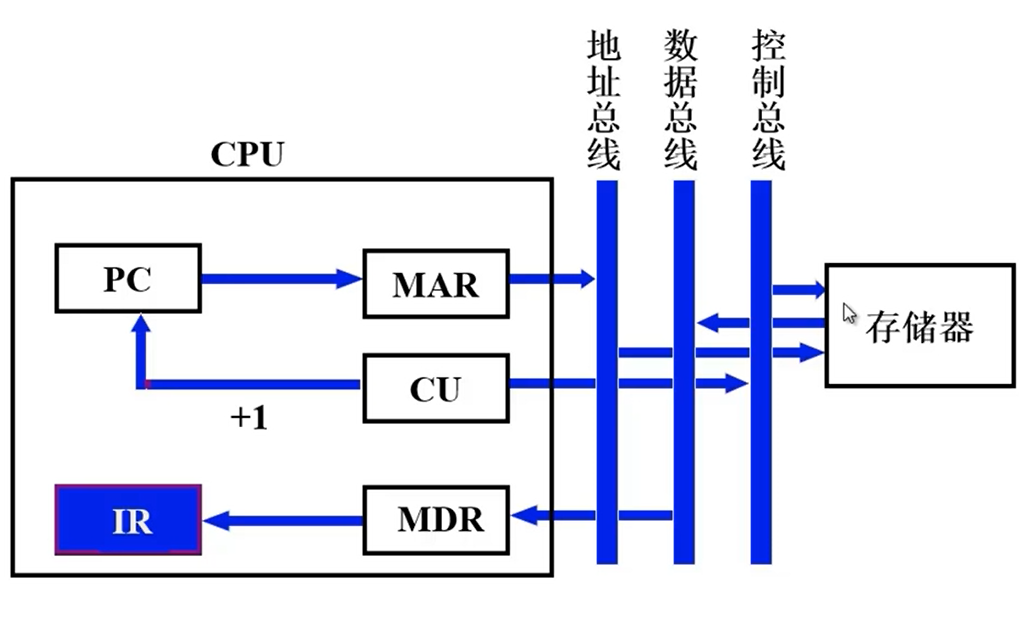

取指周期的数据流

取指周期从PC开始,因为PC知道要取的指令的内存单元的地址,PC要把地址传送给存储器,要先把地址传给MAR,再由MAR传给地址总线,再由地址总线传给存储器。CU把读操作这个控制信号送到控制总线上,再由控制总线送到存储器,存储器执行读操作,把相应的数据送到数据总线,数据总线再送到MDR,最后送到IR当中,此时,我们还要为取下一条指令做准备,要把下一条指令的地址保存在PC里,由CU控制PC进行PC+1操作,使PC指向下一条要取的指令的地址。这样一个完整的取值周期就完成了。(注意:这里的+1操作不是单纯的+1而是是加上下一条指令的地址)

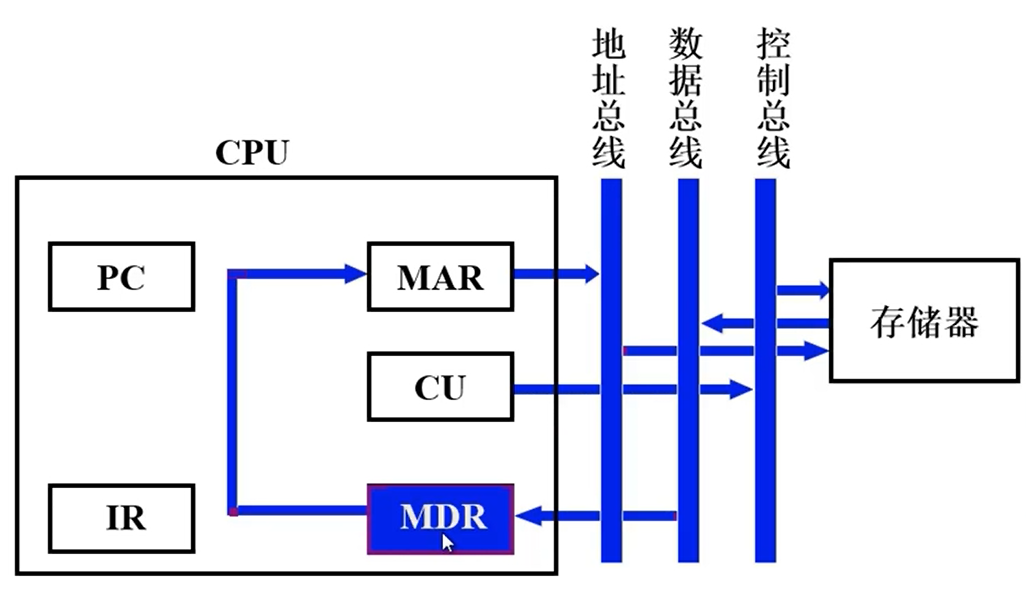

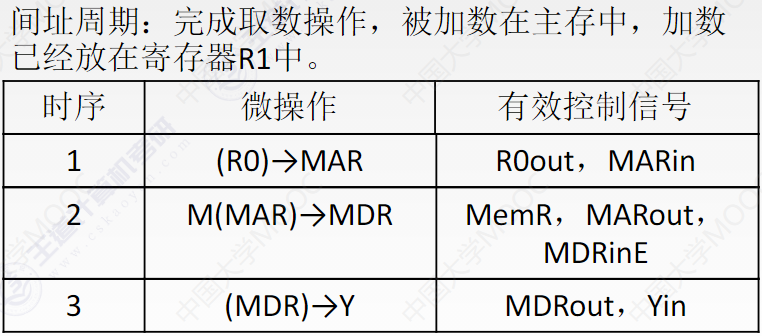

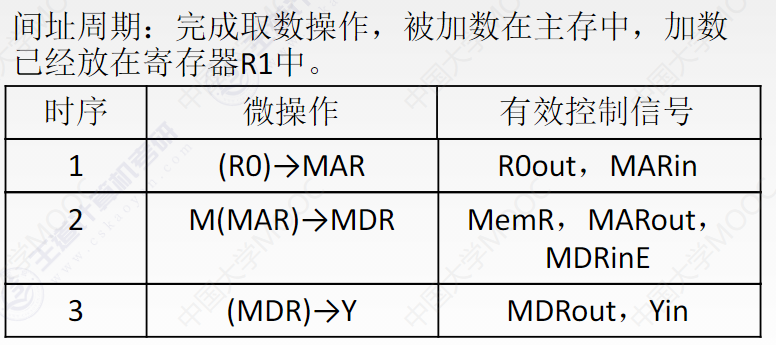

间址周期的数据流

操作数所在的内存单元的地址IR和MDR中都有,所以间址周期可以从IR开始,也可以从MDR开始,假设从MDR开始,MDR会把操作数中的地址码部分发送给MAR,MAR会把地址送给地址总线,再由地址总线送给存储器,然后CU发出读操作,操作信号先送给控制总线,再由控制总线送到存储器当中,存储器完成读操作,把数据送到数据总线上,再由数据总线送到MDR当中,这个时候MDR才真正保存了我们所需要的操作数的真正的地址。

执行周期数据流

不同指令的执行周期数据流不同。

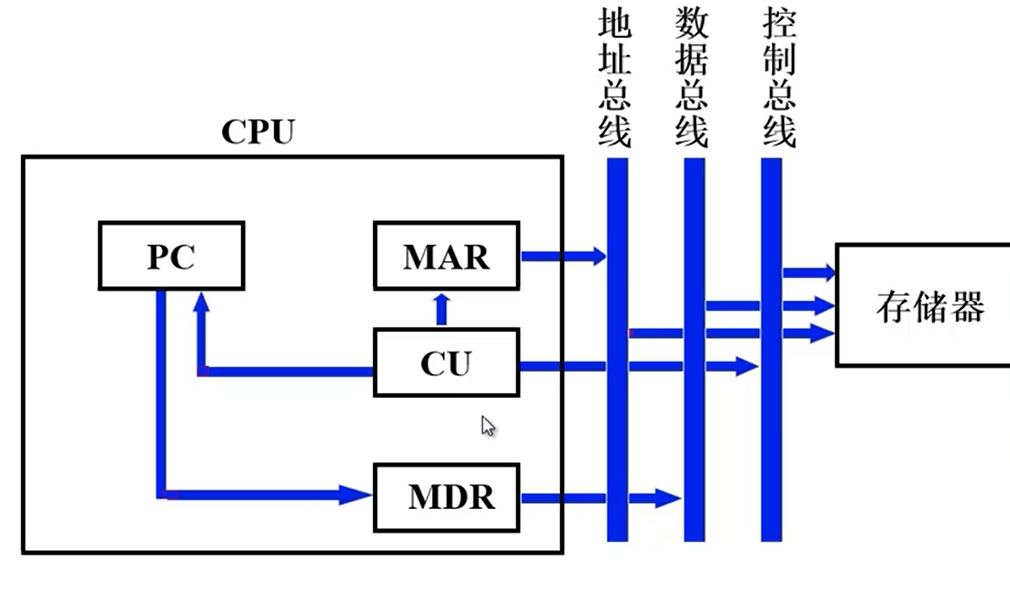

中断周期的数据流

因为CU知道程序断点应该保存在哪个位置,所以中断周期从CU开始,CU给出地址,把地址放进MAR中,MAR再送到地址总线,地址总线送到存储器,因为保存断点是一个写操作,所以CU会发出一个写命令,并把写命令送到控制总线,再由控制总线送到存储器,保存断点即返回到程序中断之后的那个位置,也即中断之后要执行的下一个命令地址,中断之后的下一条命令保存在PC当中,所以保存断点即保存当前PC的值,PC会把值送到MDR当中,MDR送到数据总线,数据总线再保存到存储器中。中断服务程序的入口地址是由CU给出,CU会把这个地址写入PC,中断服务程序的入口就给了PC

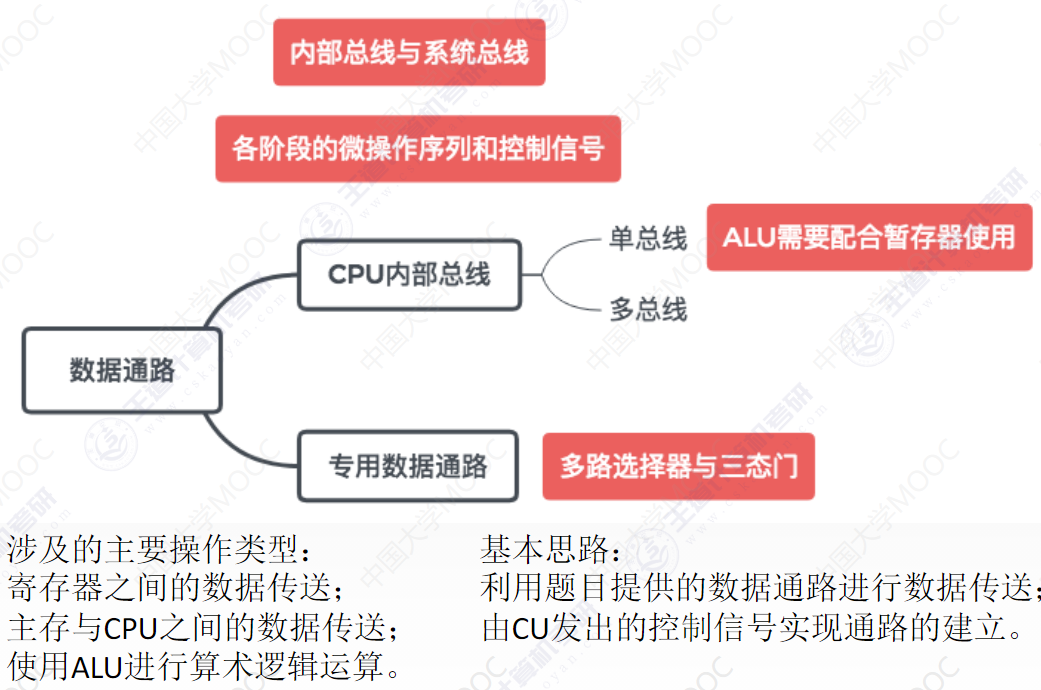

数据通路的功能和基本结构

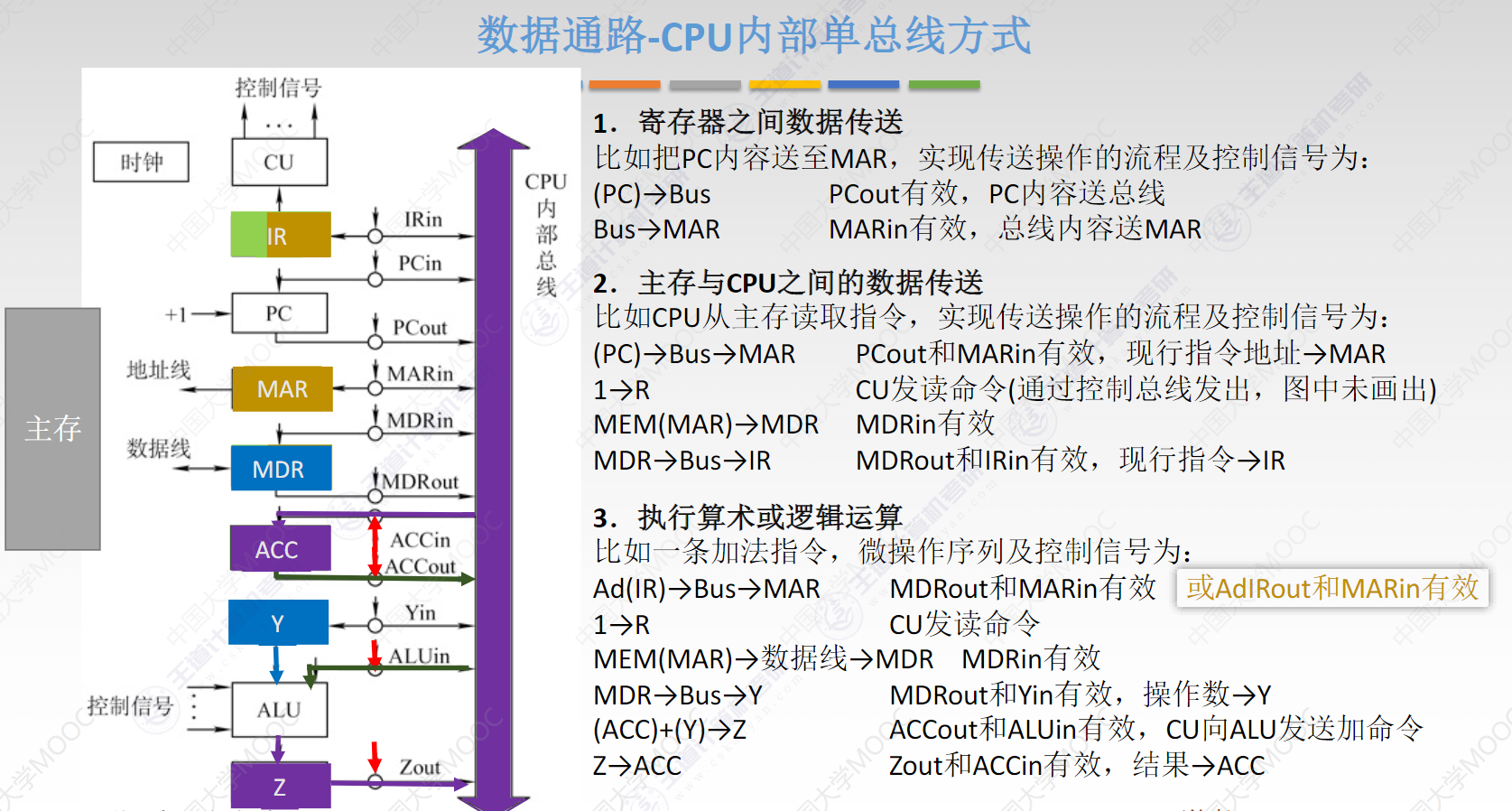

CPU内部单总线方式

点击查看

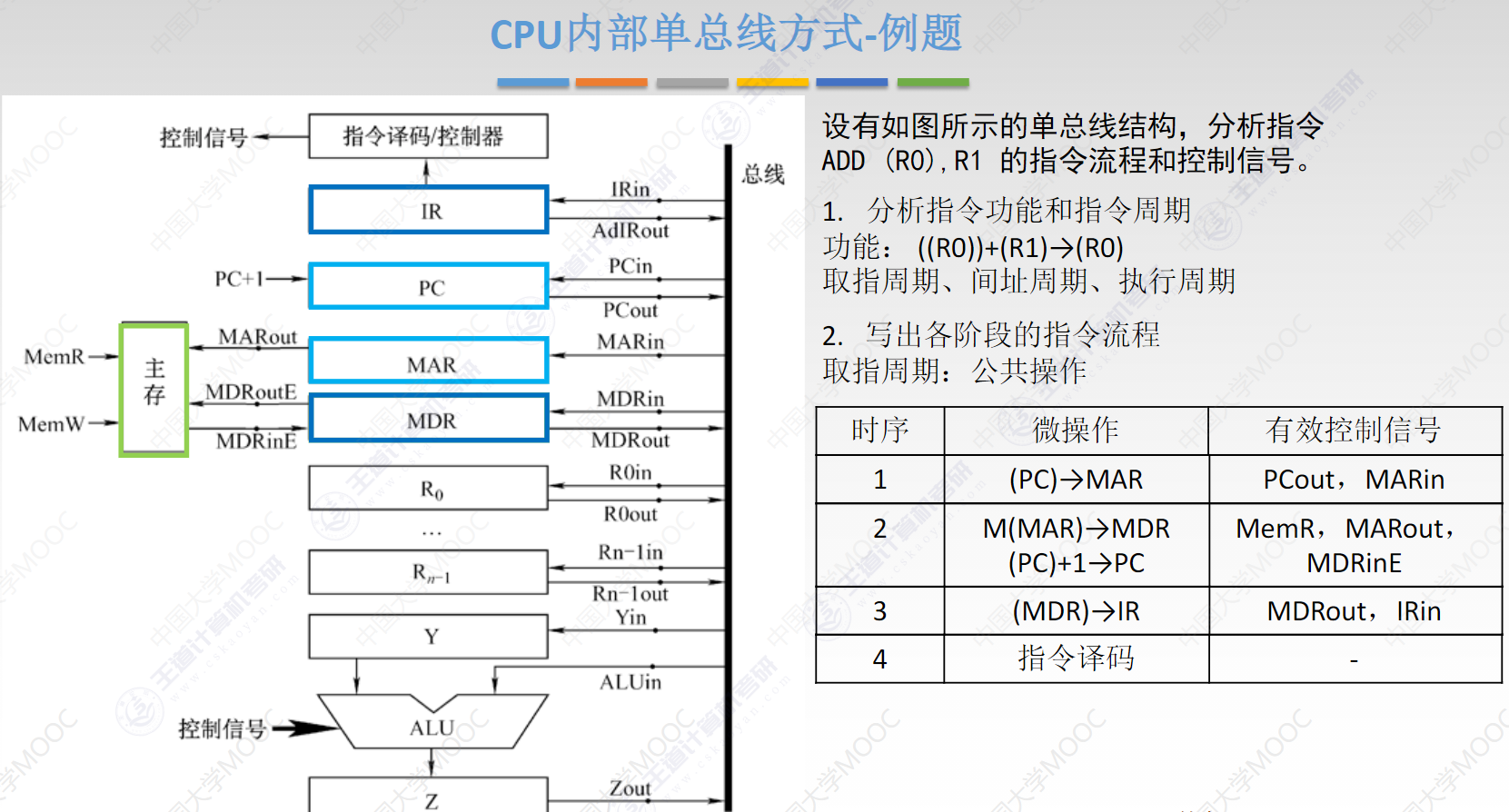

例题

点击查看

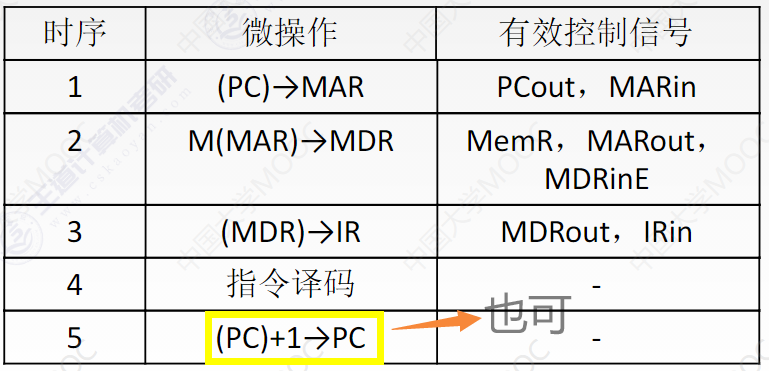

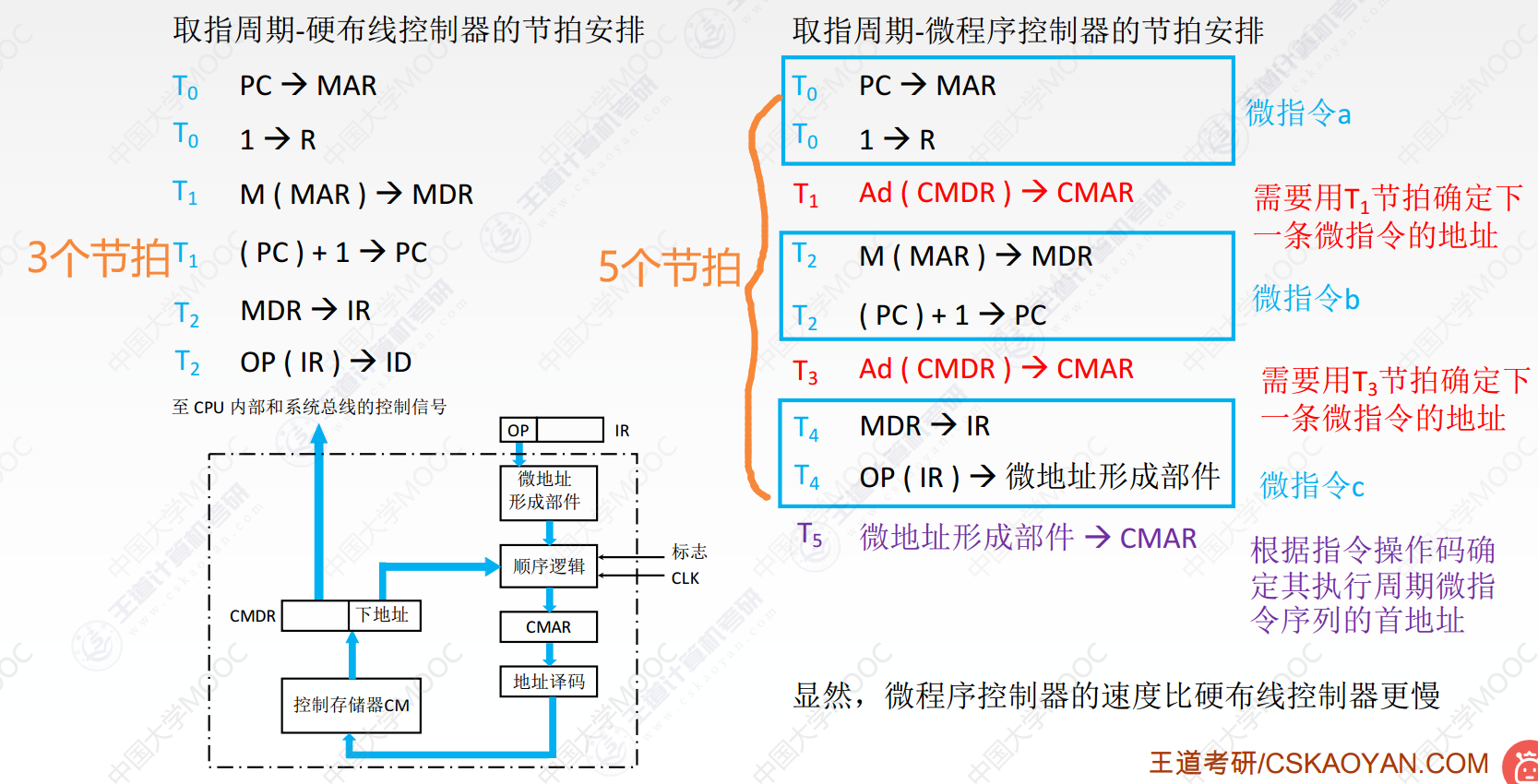

取指周期

间址周期

执行周期

控制器的功能和基本原理

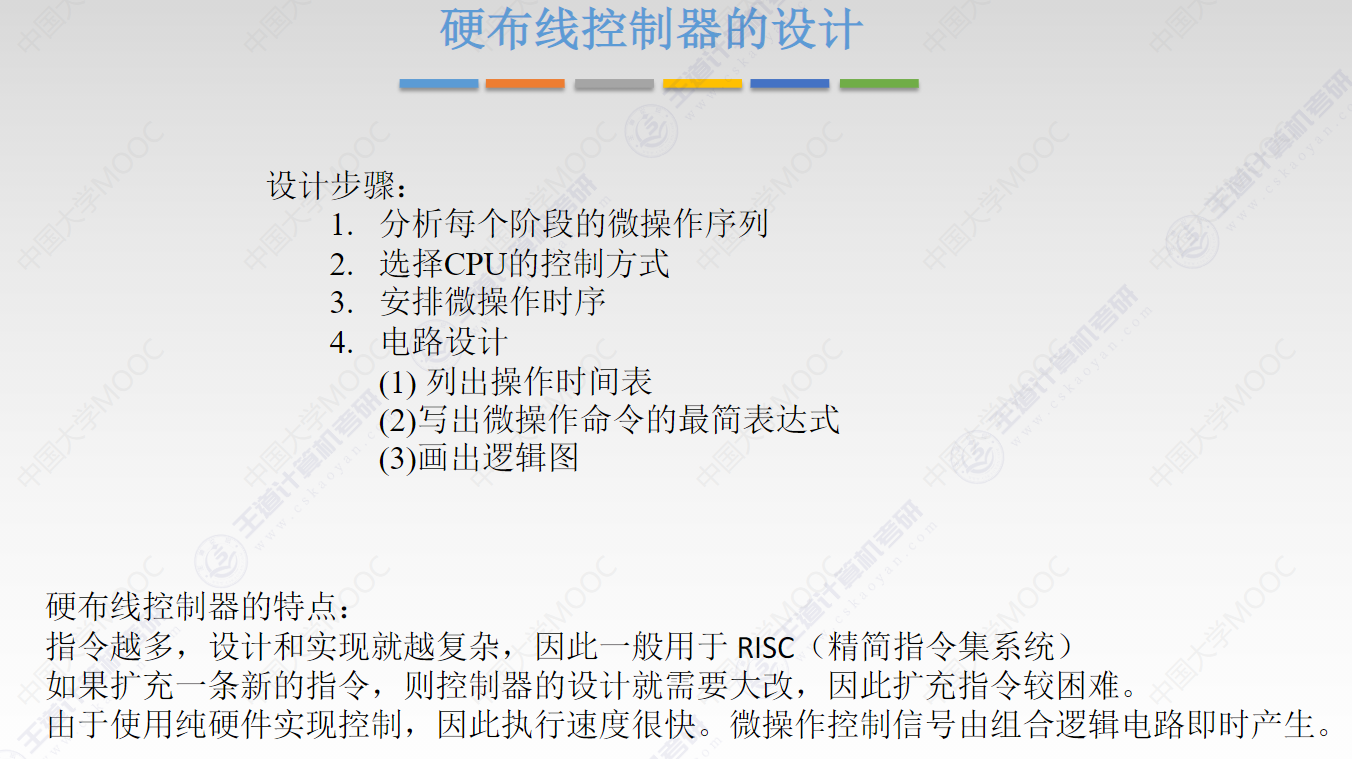

硬布线控制器

文稿: 第一个步骤,我们需要罗列出所有的指令,所有的指令在每一个阶段的微操作序列。

然后选择一种CPU的控制方式,也就是要确定机器周期是否定长,每一个机器周期内要安排几个节拍,确定这样的一个事情,

第三步安排第一步得到的这些微操作序列的一个时序,哪些微操作可以在t0这个时序内完成,哪些微操作可以在t1,哪些微操作应该放在t2?要进行这样的一个安排好,最后根据之前整理的信息,可以设计出电路,首先需要列出操作时间表,就是要把每一个指令周期。每个周期内的各个节拍有可能使用到哪些微操作?把这个信息用一张表罗列出来,然后也需要根据具体的指令。是否需要使用到某一个微操作,在这个表里边标一。然后接下来根据操作时间表就可以得到微操作命令,它所对应的逻辑表达式如果能把它画到最简的话,就意味着我们的电路也可以更简单。

接下来最后一步,根据我们得到的逻辑表达式就可以得到这个组合逻辑,电路的电路图,这就是硬部线控制器的一个设计的步骤。

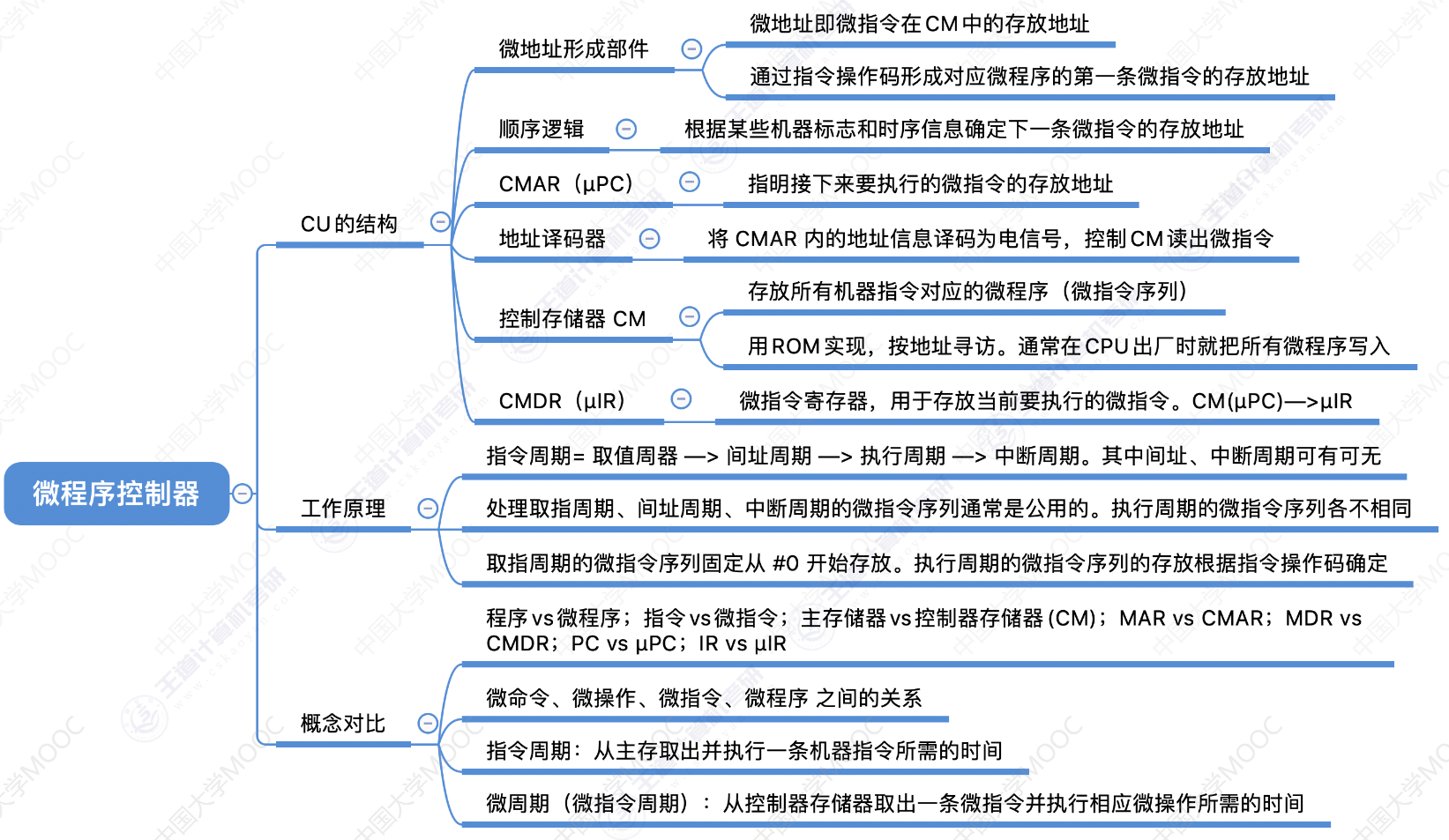

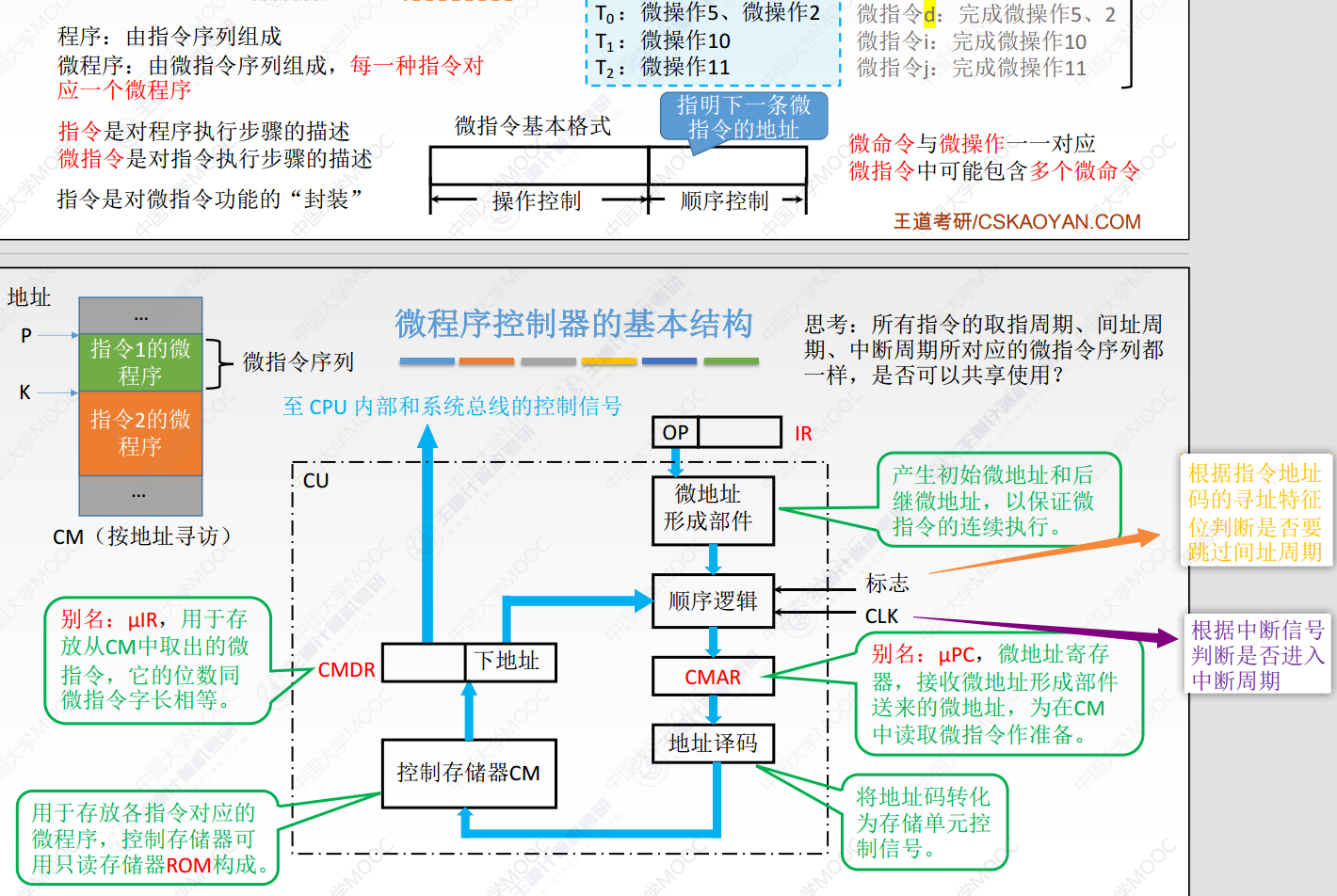

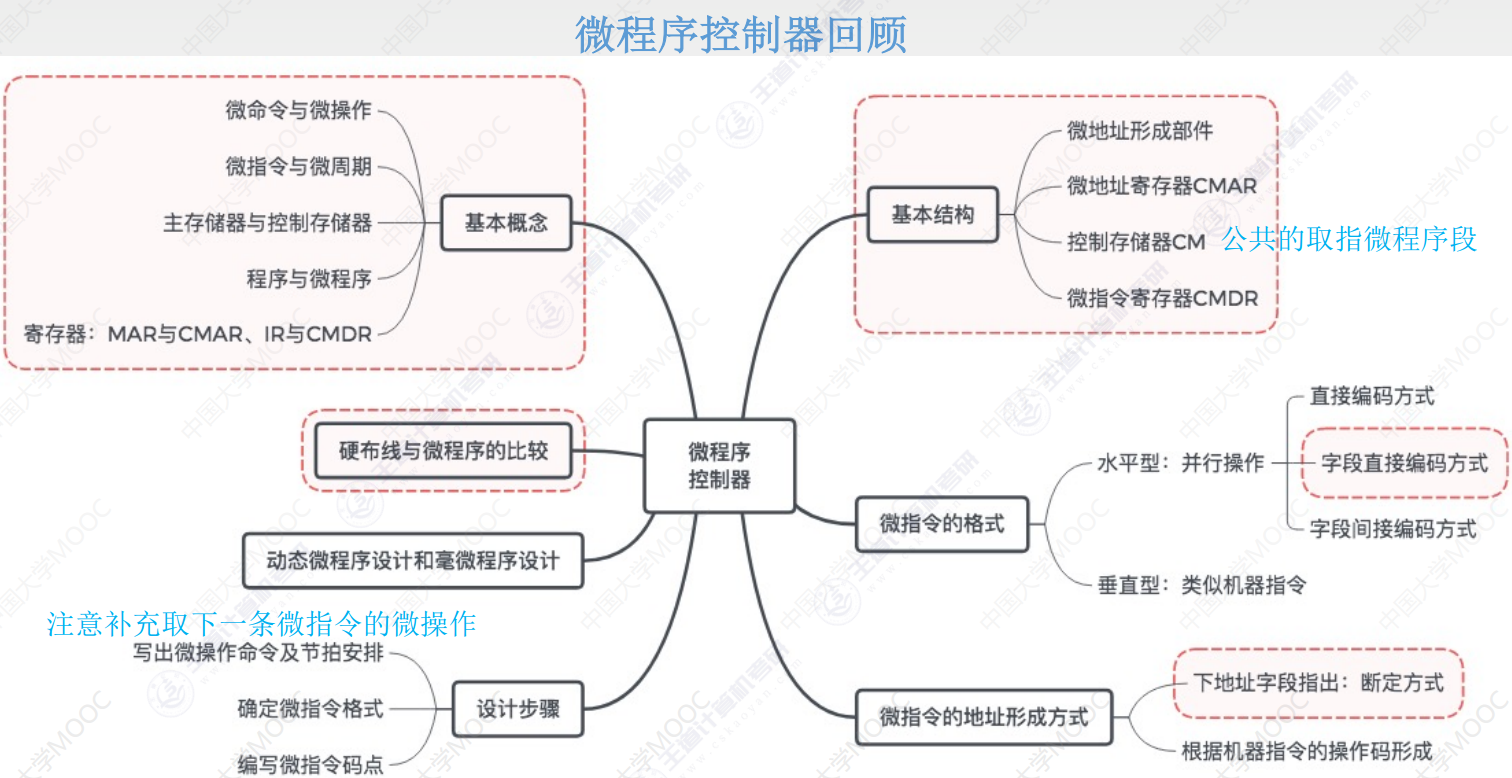

微程序控制器

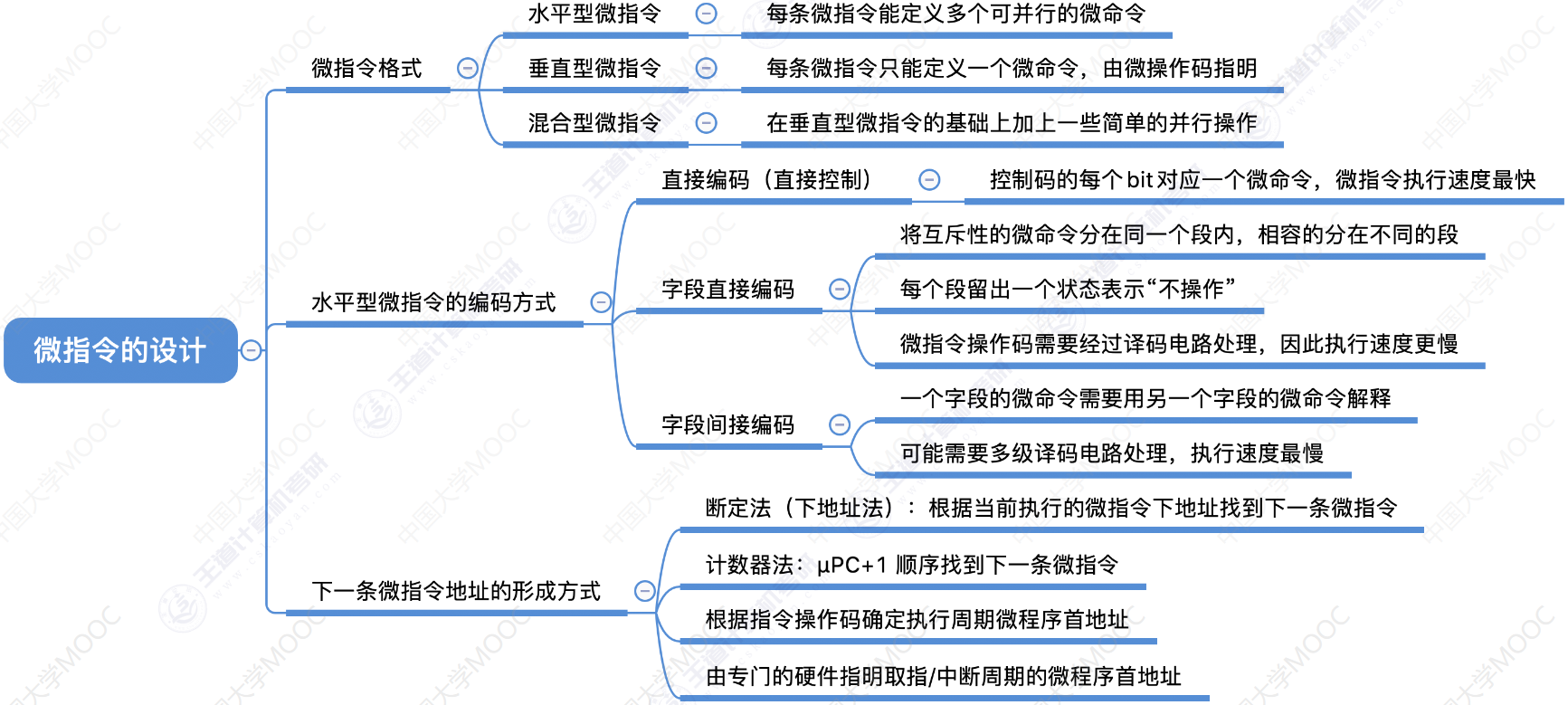

微指令的设计

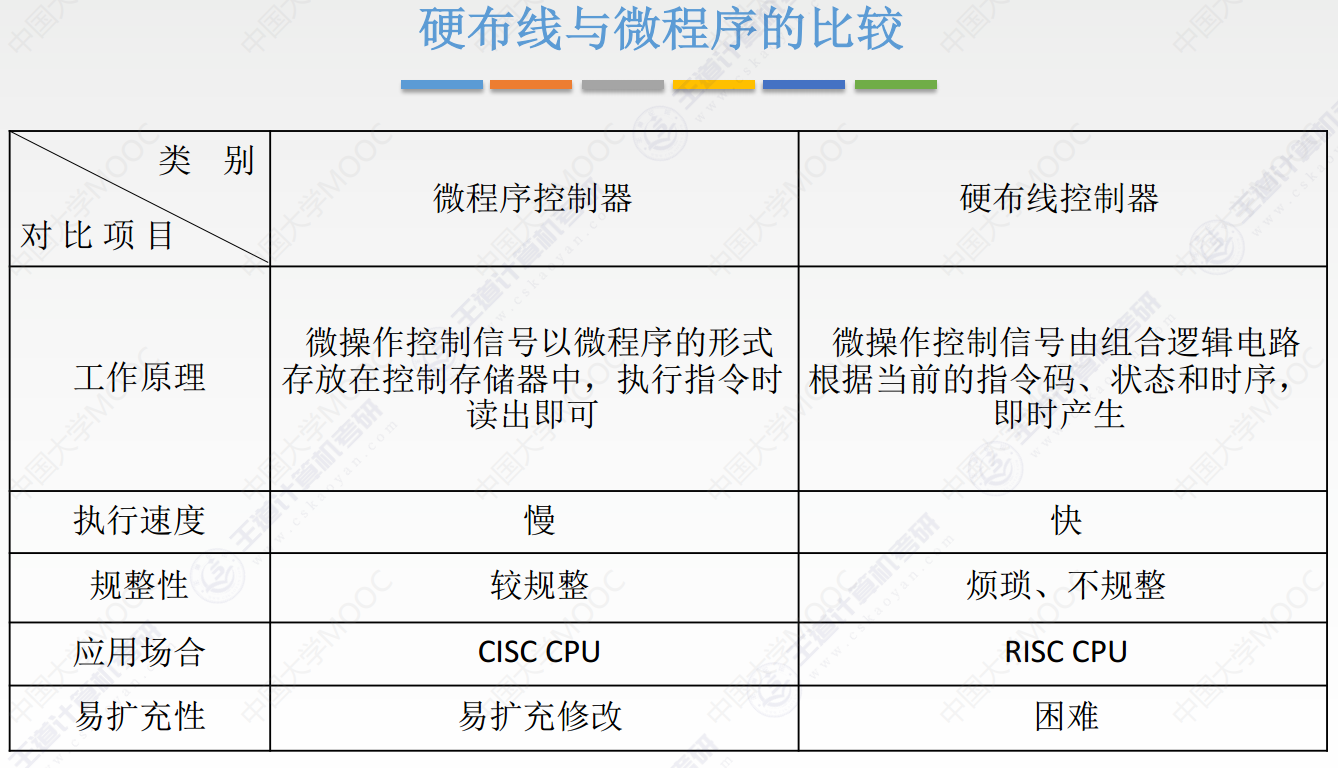

硬布线和微程序的比较

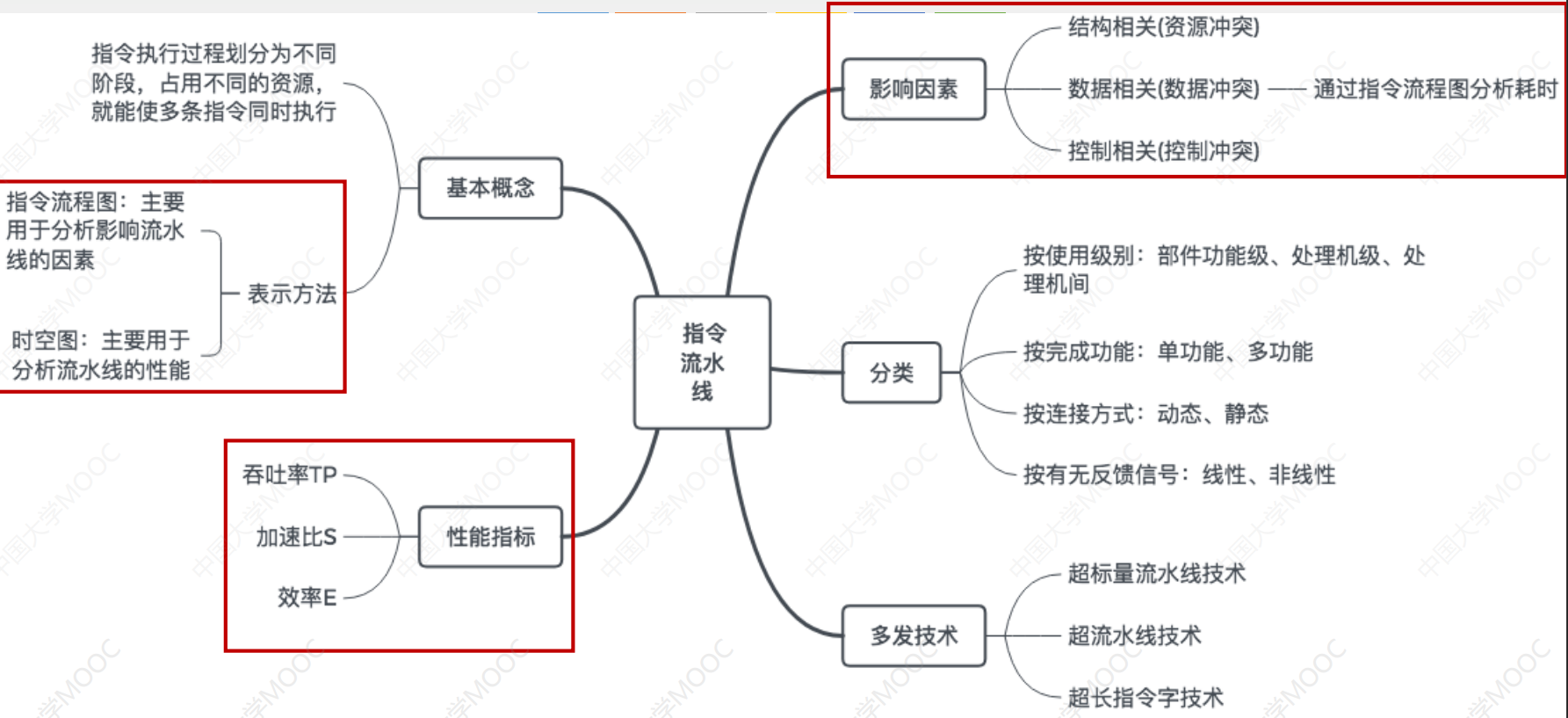

指令流水线

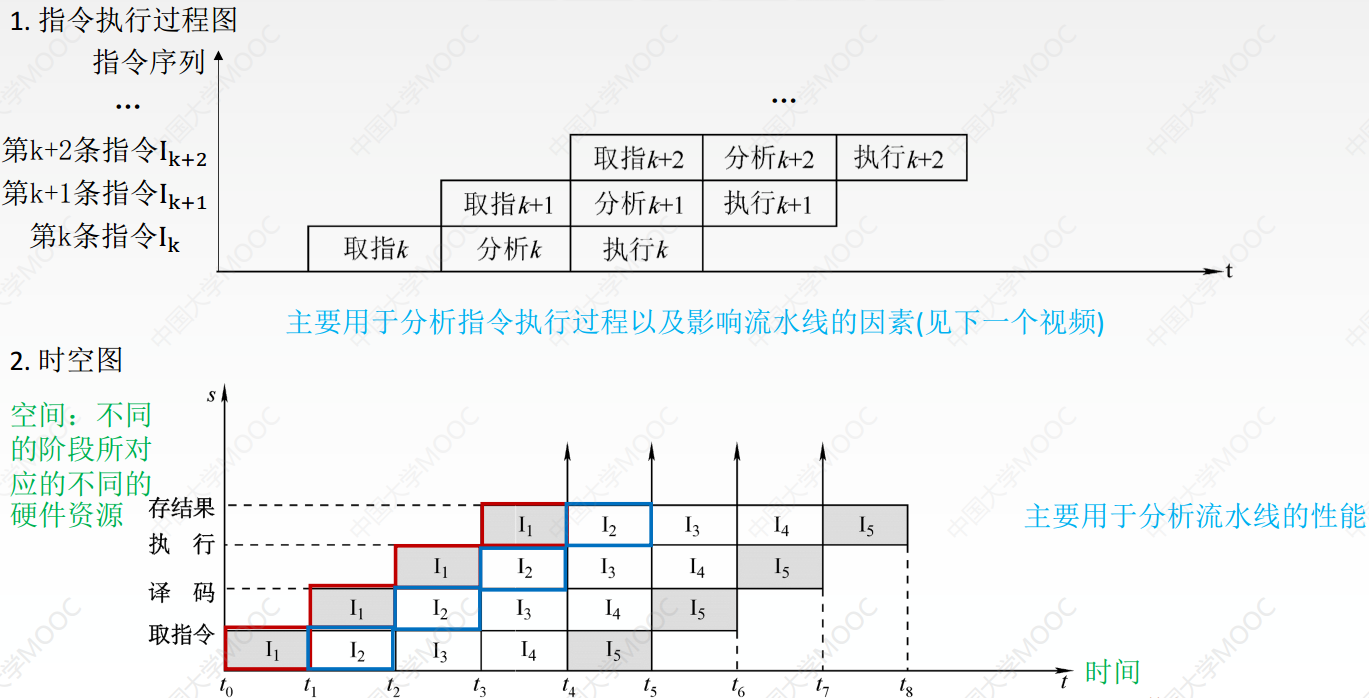

表示方法

点击查看

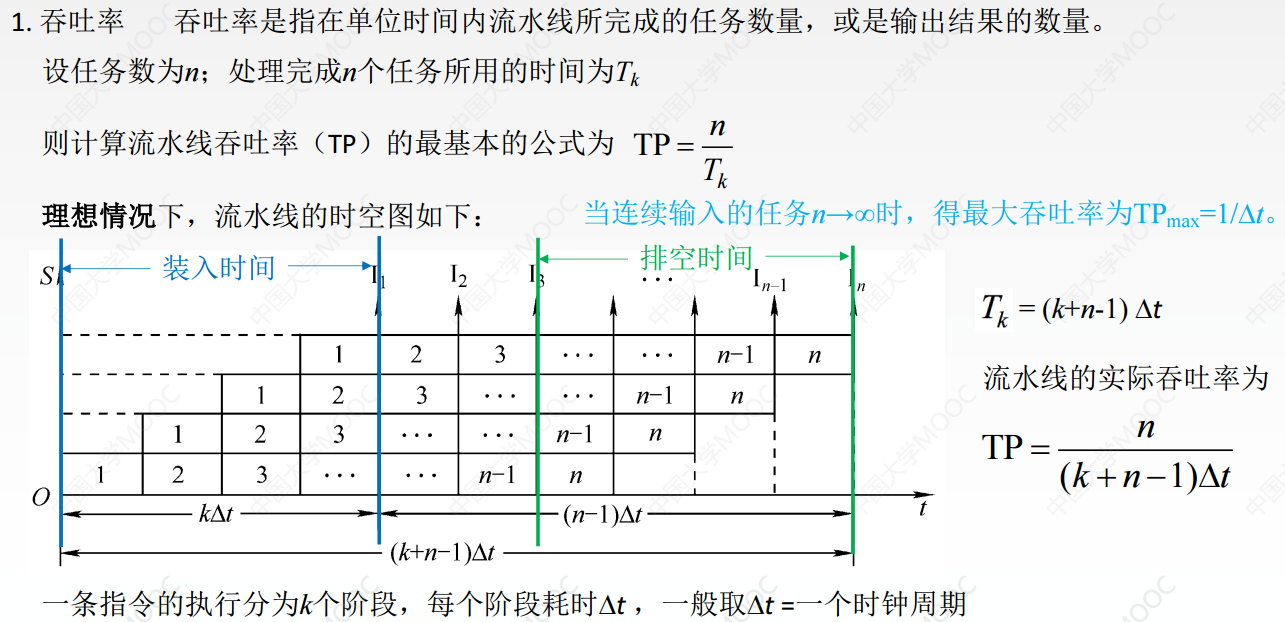

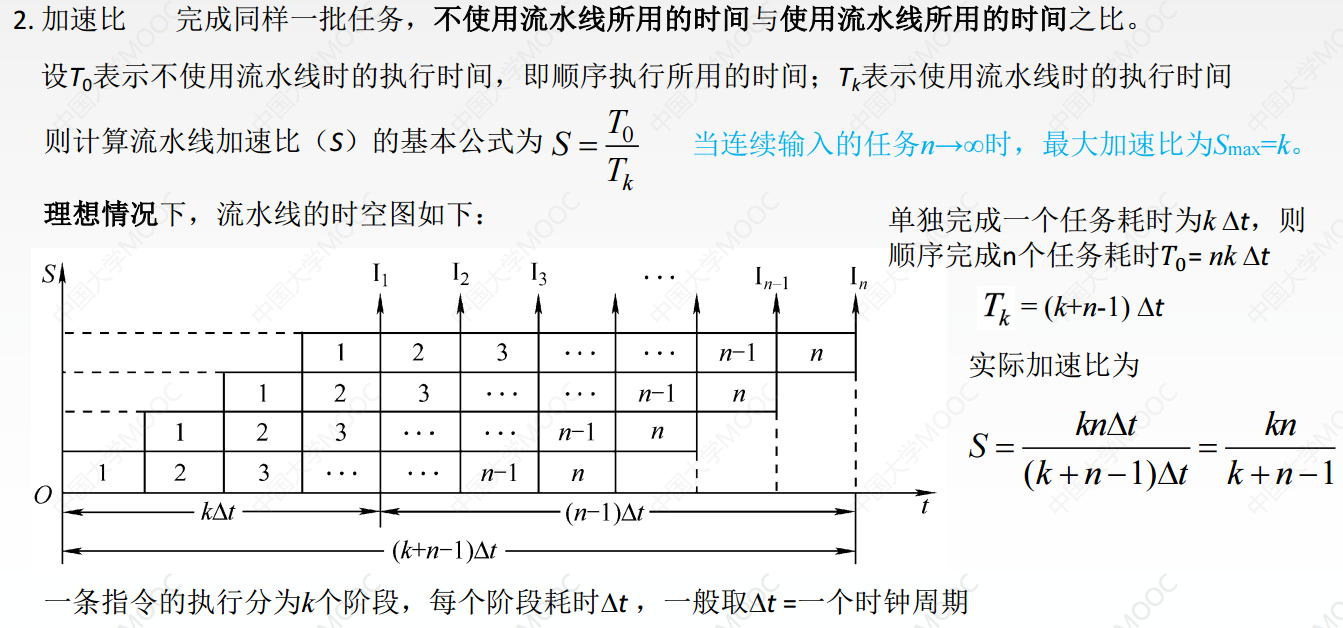

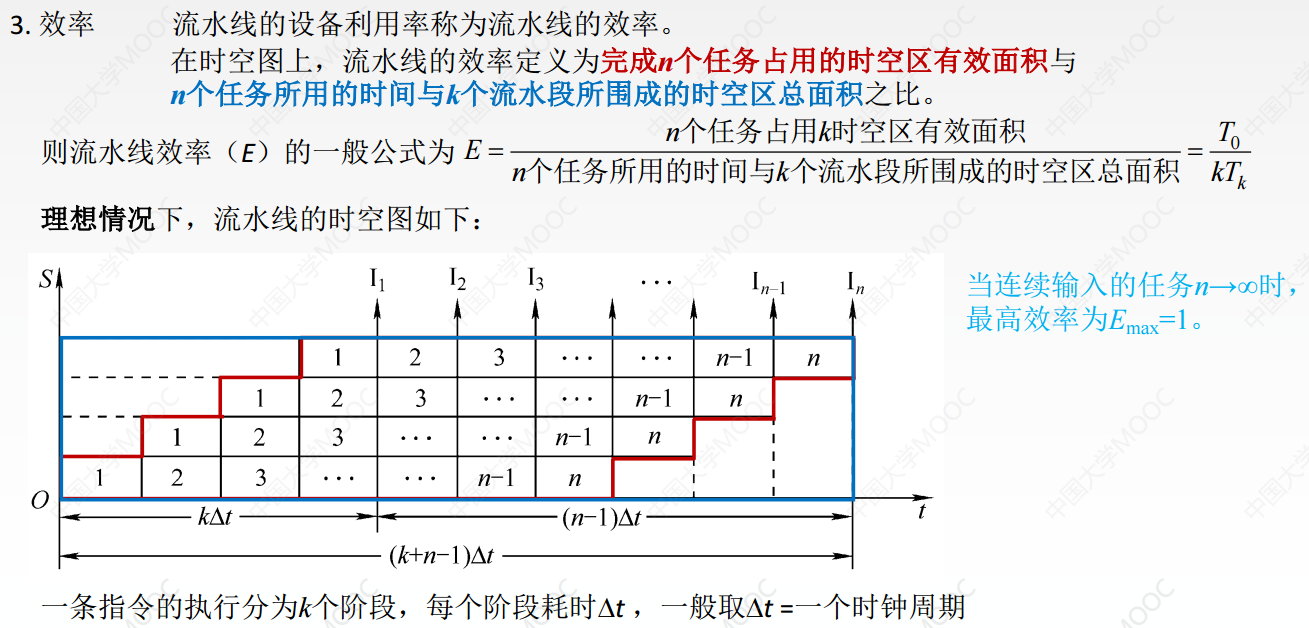

吞吐率,加速比,效率

点击查看

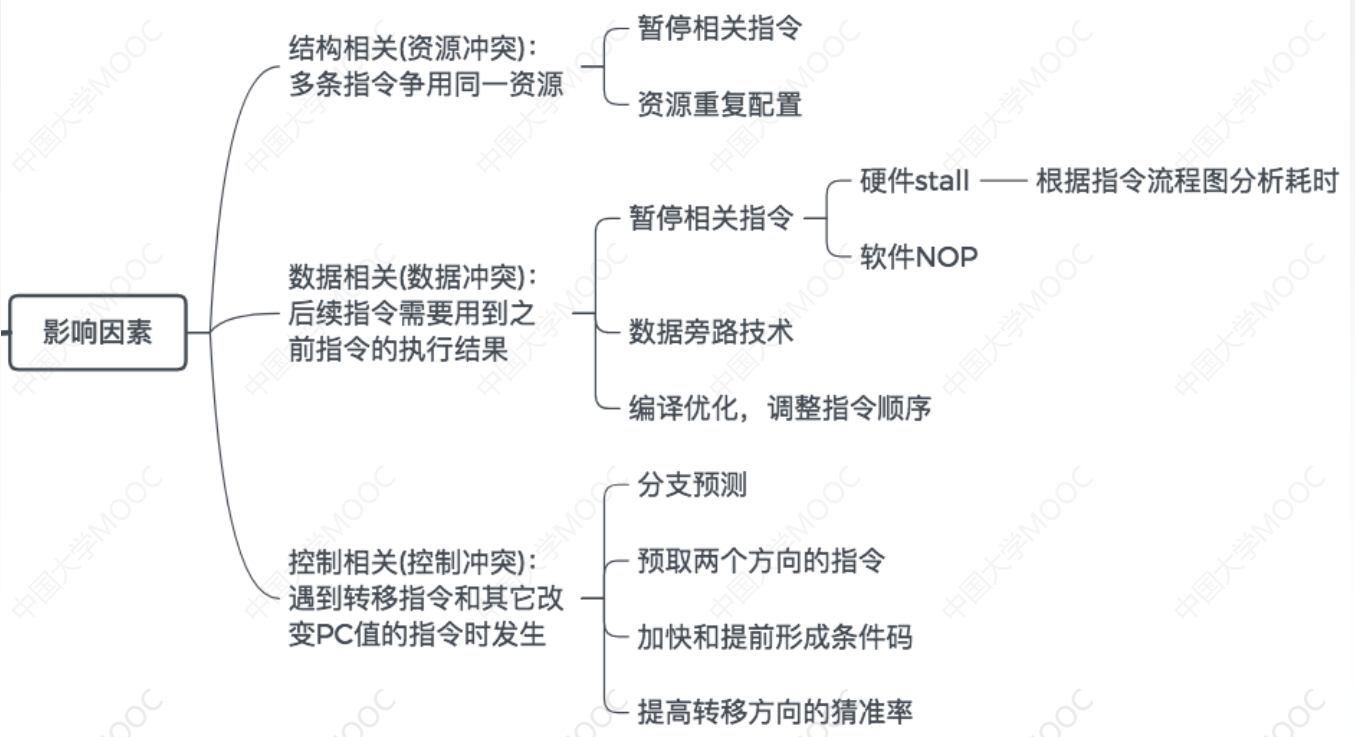

指令流水线影响因素分类

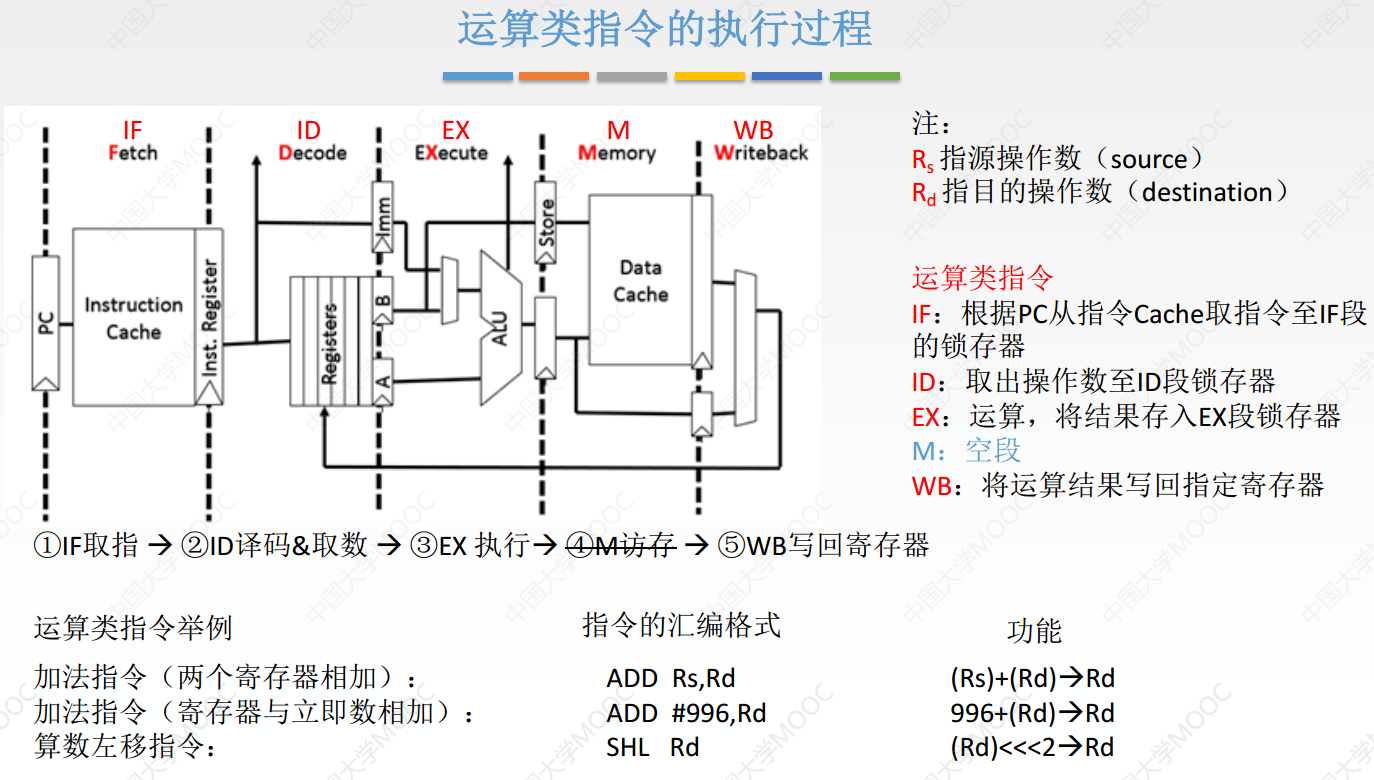

五段式指令流水线

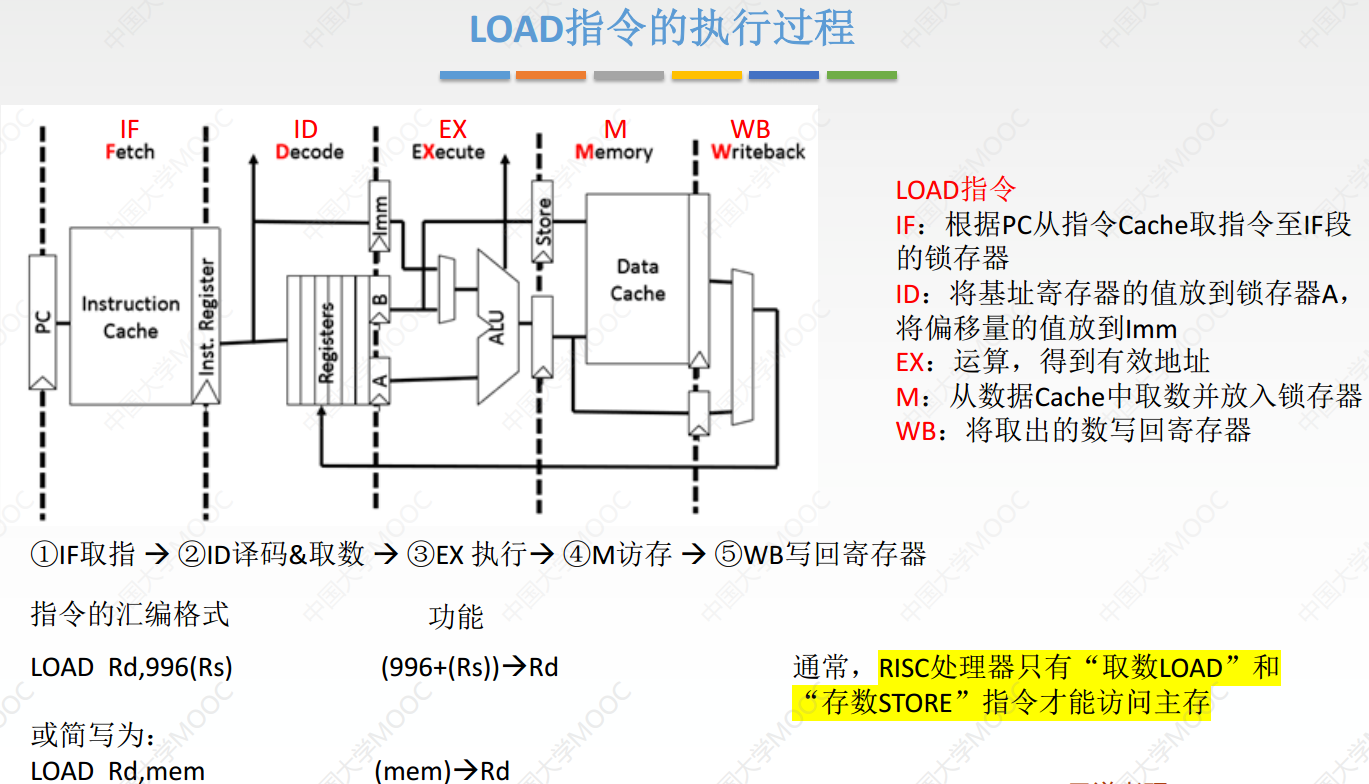

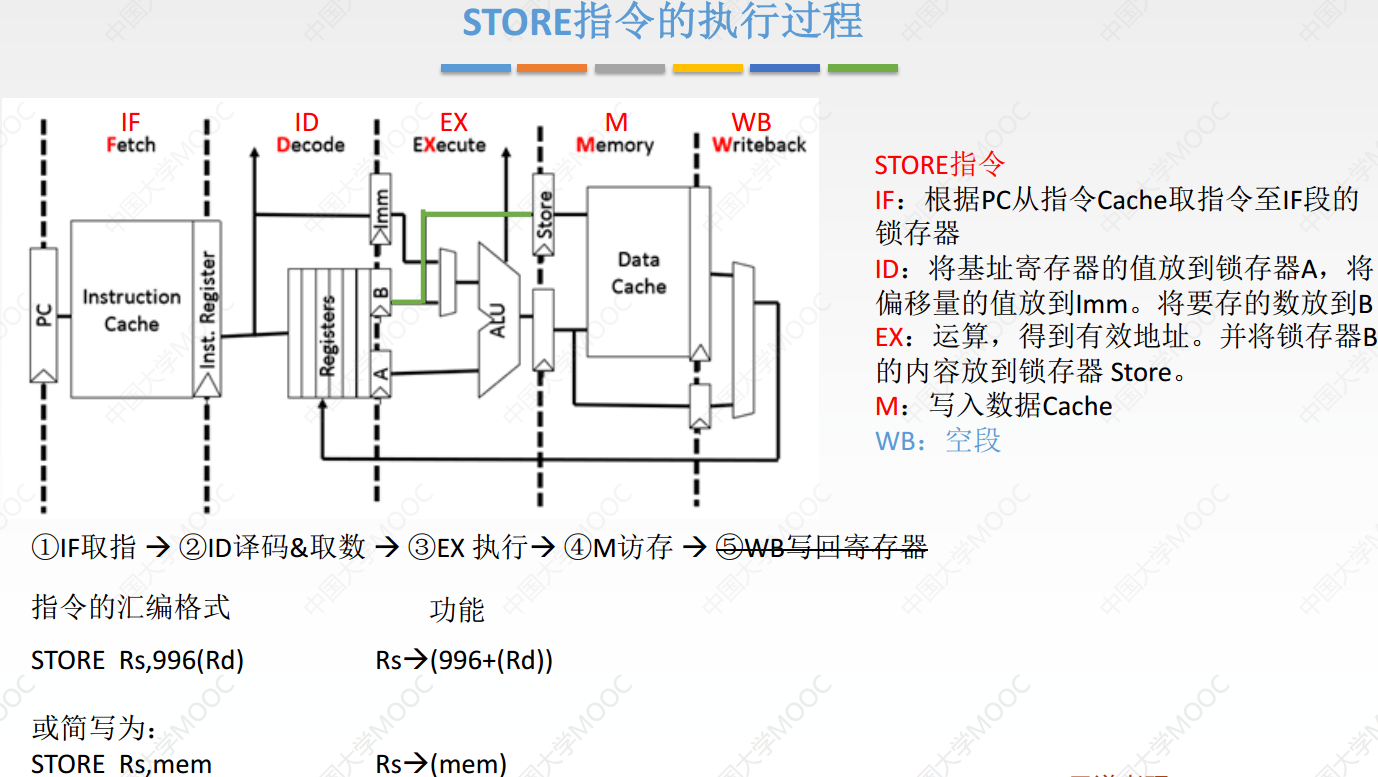

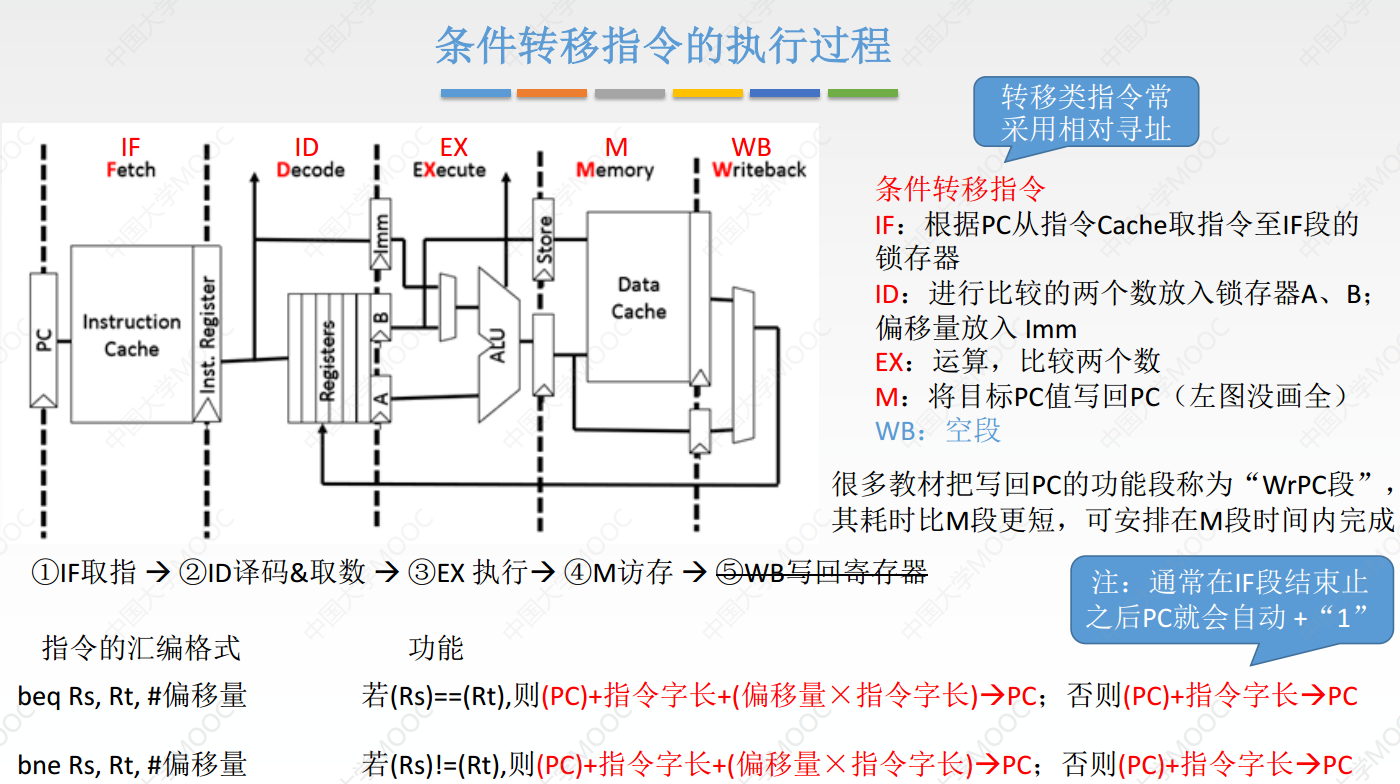

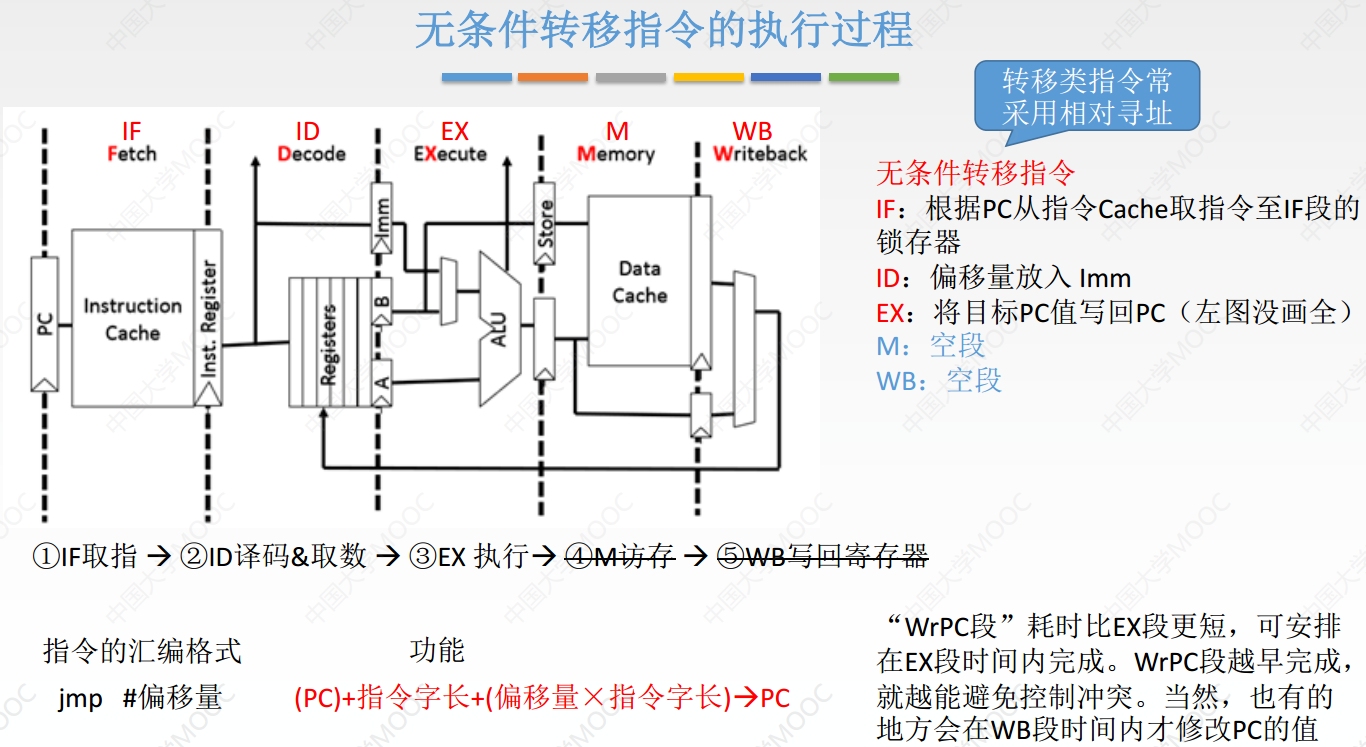

运算类指令、LOAD指令、STORE指令、条件转移指令、无条件转移指令

点击查看执行过程

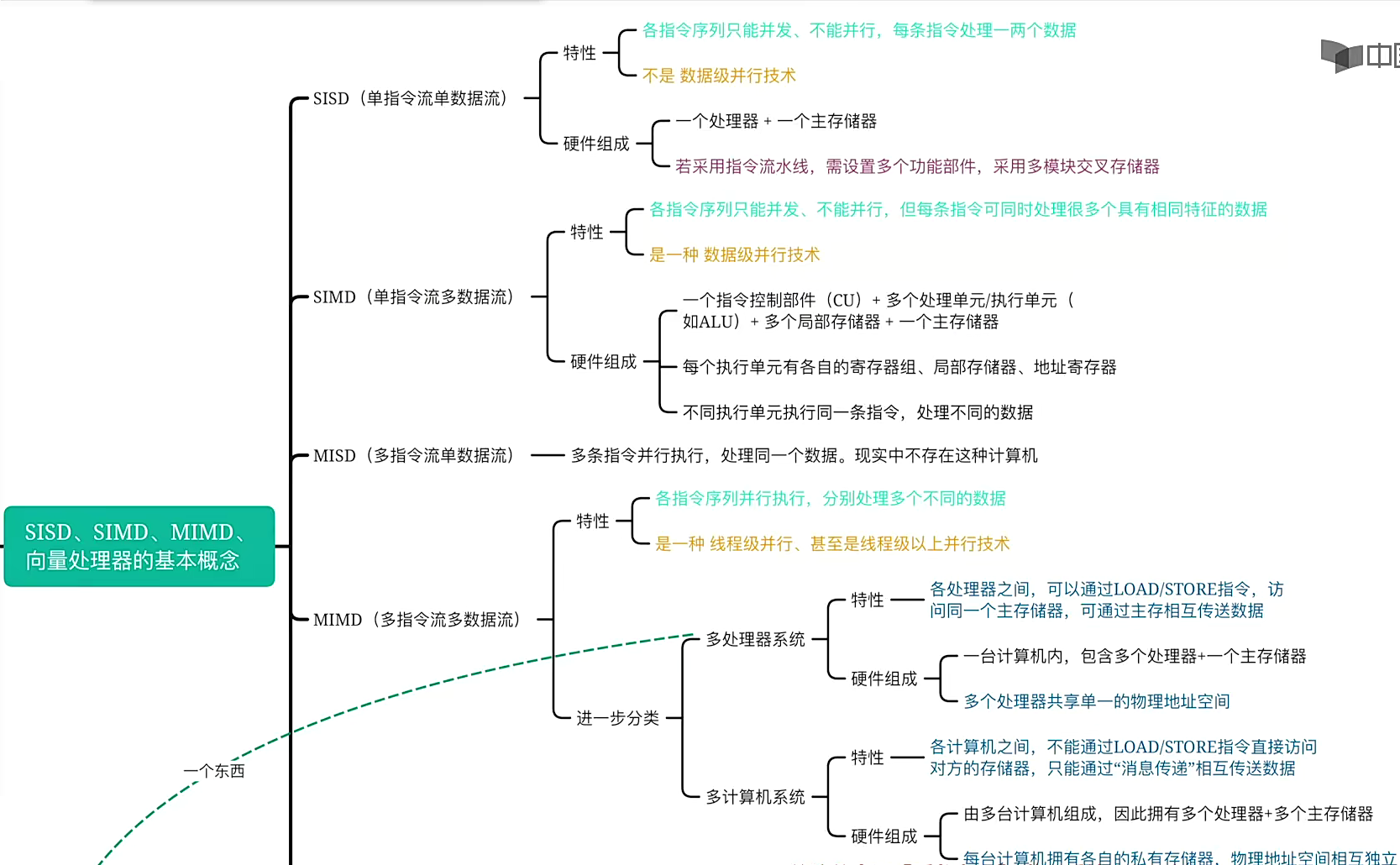

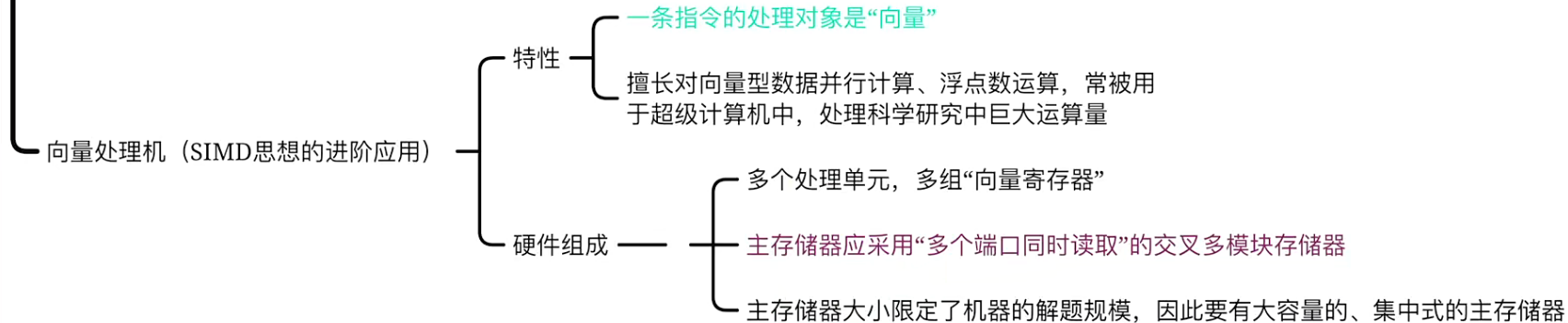

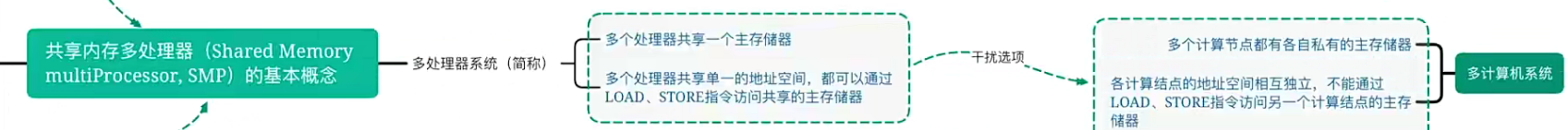

多处理器

SISD,SIMD,MIMD,向量处理器

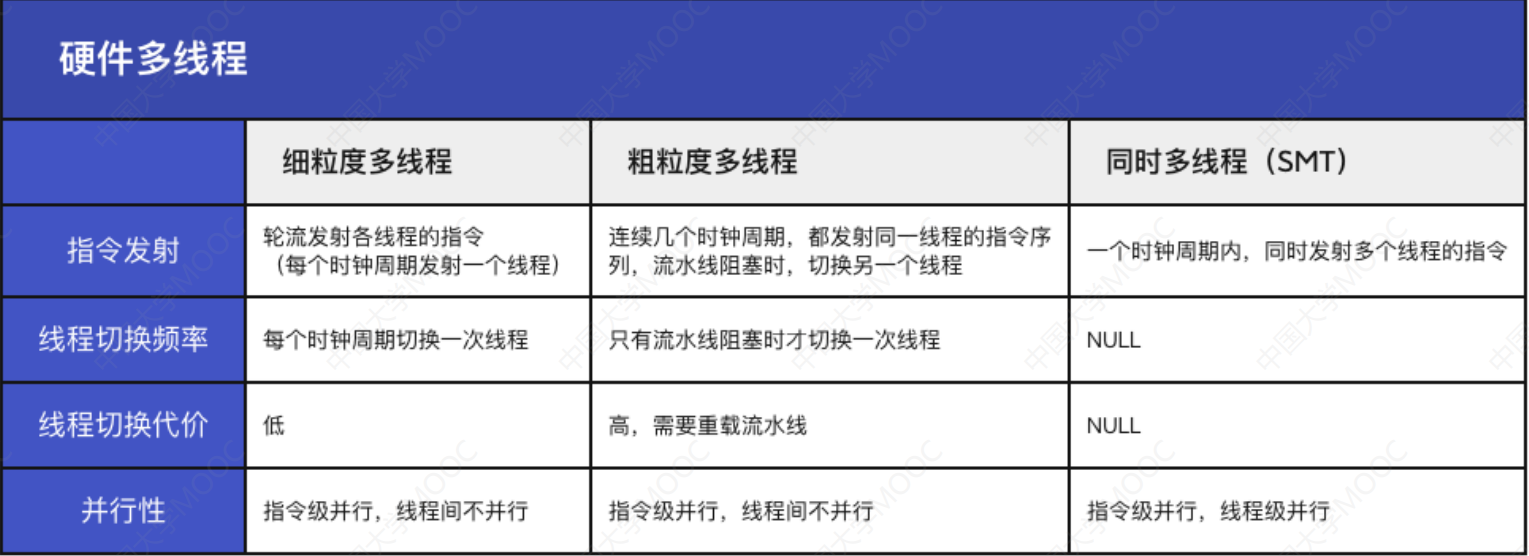

硬件多线程

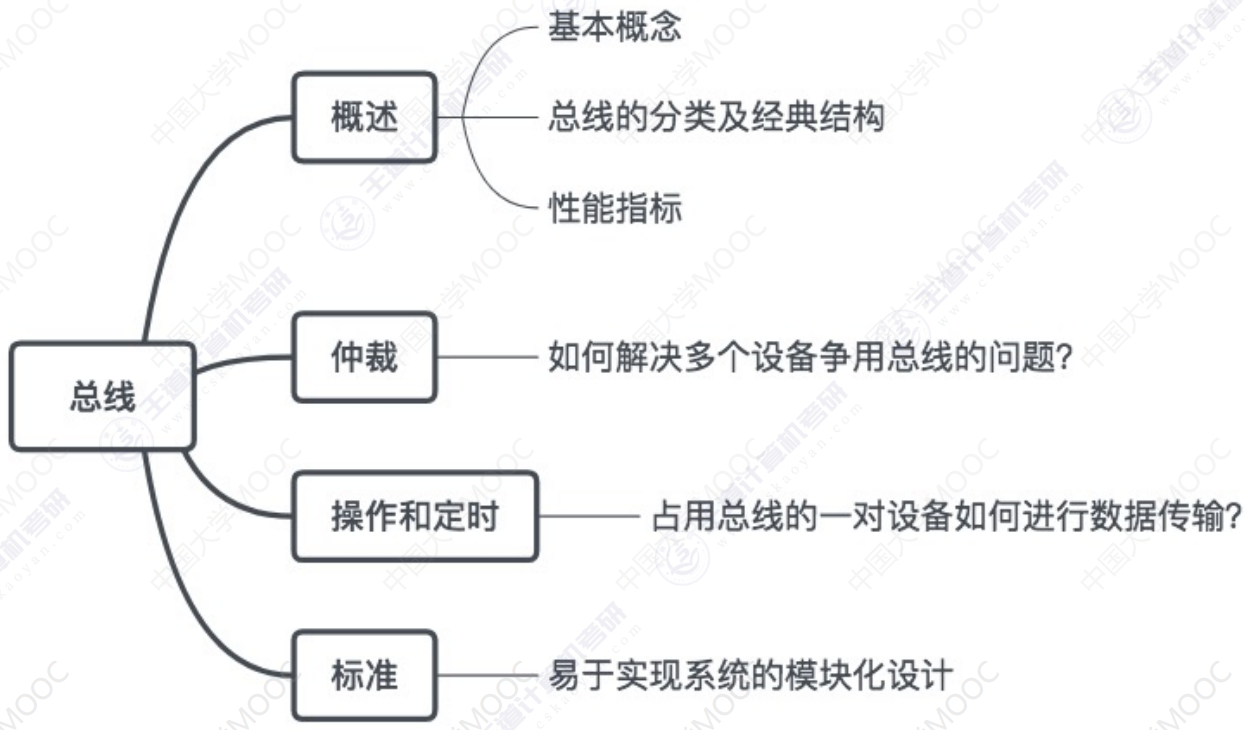

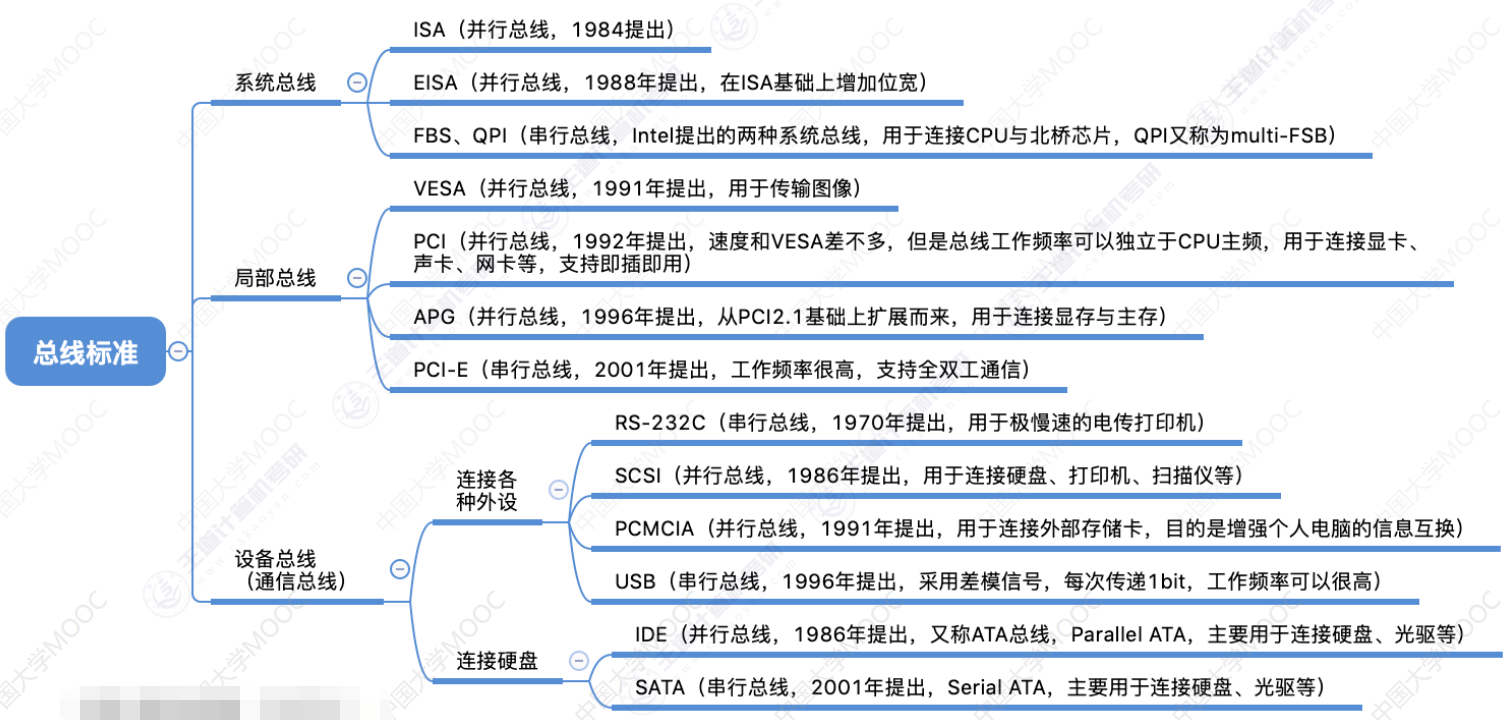

6️⃣: 总线

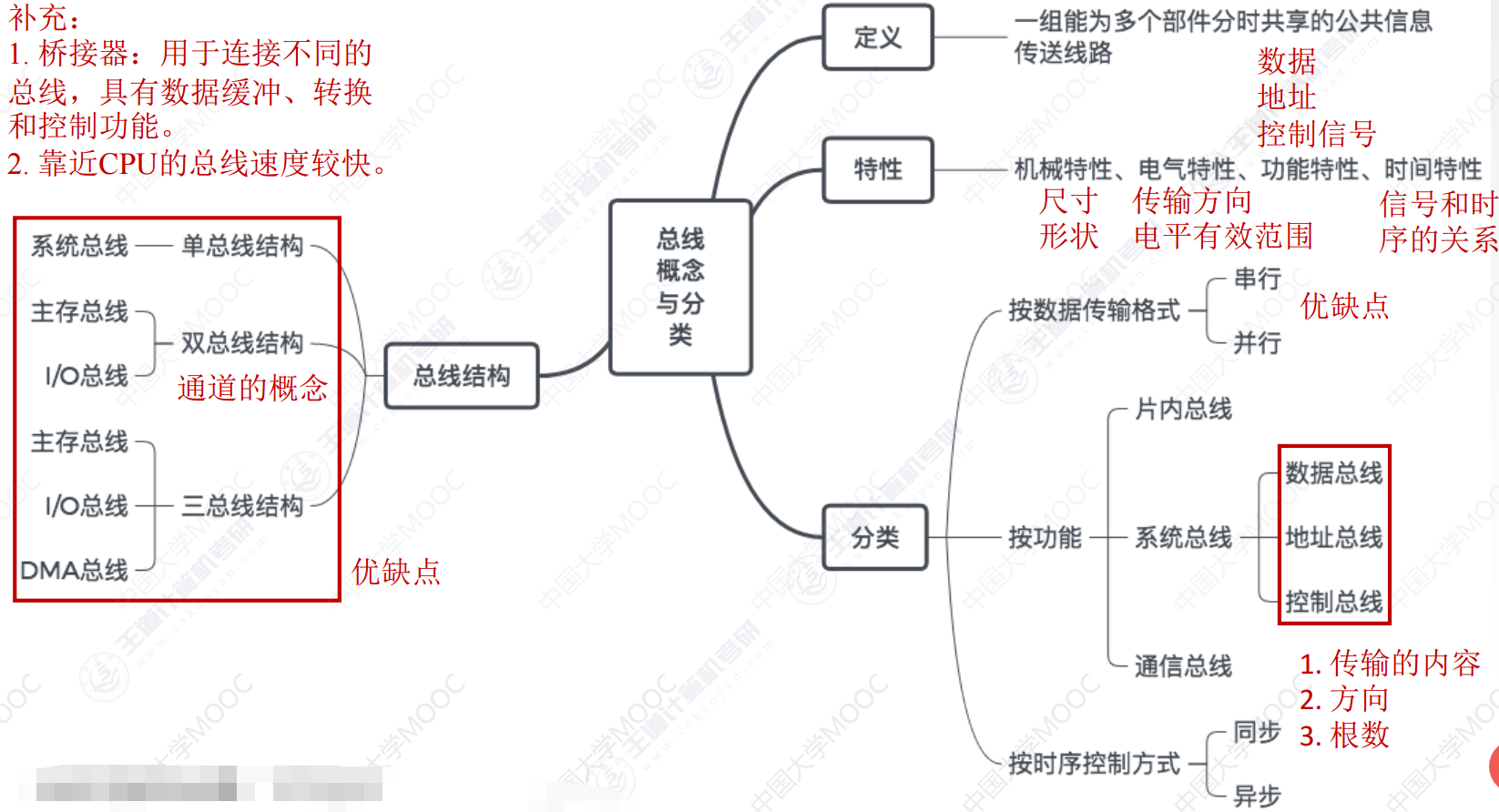

总线概念与分类

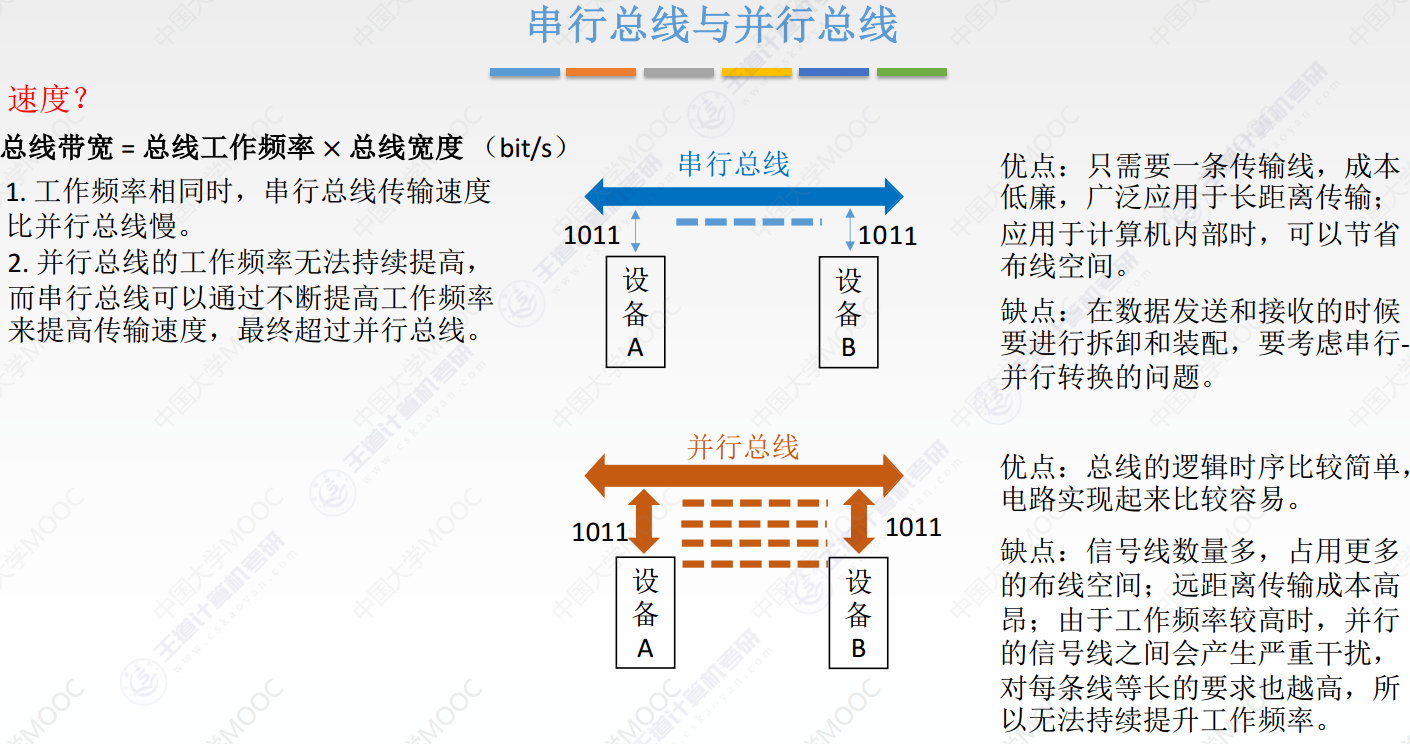

补充:串行总线与并行总线

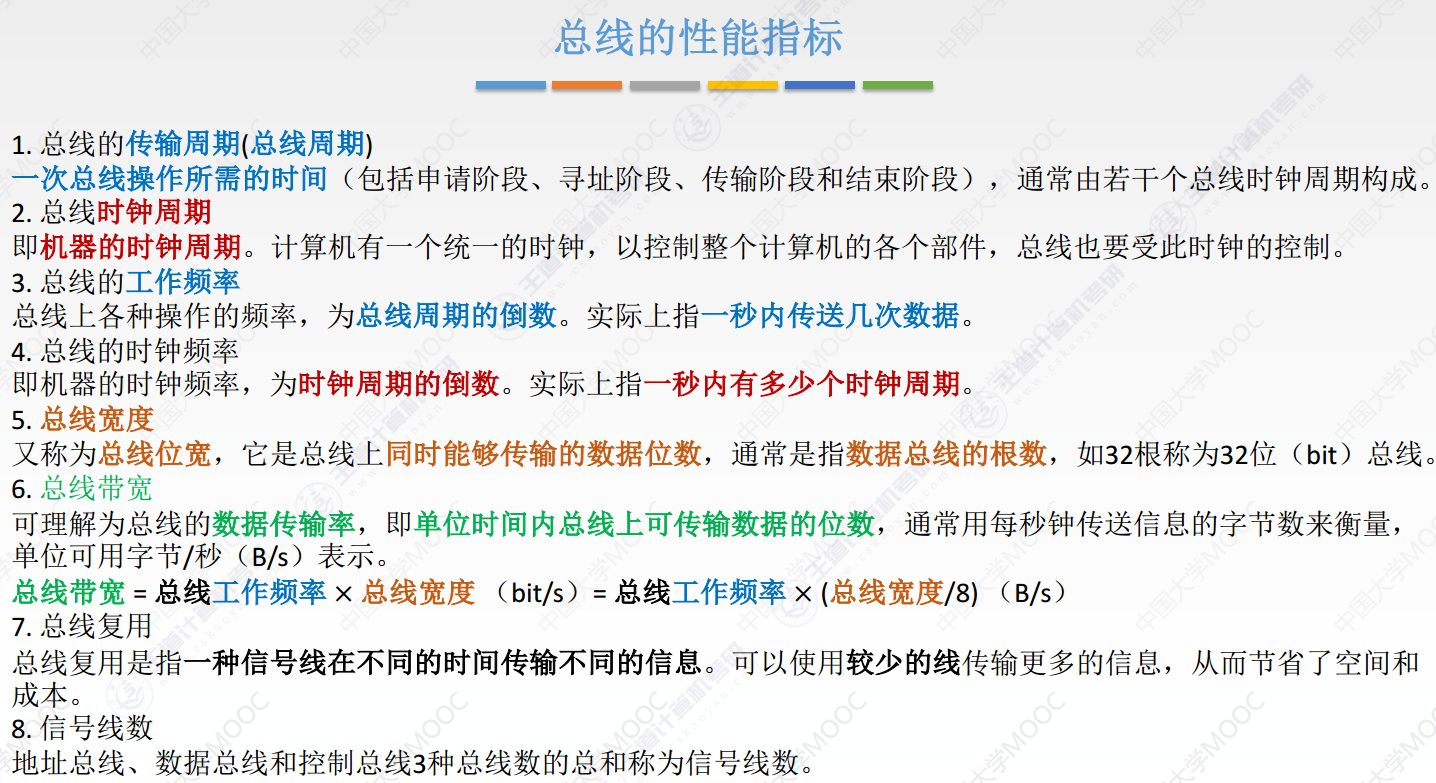

总线的性能指标

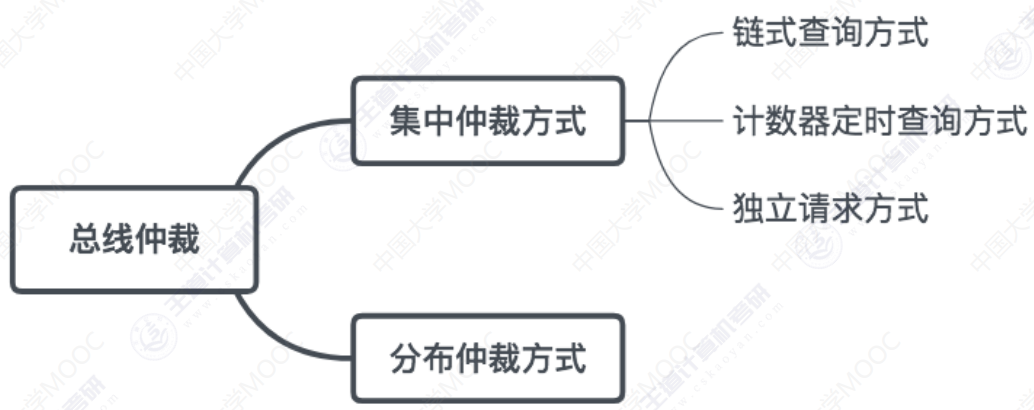

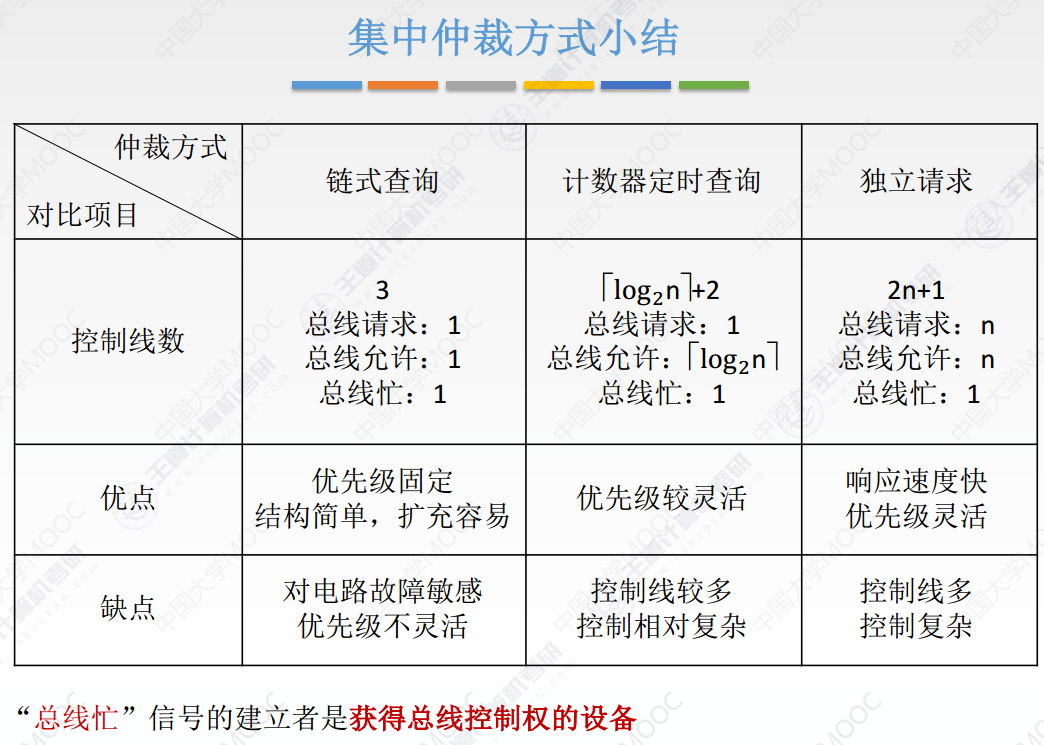

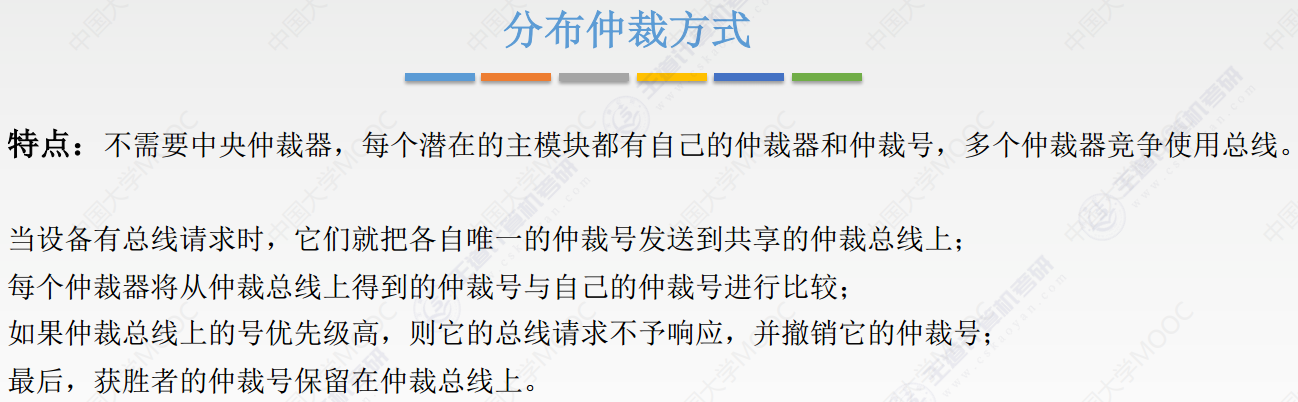

总线仲裁(已删,没看)

集中仲裁, 分布仲裁

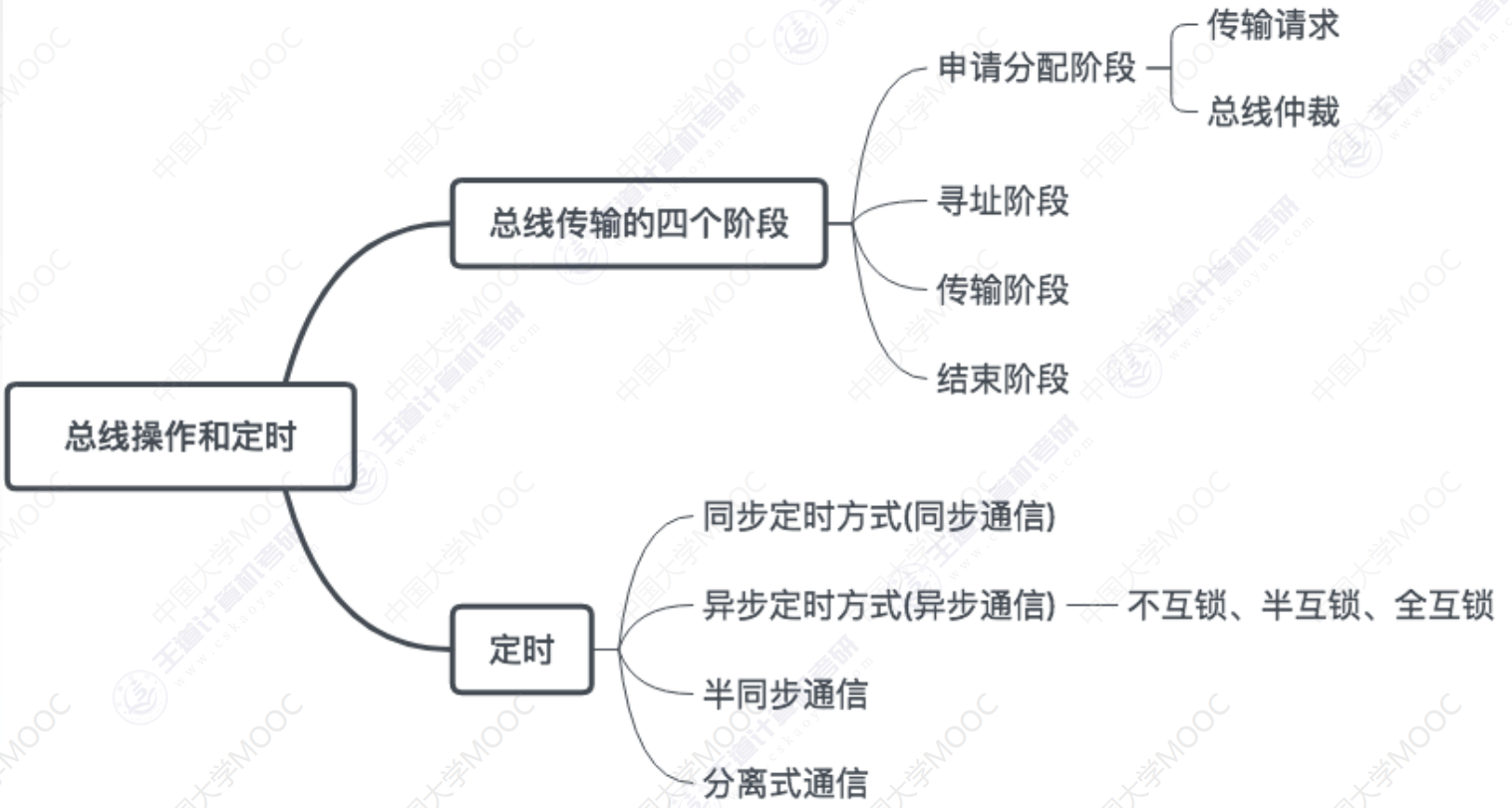

总线操作与定时

总线标准(已删,没看)

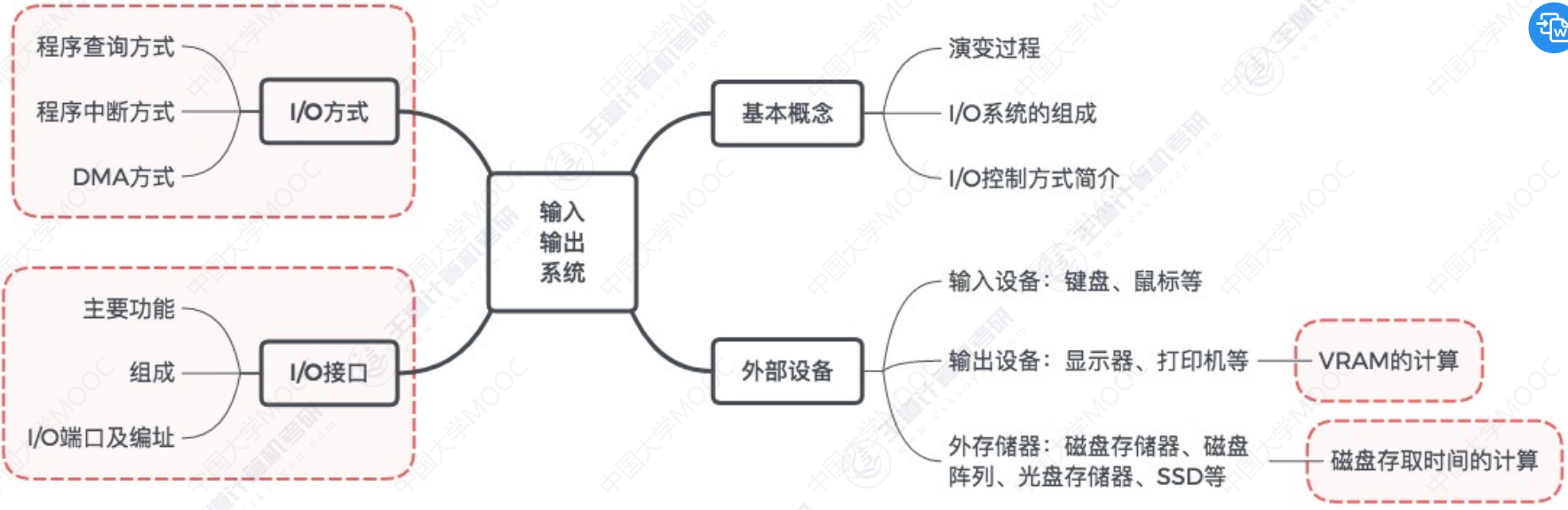

7️⃣: 输入/输出系统

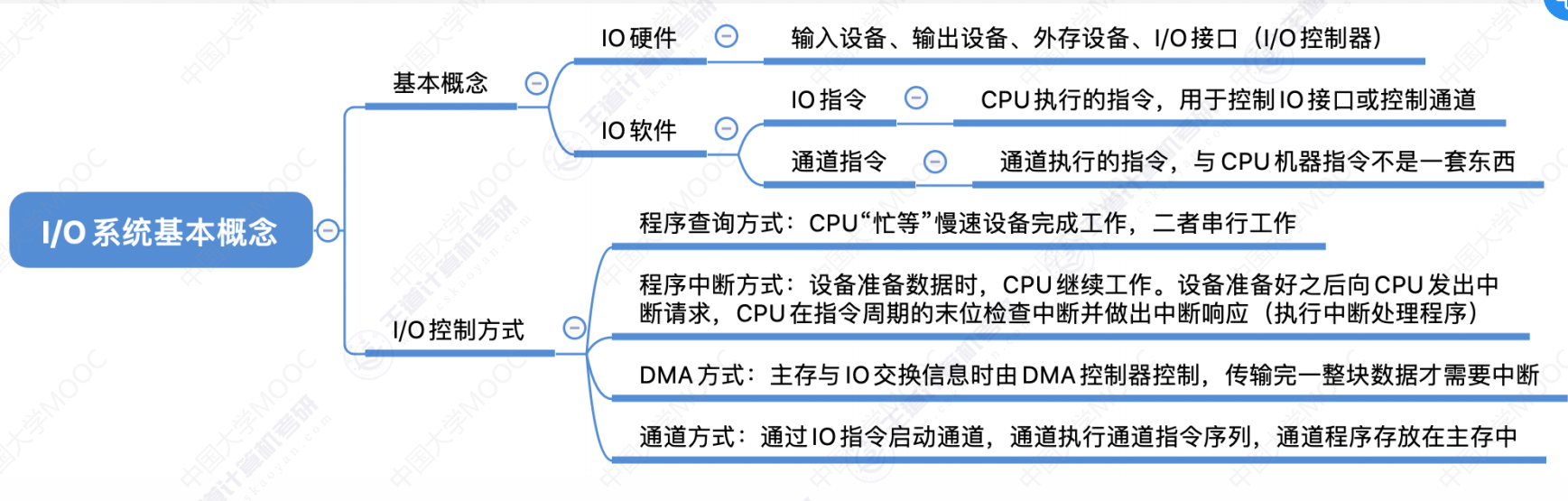

I/O系统基本概念

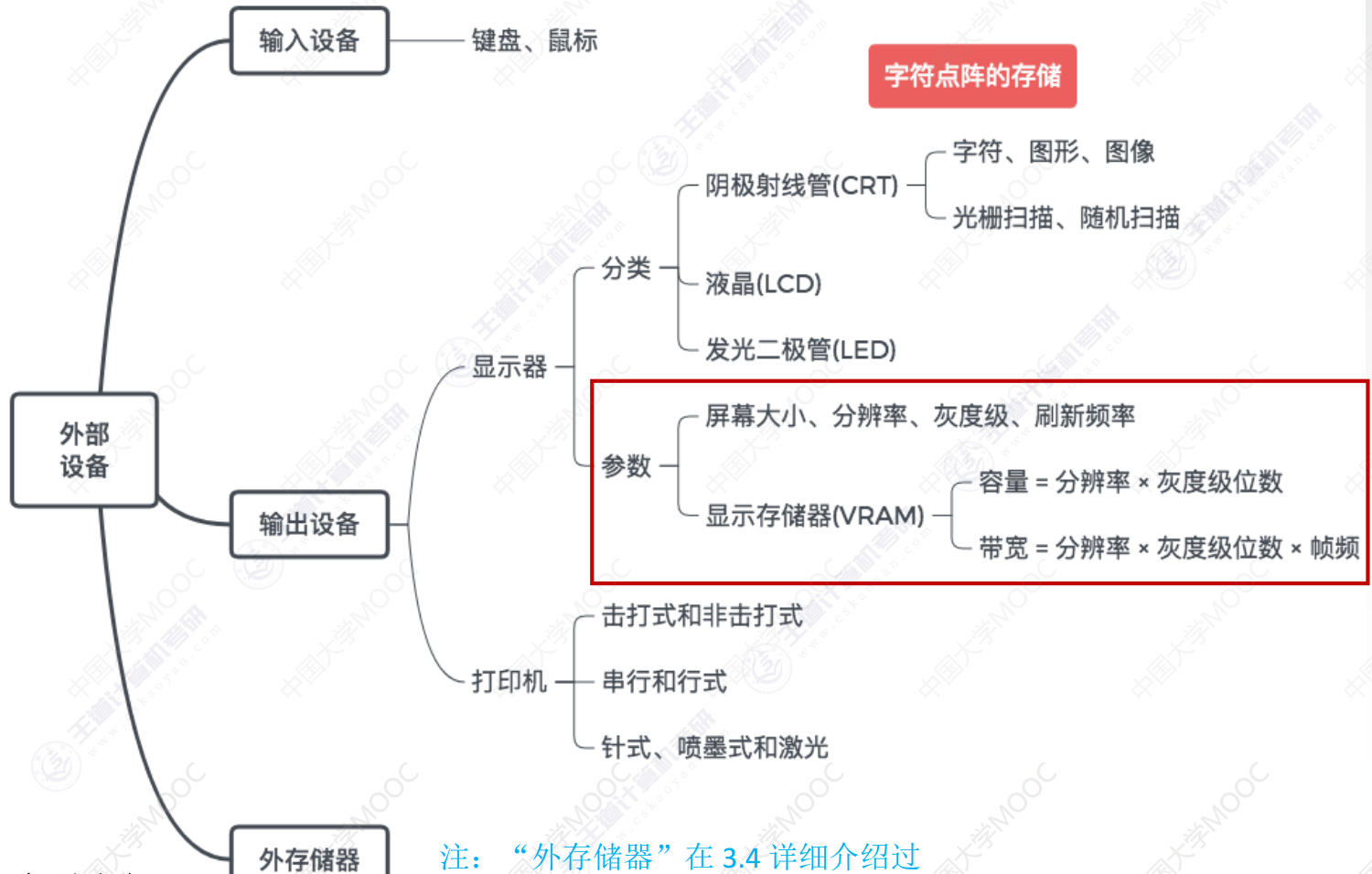

外部设备

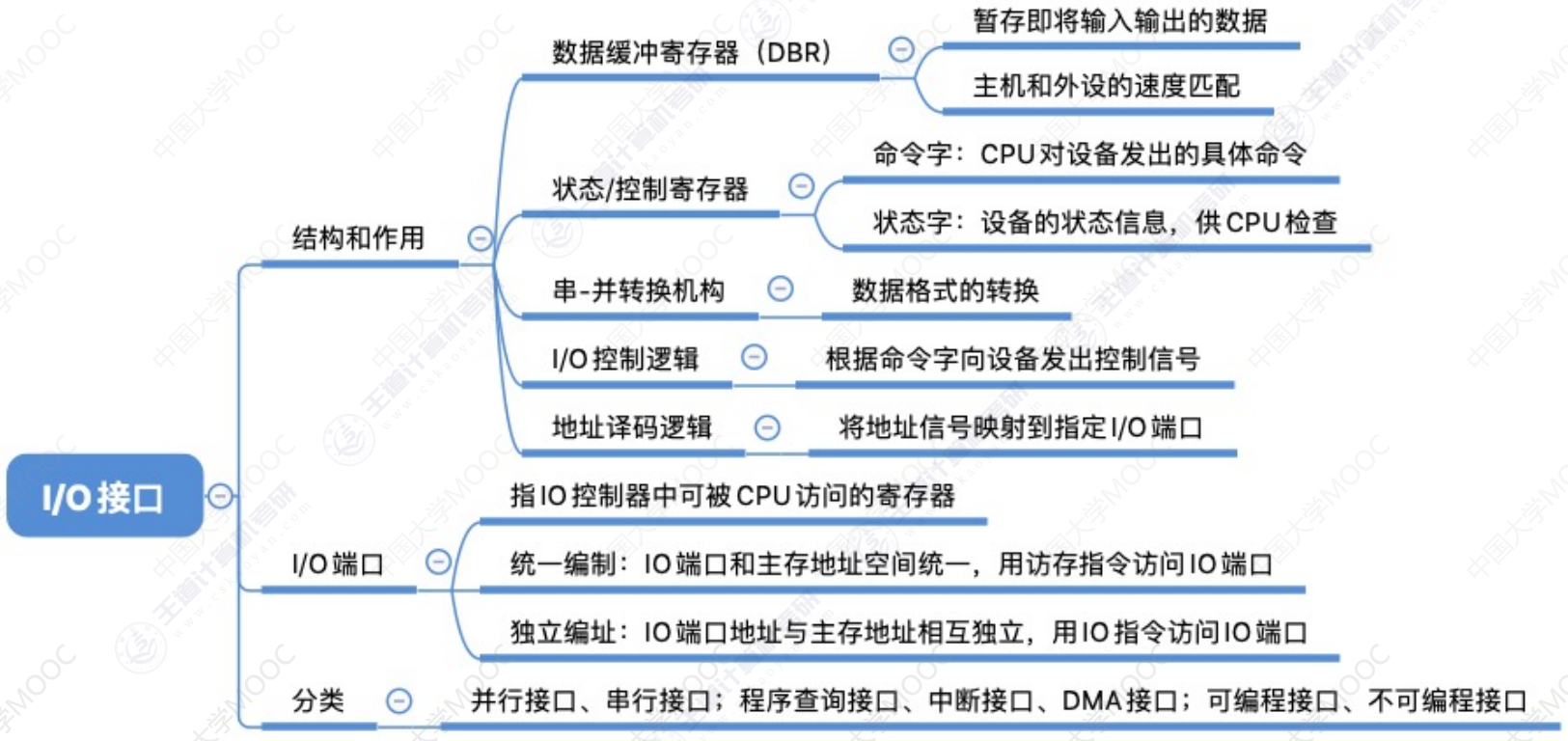

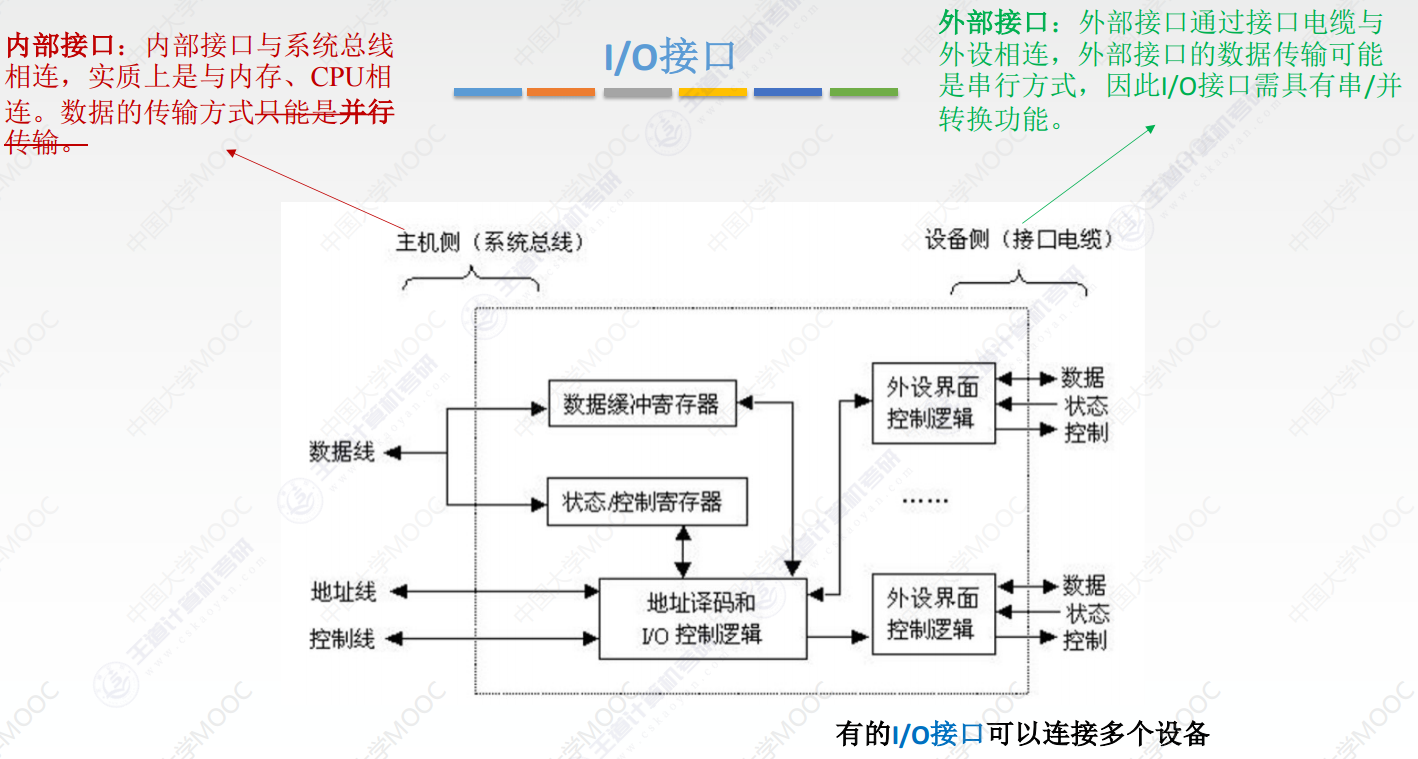

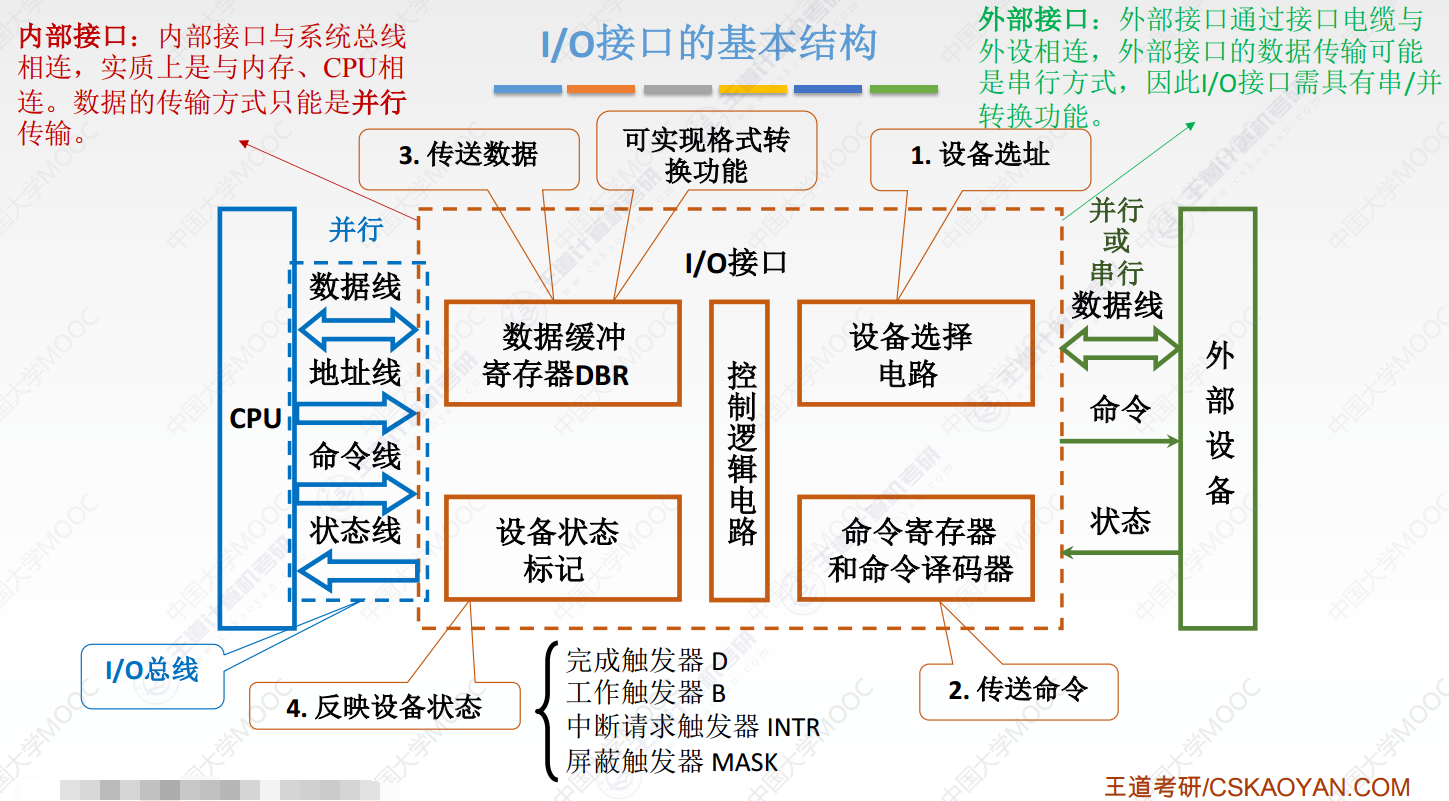

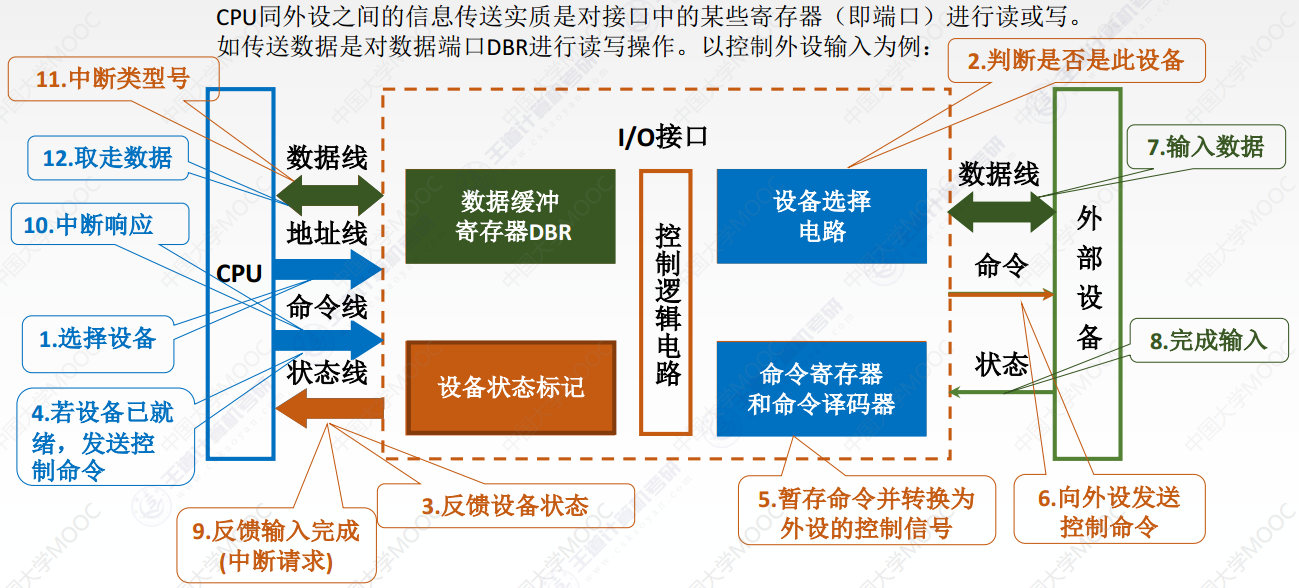

I/O接口

基本结构

点击查看

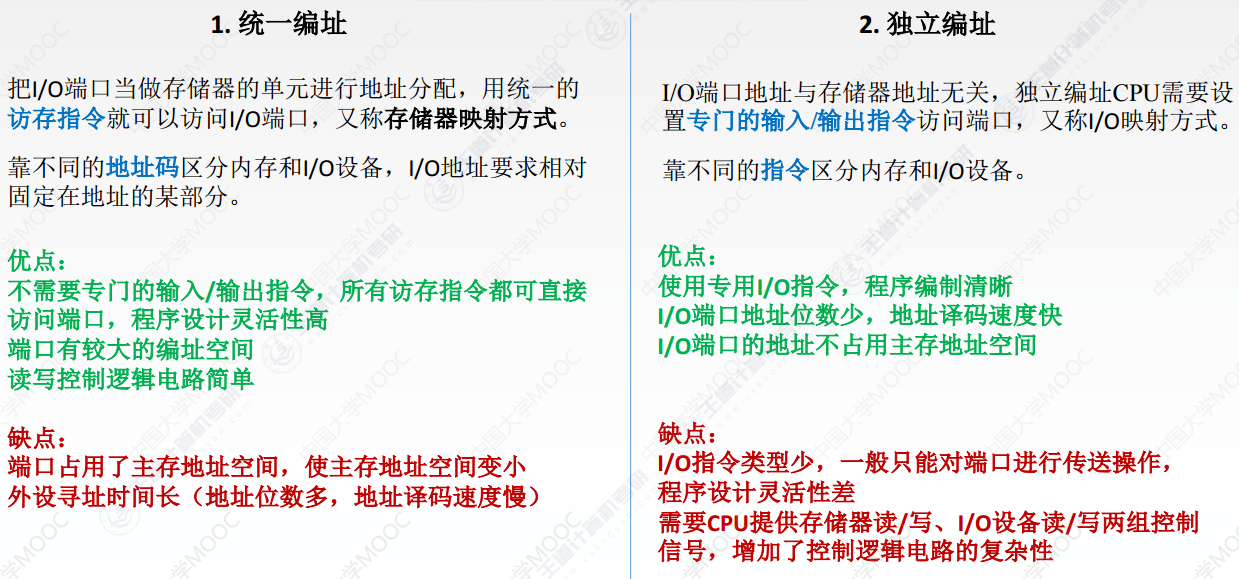

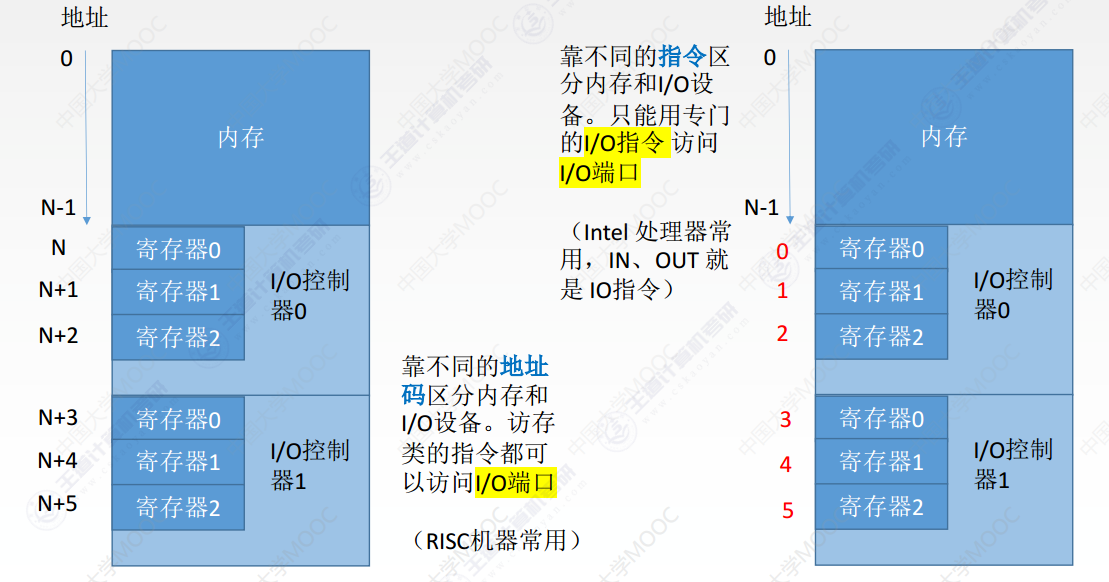

统一编址vs独立编址

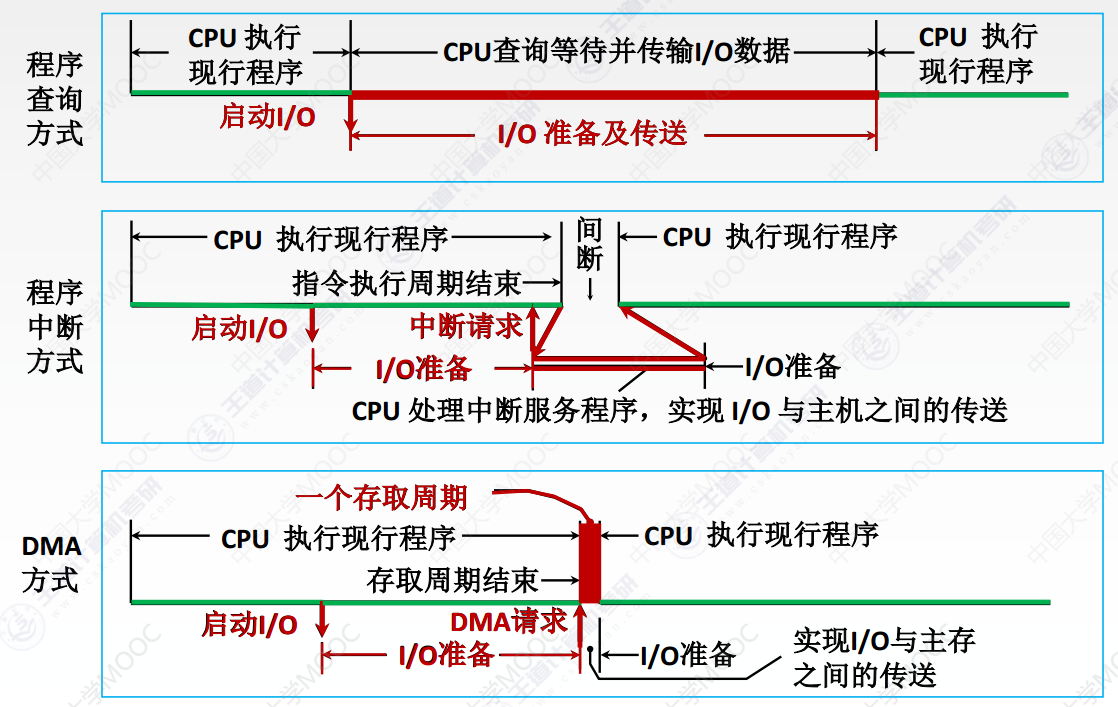

I/O方式

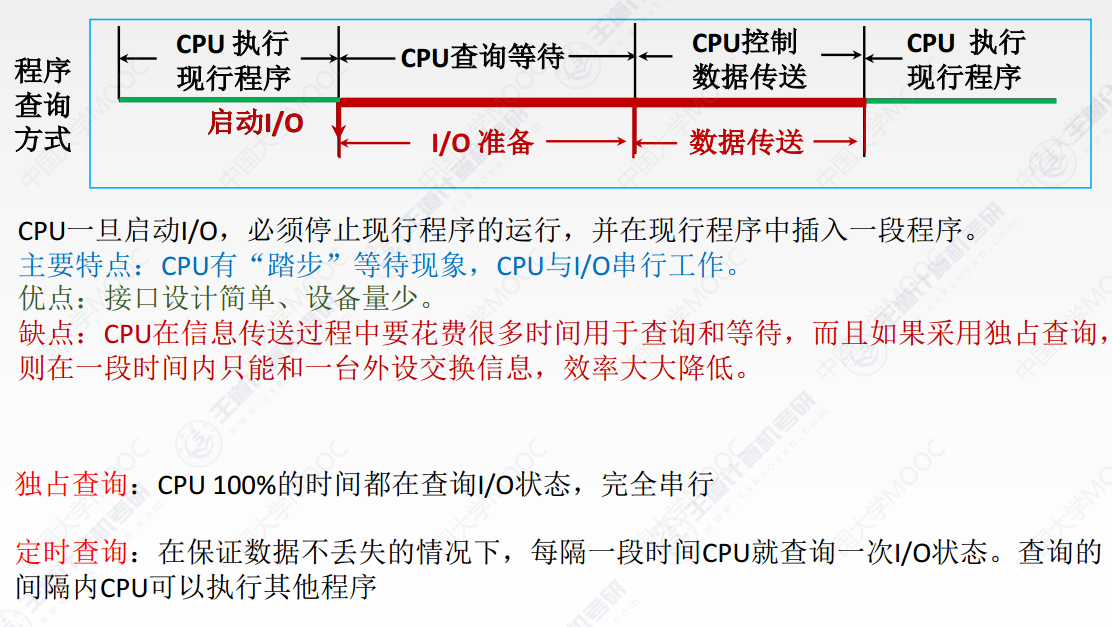

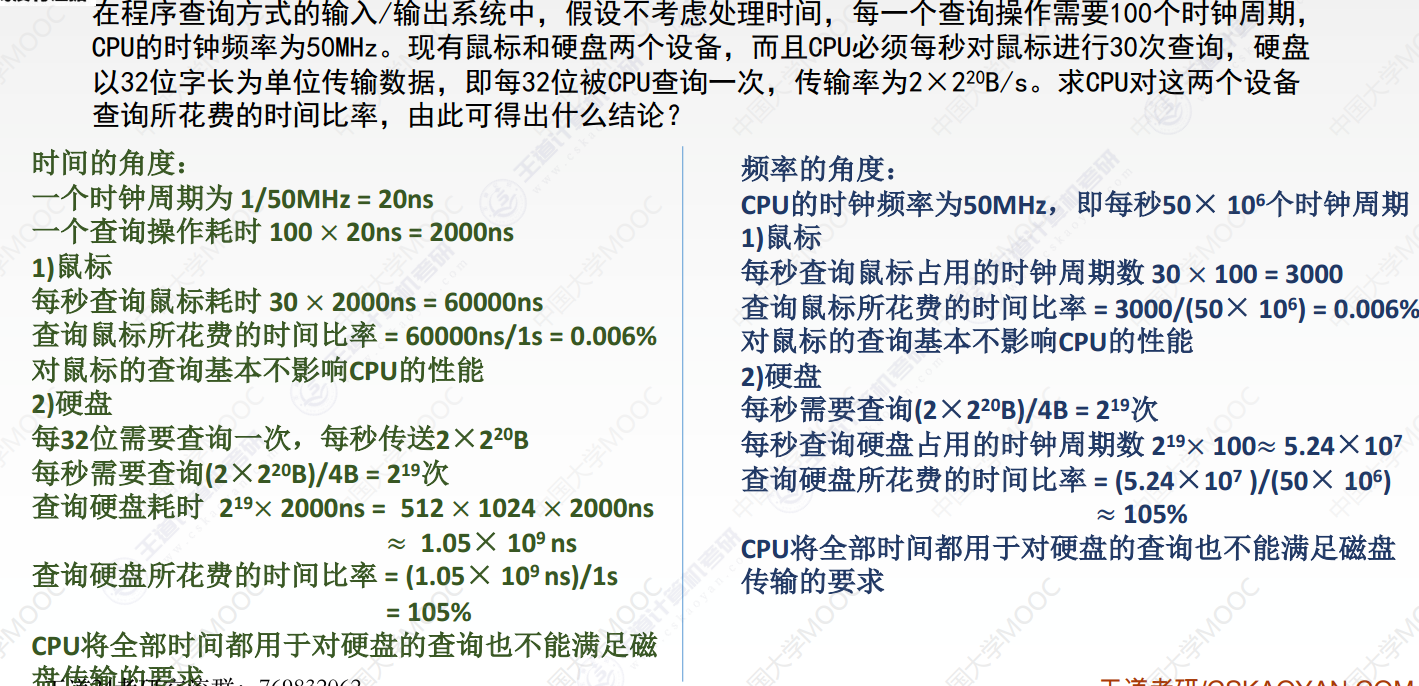

程序查询方式

例题

例题

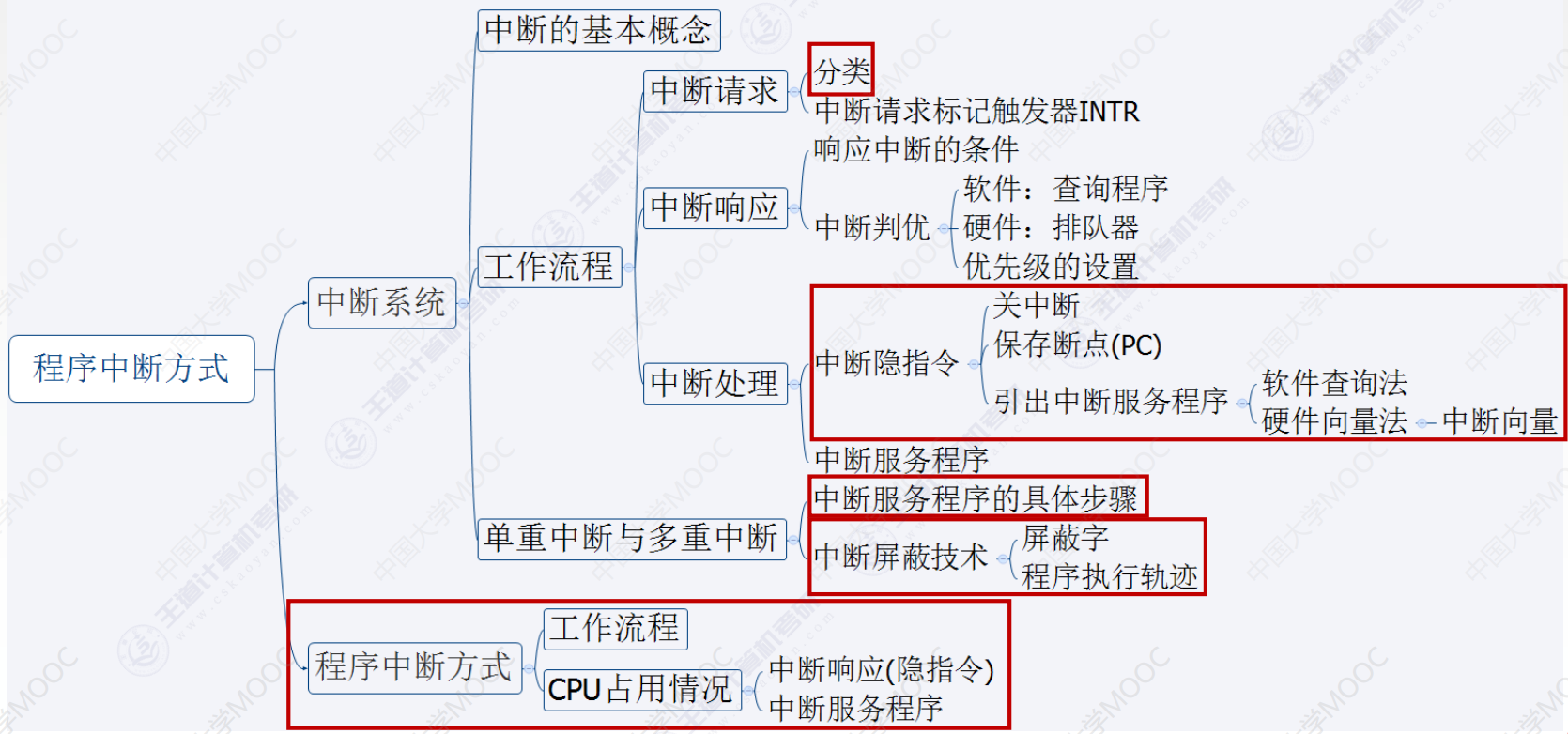

程序中断方式

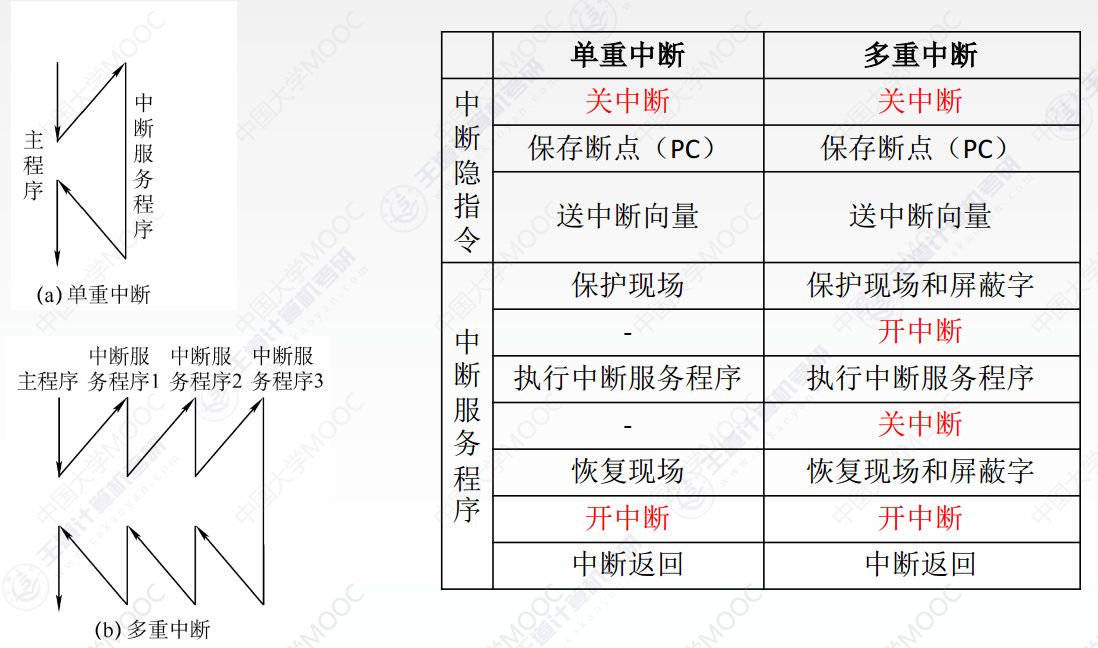

单重中断vs多重中断

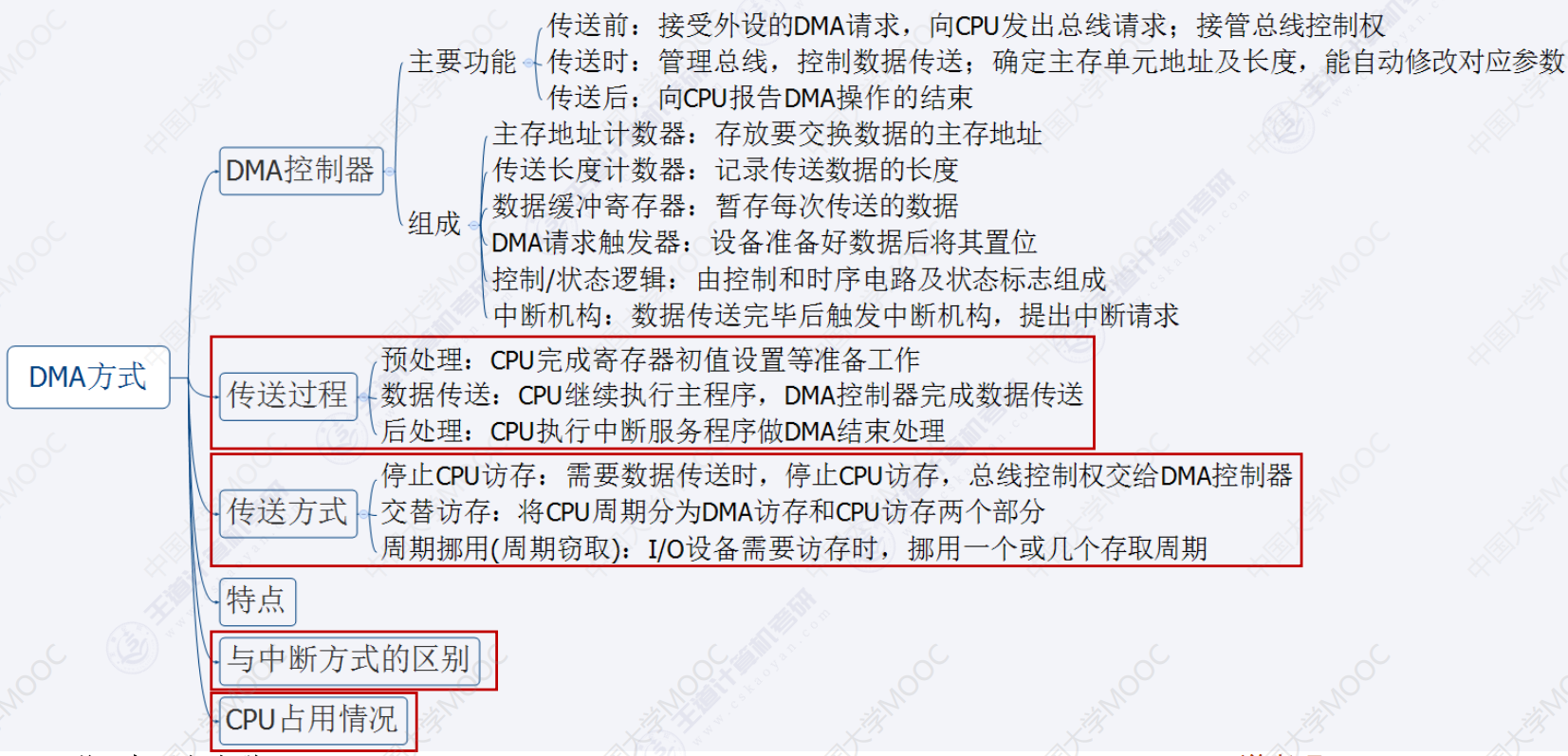

DMA方式

🚀各章节导图总览

一:计算机系统概论

二:数据的表示与运算

三:存储系统

本文来自博客园,作者:泥烟,CSDN同名, 转载请注明原文链接:https://www.cnblogs.com/Knight02/articles/408-jz-KnowledgeMap.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号