基于状态机的简易RISC CPU设计

目录

一、什么是CPU?

二、RISC CPU结构

1.时钟发生器2.指令寄存器3.累加器4.RISC CPU算术逻辑运算单元5.数据控制器6.状态控制器7.程序计数器8.地址多路器9.外围模块10.地址译码器

a.RAMb.ROM

三、RISC CPU中各部件的相互连接关系

四、RISC CPU和它的外围电路

五、RISC CPU的寻址方式和指令系统

六、RISC CPU的操作和时序

正文

一、什么是CPU?

CPU 即中央处理单元的英文缩写,它是计算机的核心部件。计算机进行信息处理可分为两个步骤:- 将数据和程序(即指令序列)输入到计算机的存储器中。

- 从第一条指令的地址起开始执行该程序,得到所需结果,结束运行。CPU的作用是协调并控制计算机的各个部件执行程序的指令序列,使其有条不紊地进行。因此它必须具有以下基本功能:

- a)取指令:当程序已在存储器中时,首先根据程序入口地址取出一条程序,为此要发出指令地址及控制信号。

- b)分析指令:即指令译码。是对当前取得的指令进行分析,指出它要求什么操作,并产生相应的操作控制命令。

- c)执行指令:根据分析指令时产生的“操作命令”形成相应的操作控制信号序列,通过运算器,存储器及输入/输出设备的执行,实现每条指令的功能,其中包括对运算结果的处理以及下条指令地址的形成。

将其功能进一步细化,可概括如下:

- 能对指令进行译码并执行规定的动作;

- 可以进行算术和逻辑运算;

- 能与存储器,外设交换数据;

- 提供整个系统所需要的控制;

尽管各种CPU的性能指标和结构细节各不相同,但它们所能完成的基本功能相同。由功能分析,可知任何一种CPU内部结构至少应包含下面这些部件:

- 算术逻辑运算部件(ALU),

- 累加器,

- 程序计数器,

- 指令寄存器,译码器,

- 时序和控制部件。

RISC 即精简指令集计算机(Reduced Instruction Set Computer)的缩写。它是一种八十年代才出现的CPU,与一般的CPU 相比不仅只是简化了指令系统,而且是通过简化指令系统使计算机的结构更加简单合理,从而提高了运算速度。从实现的途径看,RISC_CPU与一般的CPU的不同处在于:它的时序控制信号形成部件是用硬布线逻辑实现的而不是采用微程序控制的方式。所谓硬布线逻辑也就是用触发器和逻辑门直接连线所构成的状态机和组合逻辑,故产生控制序列的速度比用微程序控制方式快得多,因为这样做省去了读取微指令的时间。RISC_CPU也包括上述这些部件,下面就详细介绍一个简化的用于教学目的的RISC_CPU的可综合VerilogHDL模型的设计和仿真过程。

二、RISC CPU结构

RISC_CPU是一个复杂的数字逻辑电路,但是它的基本部件的逻辑并不复杂。可把它分成八个基本部件:

- 时钟发生器

- 指令寄存器

- 累加器

- RISC CPU算术逻辑运算单元

- 数据控制器

- 状态控制器

- 程序计数器

- 地址多路器

1 时钟发生器

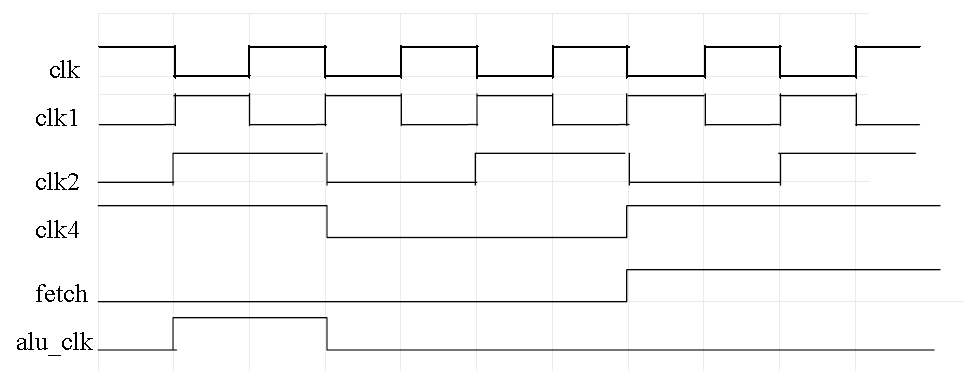

时钟发生器 clkgen 利用外来时钟信号clk 来生成一系列时钟信号clk1、fetch、alu_clk 送往CPU的其他部件。其中fetch是外来时钟 clk 的八分频信号。利用fetch的上升沿来触发CPU控制器开始执行一条指令,同时fetch信号还将控制地址多路器输出指令地址和数据地址。clk1信号用作指令寄存器、累加器、状态控制器的时钟信号。alu_clk 则用于触发算术逻辑运算单元。时钟发生器clkgen的波形见下图所示:

其VerilogHDL 程序见下面的模块:

1 module clk_gen (clk,reset,clk1,clk2,clk4,fetch,alu_clk); 2 input clk,reset; 3 output clk1,clk2,clk4,fetch,alu_clk; 4 wire clk,reset; 5 reg clk2,clk4,fetch,alu_clk; 6 reg[7:0] state; 7 parameter S1 = 8'b00000001, 8 S2 = 8'b00000010, 9 S3 = 8'b00000100, 10 S4 = 8'b00001000, 11 S5 = 8'b00010000, 12 S6 = 8'b00100000, 13 S7 = 8'b01000000, 14 S8 = 8'b10000000, 15 idle = 8'b00000000; 16 assign clk1 = ~clk; 17 18 always @(negedge clk) 19 if(reset) 20 begin 21 clk2 <= 0; 22 clk4 <= 1; 23 fetch <= 0; 24 alu_clk <= 0; 25 state <= idle; 26 end 27 else 28 begin 29 case(state) 30 S1: 31 begin 32 clk2 <= ~clk2; 33 alu_clk <= ~alu_clk; 34 state <= S2; 35 end 36 S2: 37 begin 38 clk2 <= ~clk2; 39 clk4 <= ~clk4; 40 alu_clk <= ~alu_clk; 41 state <= S3; 42 end 43 S3: 44 begin 45 clk2 <= ~clk2; 46 state <= S4; 47 end 48 S4: 49 begin 50 clk2 <= ~clk2; 51 clk4 <= ~clk4; 52 fetch <= ~fetch; 53 state <= S5; 54 end 55 S5: 56 begin 57 clk2 <= ~clk2; 58 state <= S6; 59 end 60 S6: 61 begin 62 clk2 <= ~clk2; 63 clk4 <= ~clk4; 64 state <= S7; 65 end 66 S7: 67 begin 68 clk2 <= ~clk2; 69 state <= S8; 70 end 71 S8: 72 begin 73 clk2 <= ~clk2; 74 clk4 <= ~clk4; 75 fetch <= ~fetch; 76 state <= S1; 77 end 78 idle: state <= S1; 79 default: state <= idle; 80 endcase 81 end 82 endmodule 83 //--------------------------------------------------------------------------------

2 指令寄存器

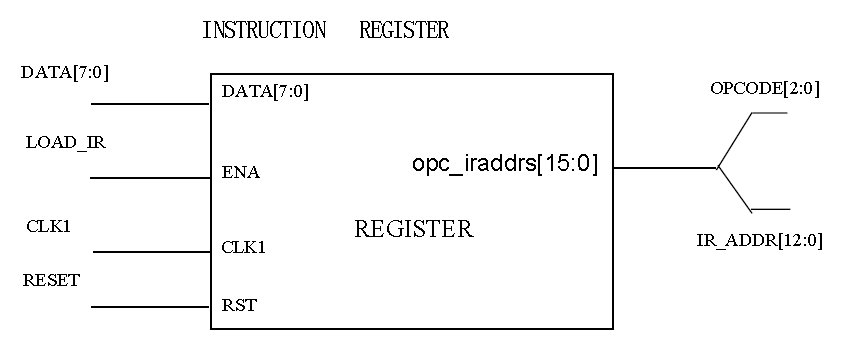

顾名思义,指令寄存器用于寄存指令。

指令寄存器的触发时钟是clk1,在clk1的正沿触发下,寄存器将数据总线送来的指令存入高8位或低8位寄存器中。但并不是每个clk1的上升沿都寄存数据总线的数据,因为数据总线上有时传输指令,有时传输数据。什么时候寄存,什么时候不寄存由CPU状态控制器的load_ir信号控制。load_ir信号通过ena 口输入到指令寄存器。复位后,指令寄存器被清为零。

每条指令为2个字节,即16位。高3位是操作码,低13位是地址。(CPU的地址总线为13位,寻址空间为8K字节。)本设计的数据总线为8位,所以每条指令需取两次。先取高8位,后取低8位。而当前取的是高8位还是低8位,由变量state记录。state为零表示取的高8位,存入高8位寄存器,同时将变量state置为1。下次再寄存时,由于state为1,可知取的是低8位,存入低8位寄存器中。

指令寄存器的触发时钟是clk1,在clk1的正沿触发下,寄存器将数据总线送来的指令存入高8位或低8位寄存器中。但并不是每个clk1的上升沿都寄存数据总线的数据,因为数据总线上有时传输指令,有时传输数据。什么时候寄存,什么时候不寄存由CPU状态控制器的load_ir信号控制。load_ir信号通过ena 口输入到指令寄存器。复位后,指令寄存器被清为零。

每条指令为2个字节,即16位。高3位是操作码,低13位是地址。(CPU的地址总线为13位,寻址空间为8K字节。)本设计的数据总线为8位,所以每条指令需取两次。先取高8位,后取低8位。而当前取的是高8位还是低8位,由变量state记录。state为零表示取的高8位,存入高8位寄存器,同时将变量state置为1。下次再寄存时,由于state为1,可知取的是低8位,存入低8位寄存器中。

其VerilogHDL 程序见下面的模块:

1 //--------------------------------------------------------------- 2 module register(opc_iraddr,data,ena,clk1,rst); 3 output [15:0] opc_iraddr; 4 input [7:0] data; 5 input ena, clk1, rst; 6 reg [15:0] opc_iraddr; 7 reg state; 8 9 always @(posedge clk1) 10 begin 11 if(rst) 12 begin 13 opc_iraddr<=16'b0000_0000_0000_0000; 14 state<=1'b0; 15 end 16 else 17 begin 18 if(ena) //如果加载指令寄存器信号load_ir到来, 19 begin //分两个时钟每次8位加载指令寄存器 20 casex(state) //先高字节,后低字节 21 1’b0: begin 22 opc_iraddr[15:8]<=data; 23 state<=1; 24 end 25 1’b1: begin 26 opc_iraddr[7:0]<=data; 27 state<=0; 28 end 29 default: begin 30 opc_iraddr[15:0]<=16'bxxxxxxxxxxxxxxxx; 31 state<=1'bx; 32 end 33 endcase 34 end 35 else 36 state<=1'b0; 37 end 38 end 39 endmodule 40 //--------------------------------------------------------

3.累加器

累加器用于存放当前的结果,它也是双目运算其中一个数据来源。复位后,累加器的值是零。当累加器通过ena口收到来自CPU状态控制器load_acc信号时,在clk1时钟正跳沿时就收到来自于数据总线的数据。

其VerilogHDL 程序见下面的模块:

其VerilogHDL 程序见下面的模块:

1 //-------------------------------------------------------------- 2 module accum( accum, data, ena, clk1, rst); 3 output[7:0]accum; 4 input[7:0]data; 5 input ena,clk1,rst; 6 reg[7:0]accum; 7 8 always@(posedge clk1) 9 begin 10 if(rst) 11 accum<=8'b0000_0000; //Reset 12 else 13 if(ena) //当CPU状态控制器发出load_acc信号 14 accum<=data; //Accumulate 15 end 16 endmodule

4.算术运算器

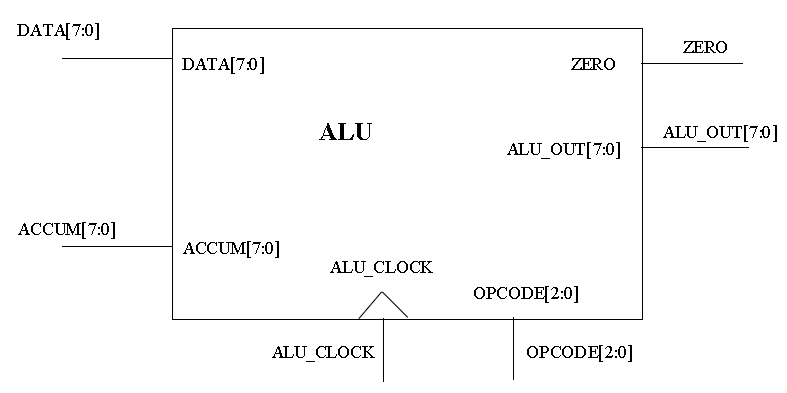

算术逻辑运算单元 根据输入的8种不同操作码分别实现相应的加、与、异或、跳转等8种基本操作运算。利用这几种基本运算可以实现很多种其它运算以及逻辑判断等操作。

其VerilogHDL 程序见下面的模块:

其VerilogHDL 程序见下面的模块:

1 //------------------------------------------------------------------------------ 2 module alu (alu_out, zero, data, accum, alu_clk, opcode); 3 output [7:0]alu_out; 4 output zero; 5 input [7:0] data, accum; 6 input [2:0] opcode; 7 input alu_clk; 8 reg [7:0] alu_out; 9 10 parameter HLT =3’b000, 11 SKZ =3’b001, 12 ADD =3’b010, 13 ANDD =3’b011, 14 XORR =3’b100, 15 LDA =3’b101, 16 STO =3’b110, 17 JMP =3’b111; 18 19 assign zero = !accum; 20 always @(posedgealu_clk) 21 begin //操作码来自指令寄存器的输出opc_iaddr<15..0>的低3位 22 casex (opcode) 23 HLT: alu_out<=accum; 24 SKZ: alu_out<=accum; 25 ADD: alu_out<=data+accum; 26 ANDD: alu_out<=data&accum; 27 XORR: alu_out<=data^accum; 28 LDA: alu_out<=data; 29 STO: alu_out<=accum; 30 JMP: alu_out<=accum; 31 default: alu_out<=8'bxxxx_xxxx; 32 endcase 33 end 34 endmodule 35 //----------------------------------------------------------------------------

5.数据控制器

数据控制器的作用是控制累加器数据输出,由于数据总线是各种操作时传送数据的公共通道,不同的情况下传送不同的内容。有时要传输指令,有时要传送RAM区或接口的数据。累加器的数据只有在需要往RAM区或端口写时才允许输出,否则应呈现高阻态,以允许其它部件使用数据总线。 所以任何部件往总线上输出数据时,都需要一控制信号。而此控制信号的启、停,则由CPU状态控制器输出的各信号控制决定。数据控制器何时输出累加器的数据则由状态控制器输出的控制信号datactl_ena决定。其VerilogHDL 程序见下面的模块:

1 //-------------------------------------------------------------------- 2 module datactl (data,in,data_ena); 3 output [7:0]data; 4 input [7:0]in; 5 input data_ena; 6 7 assign data = (data_ena)? In : 8'bzzzz_zzzz; 8 9 endmodule 10 //--------------------------------------------------------------------

6.地址多路器

地址多路器用于选择输出的地址是PC(程序计数)地址还是数据/端口地址。每个指令周期的前4个时钟周期用于从ROM中读取指令,输出的应是PC地址。后4个时钟周期用于对RAM或端口的读写,该地址由指令中给出。地址的选择输出信号由时钟信号的8分频信号fetch提供。 其VerilogHDL 程序见下面的模块:

其VerilogHDL 程序见下面的模块:

状态机是CPU的控制核心,用于产生一系列的控制信号,启动或停止某些部件。CPU何时进行读指令读写I/O端口,RAM区等操作,都是由状态机来控制的。状态机的当前状态,由变量state记录,state的值就是当前这个指令周期中已经过的时钟数(从零计起)。

指令周期是由8个时钟周期组成,每个时钟周期都要完成固定的操作。

FFFFH---1800H RAM

1800H---0000H ROM

1 //------------------------------------------------------------------------------ 2 module adr(addr,fetch,ir_addr,pc_addr); 3 output [12:0] addr; 4 input [12:0] ir_addr, pc_addr; 5 input fetch; 6 7 8 assign addr = fetch? pc_addr : ir_addr; 9 10 11 endmodule 12 //------------------------------------------------------------------------------

7.程序计数器

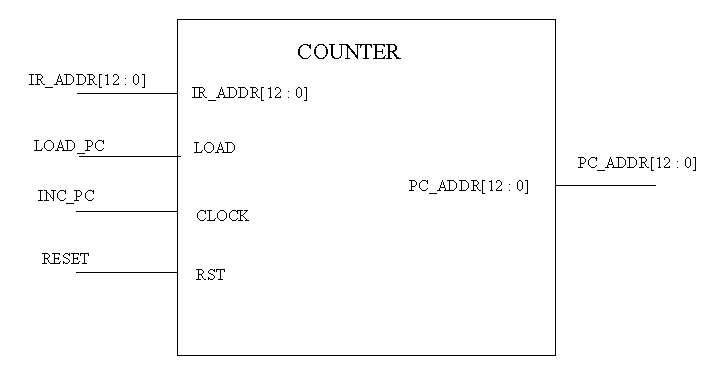

程序计数器用于提供指令地址。以便读取指令,指令按地址顺序存放在存储器中。有两种途径可形成指令地址:其一是顺序执行的情况,其二是遇到要改变顺序执行程序的情况,例如执行JMP指令后,需要形成新的指令地址。复位后,指令指针为零,即每次CPU重新启动将从ROM的零地址开始读取指令并执行。每条指令执行完需2个时钟,这时pc_addr已被增2,指向下一条指令。(因为每条指令占两个字节。)如果正执行的指令是跳转语句,这时CPU状态控制器将会输出load_pc信号,通过load口进入程序计数器。程序计数器(pc_addr)将装入目标地址(ir_addr),而不是增2。其VerilogHDL 程序见下面的模块:

1 //------------------------------------------------------------------------------ 2 module counter ( pc_addr, ir_addr, load, clock, rst); 3 output [12:0] pc_addr; 4 input [12:0] ir_addr; 5 input load, clock, rst; 6 reg [12:0] pc_addr; 7 8 always @( posedge clock or posedge rst ) 9 begin 10 if(rst) 11 pc_addr<=13'b0_0000_0000_0000; 12 else 13 if(load) 14 pc_addr<=ir_addr; 15 else 16 pc_addr <= pc_addr + 1; 17 end 18 endmodule 19 //------------------------------------------------------------------------------

8.状态控制器

状态控制器由两部分组成:

状态控制器的VerilogHDL程序见下面模块:

- 状态机(上图中的MACHINE部分)

- 状态控制器(上图中的MACHINECTL部分)

状态控制器的VerilogHDL程序见下面模块:

1 //------------------------------------------------------------------------------ 2 module machinectl( ena, fetch, rst); 3 output ena; 4 input fetch, rst; 5 reg ena; 6 always @(posedge fetch or posedge rst) 7 8 9 begin 10 if(rst) 11 ena<=0; 12 else 13 ena<=1; 14 end 15 endmodule 16 //------------------------------------------------------------------------------

- 第0个时钟,因为CPU状态控制器的输出:rd和load_ir为高电平,其余均为低电平。指令寄存器寄存由ROM送来的高8位指令代码。

- 第1个时钟,与上一时钟相比只是inc_pc从0变为1故PC增1,ROM送来低8位指令代码,指令寄存器寄存该8位代码。

- 第2个时钟,空操作。

- 第3个时钟,PC增1,指向下一条指令。若操作符为HLT,则输出信号HLT为高。如果操作符不为HLT,除了PC增一外(指向下一条指令),其它各控制线输出为零。

- 第4个时钟,若操作符为AND、ADD、XOR或LDA,读相应地址的数据;若为JMP,将目的地址送给程序计数器;若为STO,输出累加器数据。

- 第5个时钟,若操作符为ANDD、ADD或XORR,算术运算器就进行相应的运算;若为LDA,就把数据通过算术运算器送给累加器;若为SKZ,先判断累加器的值是否为0,如果为0,PC就增1,否则保持原值;若为JMP,锁存目的地址;若为STO,将数据写入地址处。

- 第6个时钟,空操作。

- 第7个时钟,若操作符为SKZ且累加器值为0,则PC值再增1,跳过一条指令,否则PC无变化。

状态机的VerilogHDL 程序见下面模块:

1 //------------------------------------------------------------------------------ 2 module machine( inc_pc, load_acc, load_pc, rd,wr, load_ir, 3 datactl_ena, halt, clk1, zero, ena, opcode ); 4 output inc_pc, load_acc, load_pc, rd, wr, load_ir; 5 output datactl_ena, halt; 6 input clk1, zero, ena; 7 input [2:0] opcode; 8 reg inc_pc, load_acc, load_pc, rd, wr, load_ir; 9 reg datactl_ena, halt; 10 reg [2:0] state; 11 12 parameter HLT = 3 'b000, 13 SKZ = 3 'b001, 14 ADD = 3 'b010, 15 ANDD = 3 'b011, 16 XORR = 3 'b100, 17 LDA = 3 'b101, 18 STO = 3 'b110, 19 JMP = 3 'b111; 20 21 always @( negedge clk1 ) 22 begin 23 if ( !ena ) //接收到复位信号RST,进行复位操作 24 begin 25 state<=3'b000; 26 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 27 {wr,load_ir,datactl_ena,halt}<=4'b0000; 28 end 29 else 30 ctl_cycle; 31 end 32 //-----------------begin of task ctl_cycle--------- 33 task ctl_cycle; 34 begin 35 casex(state) 36 3’b000: //load high 8bits in struction 37 begin 38 {inc_pc,load_acc,load_pc,rd}<=4'b0001; 39 {wr,load_ir,datactl_ena,halt}<=4'b0100; 40 state<=3’b001; 41 end 42 3’b001: //pc increased by one then load low 8bits instruction 43 begin 44 {inc_pc,load_acc,load_pc,rd}<=4'b1001; 45 {wr,load_ir,datactl_ena,halt}<=4'b0100; 46 state<=3’b010; 47 end 48 3’b010: //idle 49 begin 50 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 51 {wr,load_ir,datactl_ena,halt}<=4'b0000; 52 state<=3’b011; 53 end 54 3’b011: //next instruction address setup 分析指令从这里开始 55 begin 56 if(opcode==HLT) //指令为暂停HLT 57 begin 58 {inc_pc,load_acc,load_pc,rd}<=4'b1000; 59 {wr,load_ir,datactl_ena,halt}<=4'b0001; 60 end 61 else 62 begin 63 {inc_pc,load_acc,load_pc,rd}<=4'b1000; 64 {wr,load_ir,datactl_ena,halt}<=4'b0000; 65 end 66 state<=3’b100; 67 end 68 3’b100: //fetch oprand 69 begin 70 if(opcode==JMP) 71 begin 72 {inc_pc,load_acc,load_pc,rd}<=4'b0010; 73 {wr,load_ir,datactl_ena,halt}<=4'b0000; 74 end 75 else 76 if( opcode==ADD || opcode==ANDD || 77 opcode==XORR || opcode==LDA) 78 begin 79 {inc_pc,load_acc,load_pc,rd}<=4'b0001; 80 {wr,load_ir,datactl_ena,halt}<=4'b0000; 81 end 82 else 83 if(opcode==STO) 84 begin 85 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 86 {wr,load_ir,datactl_ena,halt}<=4'b0010; 87 end 88 else 89 begin 90 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 91 {wr,load_ir,datactl_ena,halt}<=4'b0000; 92 end 93 state<=3’b101; 94 end 95 3’b101: //operation 96 begin 97 if ( opcode==ADD||opcode==ANDD||opcode==XORR||opcode==LDA ) 98 begin //过一个时钟后与累加器的内容进行运算 99 {inc_pc,load_acc,load_pc,rd}<=4'b0101; 100 {wr,load_ir,datactl_ena,halt}<=4'b0000; 101 end 102 else 103 if( opcode==SKZ && zero==1) 104 begin 105 {inc_pc,load_acc,load_pc,rd}<=4'b1000; 106 {wr,load_ir,datactl_ena,halt}<=4'b0000; 107 end 108 else 109 if(opcode==JMP) 110 begin 111 {inc_pc,load_acc,load_pc,rd}<=4'b1010; 112 {wr,load_ir,datactl_ena,halt}<=4'b0000; 113 end 114 else 115 if(opcode==STO) 116 begin 117 //过一个时钟后把wr变1就可写到RAM中 118 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 119 {wr,load_ir,datactl_ena,halt}<=4'b1010; 120 end 121 else 122 begin 123 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 124 {wr,load_ir,datactl_ena,halt}<=4'b0000; 125 end 126 state<=3’b110; 127 end 128 3’b110: //idle 129 begin 130 if ( opcode==STO ) 131 begin 132 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 133 {wr,load_ir,datactl_ena,halt}<=4'b0010; 134 end 135 else 136 if ( opcode==ADD||opcode==ANDD||opcode==XORR||opcode==LDA) 137 begin 138 {inc_pc,load_acc,load_pc,rd}<=4'b0001; 139 {wr,load_ir,datactl_ena,halt}<=4'b0000; 140 end 141 else 142 begin 143 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 144 {wr,load_ir,datactl_ena,halt}<=4'b0000; 145 end 146 state<=3’b111; 147 end 148 3’b111: // 149 begin 150 if( opcode==SKZ && zero==1 ) 151 begin 152 {inc_pc,load_acc,load_pc,rd}<=4'b1000; 153 {wr,load_ir,datactl_ena,halt}<=4'b0000; 154 end 155 else 156 begin 157 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 158 {wr,load_ir,datactl_ena,halt}<=4'b0000; 159 end 160 state<=3’b000; 161 end 162 default: 163 begin 164 {inc_pc,load_acc,load_pc,rd}<=4'b0000; 165 {wr,load_ir,datactl_ena,halt}<=4'b0000; 166 state<=3’b000; 167 end 168 endcase 169 end 170 endtask 171 //-----------------end of task ctl_cycle--------- 172 endmodule 173 //------------------------------------------------------------------------------

9.外围模块

为了对RISC_CPU进行测试,需要有存储测试程序的ROM和装载数据的RAM、地址译码器。下面来简单介绍一下:

地址译码器

1 module addr_decode( addr, rom_sel, ram_sel); 2 output rom_sel, ram_sel; 3 input [12:0] addr; 4 reg rom_sel, ram_sel; 5 always @( addr ) 6 7 begin 8 casex(addr) 9 13'b1_1xxx_xxxx_xxxx:{rom_sel,ram_sel}<=2'b01; 10 13'b0_xxxx_xxxx_xxxx:{rom_sel,ram_sel}<=2'b10; 11 13'b1_0xxx_xxxx_xxxx:{rom_sel,ram_sel}<=2'b10; 12 default:{rom_sel,ram_sel}<=2'b00; 13 endcase 14 end 15 endmodule

地址译码器用于产生选通信号,选通ROM或RAM。

FFFFH---1800H RAM

1800H---0000H ROM

RAM

1 module ram( data, addr, ena, read, write ); 2 inout [7:0] data; 3 input [9:0] addr; 4 input ena; 5 input read, write; 6 reg [7:0] ram [10'h3ff:0]; 7 8 assign data = ( read && ena )? ram[addr] : 8'hzz; 9 10 always @(posedge write) 11 begin 12 ram[addr]<=data; 13 end 14 endmodule

ROM

1 module rom( data, addr, read, ena ); 2 output [7:0] data; 3 input [12:0] addr; 4 input read, ena; 5 reg [7:0] memory [13'h1fff:0]; 6 wire [7:0] data; 7 8 assign data= ( read && ena )? memory[addr] : 8'bzzzzzzzz; 9 10 endmodule

ROM用于装载测试程序,可读不可写。RAM用于存放数据,可读可写。

三、RISC CPU中各部件的相互连接关系

四、RISC CPU和它的外围电路

五、RISC CPU的寻址方式和指令系统

RISC_CPU的指令格式一律为:

指令系统仅由8条指令组成:

- 1) HLT 停机操作。该操作将空一个指令周期,即8个时钟周期。

- 2) SKZ 为零跳过下一条语句。该操作先判断当前alu中的结果是否为零,若是零就跳过下一条语句,否则继续执行。

- 3) ADD 相加。该操作将累加器中的值与地址所指的存储器或端口的数据相加,结果仍送回累加器中。

- 4) AND 相与。该操作将累加器的值与地址所指的存储器或端口的数据相与,结果仍送回累加器中。

- 5) XOR 异或。该操作将累加器的值与指令中给出地址的数据异或,结果仍送回累加器中。

- 6) LDA 读数据。该操作将指令中给出地址的数据放入累加器。

- 7) STO 写数据。该操作将累加器的数据放入指令中给出的地址。

- 8) JMP 无条件跳转语句。该操作将跳转至指令给出的目的地址,继续执行。

RISC_CPU是8位微处理器,一律采用直接寻址方式,即数据总是放在存储器中,寻址单元的地址由指令直接给出。这是最简单的寻址方式。

六、RISC CPU的操作和时序

一个微机系统为了完成自身的功能,需要CPU执行许多操作。以下是RISC_CPU的主要操作:

- 1.系统的复位和启动操作

- 2.总线读操作

- 3.总线写操作

1.系统的复位和启动操作

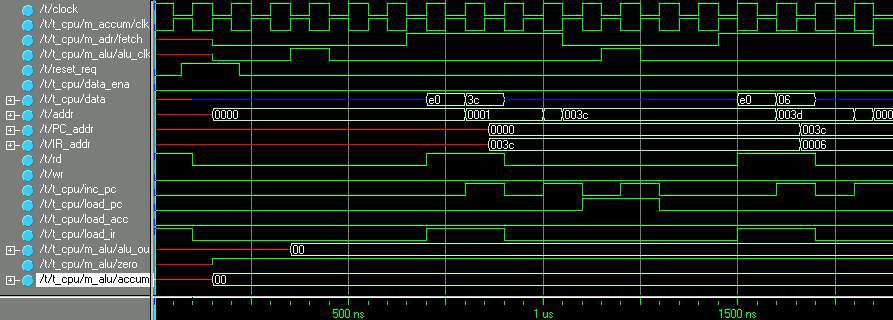

RISC_CPU的复位和启动操作是通过rst引脚的信号触发执行的。当rst信号一进入高电平,RISC_CPU就会结束现行操作,并且只要rst停留在高电平状态,CPU就维持在复位状态。在复位状态,CPU各内部寄存器都被设为初值,全部为零。数据总线为高阻态,地址总线为0000H,所有控制信号均为无效状态。rst回到低电平后,接着到来的第一个fetch上升沿将启动RISC_CPU开始工作,从ROM的000处开始读取指令并执行相应操作。波形图如下图所示。虚线标志处为RISC_CPU启动工作的时刻。RISC_CPU的复位和启动操作波形

2.总线读操作

每个指令周期的前0--3个时钟周期用于读指令,在状态控制器一节中已详细讲述,这里就不再重复。第3.5个周期处,存储器或端口地址就输出到地址总线上,第4--6个时钟周期,读信号rd有效,数据送到数据总线上,以备累加器锁存,或参与算术、逻辑运算。第7个时钟周期,读信号无效,第7.5个周期,地址总线输出PC地址,为下一个指令做好准备。CPU从存储器或端口读取数据的时序

浙公网安备 33010602011771号

浙公网安备 33010602011771号