第4章 处理器体系结构

第四章 处理器体系结构

4.1 Y86-64指令集体系结构

我们定义了一个与X86相对应的y86-64指令集结构

4.1.1程序员可见的状态

RF:15个程序寄存器,每个程序寄存机都存储一个64位的字。

CC:包括三个一位的条件码,保存着最近的算术或逻辑指令所造成影响的有关信息. 分为ZF(零标志) SF(符号标志) OF(溢出标志)

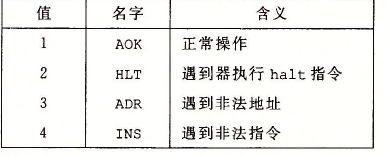

Stat:状态码,会指示现在程序是正常运行还是出现了异常

PC:Program counter 存储下一条指令的地址

DMEM:内存 内存从概念上来说就是一个很大的字节数组,保存着程序和数据,

4.1.2 Y86-64指令

Y86的ISA基本上是x86的一个子集,只包括对8字节整数的操作

·Y86 的movq指令分为4个不同的指令:irmovq , rrmovq , mrmovq,rmmovq

I: 立即数 , R : Register M:Memory

与x86一样,不支持把内存中一个数据移动到内存中另外一个地方

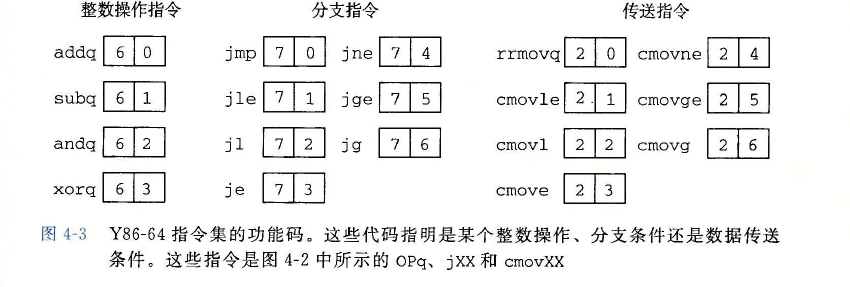

· 有四个整数操作指令Opq:addq subq andq 和xorq,他们只对寄存器数据进行操作,x86-64允许对内存数据进行操作,这些指令会设置三个条件码

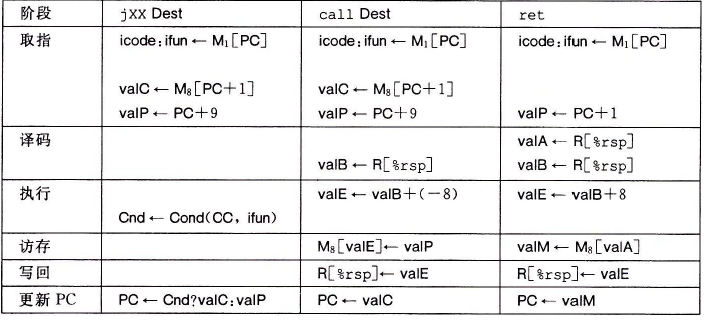

· 七个跳转指令:jmp jle jl je jne jge jg

· 有6个条件传送指令 :cmovle cmol cmoe cmovne cmovge cmovg 只有当条件码满足一定的约束时,才会更新目标寄存器的值

· call指令将返回地址入栈,然后跳转到目的地址。而ret指令则是把返回地址出栈。

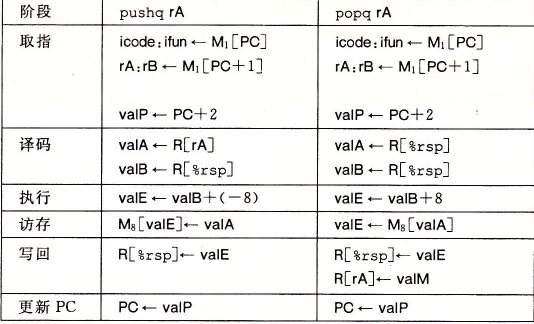

· pushq 和 popq实现了出栈和入栈

· halt指令停止指令的运行,会导致处理器停止

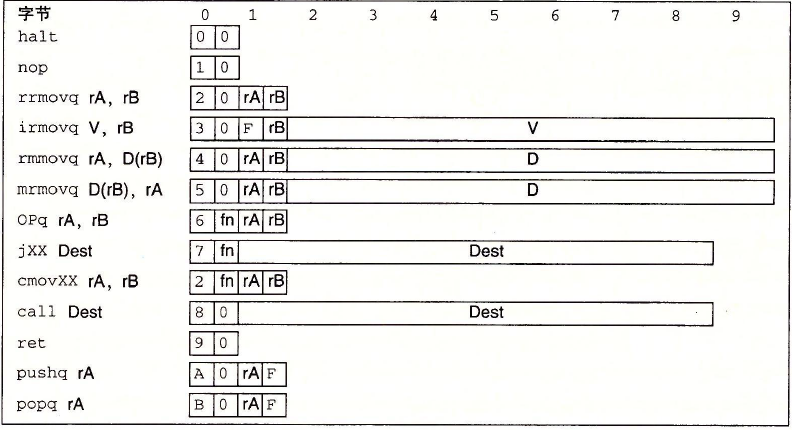

4.1.3指令编码

每条指令需要1~10个字节不等。指令的第一个字节表示它的类型,分为两个部分,高4位是code section 低4位是function section .

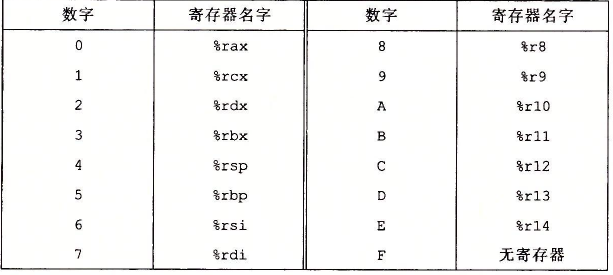

而对于这15个Register,每个都有一个对应的Register ID,范围 从0 ~0xE , 0xF代表不应访问任何寄存器

只需要一个寄存器操作数的指令,就可以把另一个寄存器指示符设为0xF.

而有些指令需要附加一个8字节长数字,可以作为irmovq的立即数数据,rmmovq和mrmovq的地址指示符的偏移量,以及分支指令和调用指令的目的地址。

同IA32一样,所有整数采用小端法编码。

例如,用十六进制来表示指令rmmovq %rsp , 0x123456789abcd(%rdx)

rmmovq第一个字节为40 %rsp为4 %rdx 为2 最后把0x123456789abcd填充为8字节数,最后按字节反序

全部连接起来就是4042cdab896745230100

4.1.4 Y86-64异常

在我们的设计中,除了AOK以外的所有代码都会使处理器停止。

4.2 逻辑设计和硬件控制语言HCL

在硬件设计中,逻辑1用1.0V左右的高电压表示,逻辑0用0.0伏特左右的低电压表示.要实现一个数字系统需要三个主要的组成部分:计算对位进行操作的函数的组合逻辑,存储位的存储器单元和控制存储器单元更新的时钟信号。

4.2.1 逻辑门

AND、OR、NOT(&& || !)

门可以进行n路操作

4.2.2 组合电路和HCL布尔表达式

将很多的逻辑门组合成一个网,就能构建一个计算块(computational block)称为组合电路

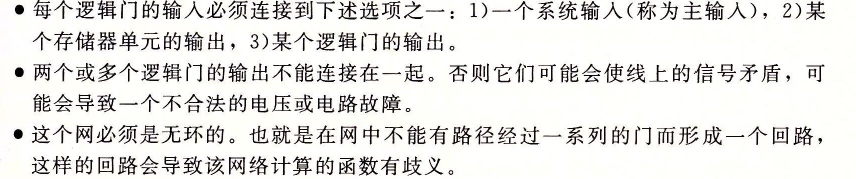

bool eq = (a && b ) || (!a && !b); ab相等的时候会输出1

bool eq = (a && b ) || (!a && !b); ab相等的时候会输出1

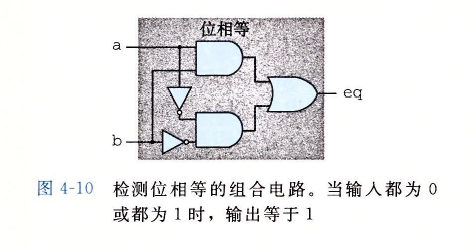

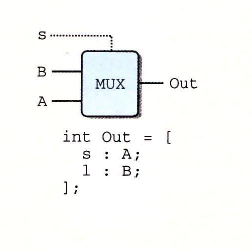

bool out = (s&& a ) || ( !s && b);

bool out = (s&& a ) || ( !s && b);

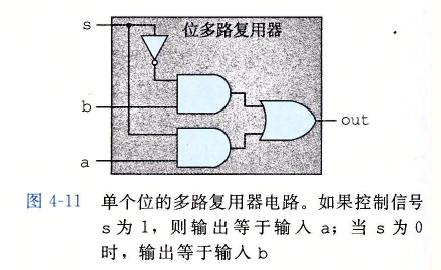

4.2.3 字级的组合电路和HCL整数表达式

利用上面单个的位测试电路,搭建组合电路,对字进行相等检测

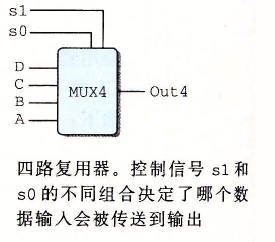

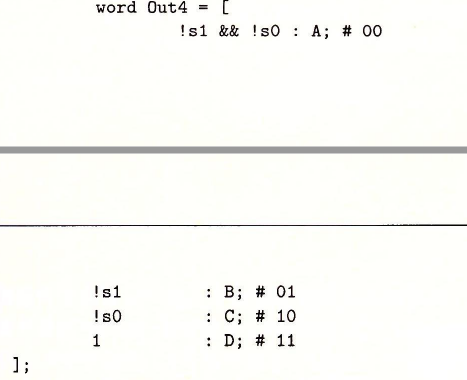

在HCL中,多路复用函数使用情况表达式来描述的

[

select1 : expr1;

select2 :expr2;

……

];

第一个求值为 1 的情况会被选中,1: 为默认情况,也是最后判断的情况

选择表达式可以使任意的布尔表达式,例如下面的四路复用器

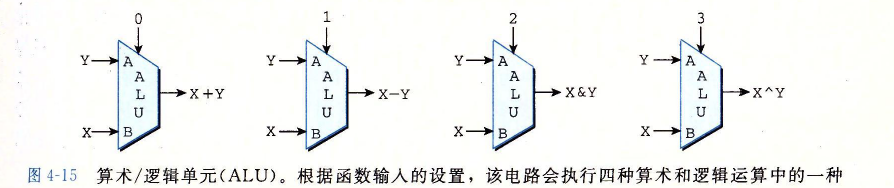

算术/逻辑单元(ALU)有三个输入,对数据进行不同的算术或逻辑运算

4.2.4集合关系

在处理器设计中,有时候可能会把输入信号和许多相匹配的情况进行比较,这时候使用集合更加方便

通用格式 iexpr in { };

4.2.5存储器和时钟

组合电路只是对信息进行一定处理,并不存储信息。为了产生时序电路,我们必须引入存储设备。而存储设备都是由一个时钟控制的,时钟是一个周期性信号,决定什么时候把新值加载到设备中。

我们可以把寄存器想象成一个仓库,时钟则是一个打开仓库大门的电机。

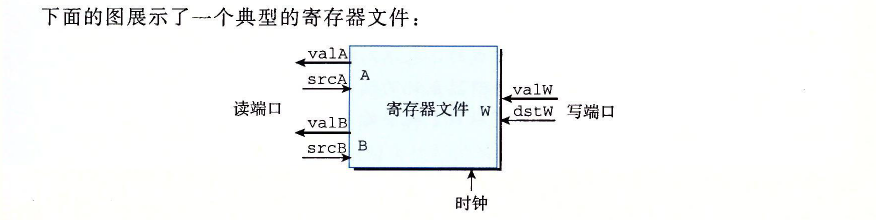

下面的图展示了一个典型的寄存器文件

虽然寄存器文件不是组合电路,但是从寄存器读取文件好像它是一个以地址为输入、数据为输出的组合逻辑块。

在srcA被设置为某个RigisterID时,存储在该Rist中的数据就会出现在valA上。

向寄存器文件写入字是由时钟信号控制的

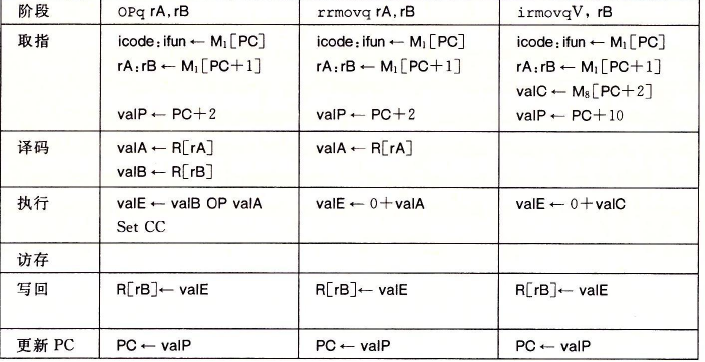

4.3 Y86-64的顺序实现

描述一个SEQ(sequential顺序的)处理器

4.3.1将处理组织成阶段

取指(fetch):从内存读取指令字节

译码(decode):从寄存器文件读入最多两个操作数,得到valA和 valB

一般是读入ra rb 指明的寄存器

执行(execute): 在exec阶段,ALU要么执行指令指明的操作,要么增加或减少栈指针,得到的值我们成为valE.这个阶段会设置CC

访存(memory): 可以写数据到内存中,或者把内存的数据读出。读出的数据称为valM

写回(write back): 最多可以写两个结果到寄存器文件

更新PC(PC update):

从popq过程这边可以看到把栈倒过来的好处

Cnd是一个一位信号

浙公网安备 33010602011771号

浙公网安备 33010602011771号