计算机组成原理基础第5讲 CPU系统

计算机组成原理基础第5讲 CPU系统

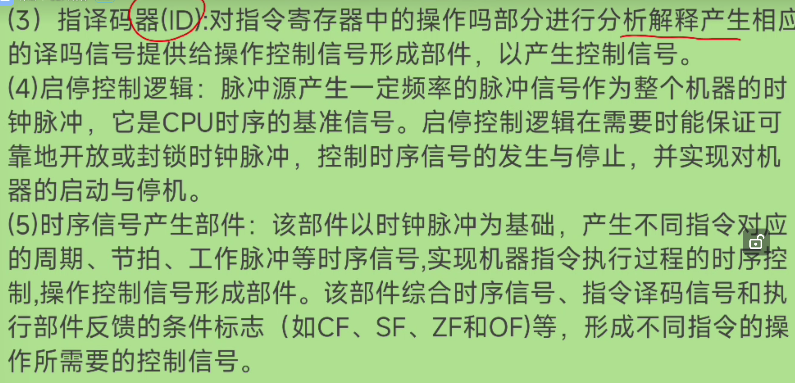

考点一:CPU的功能和组成

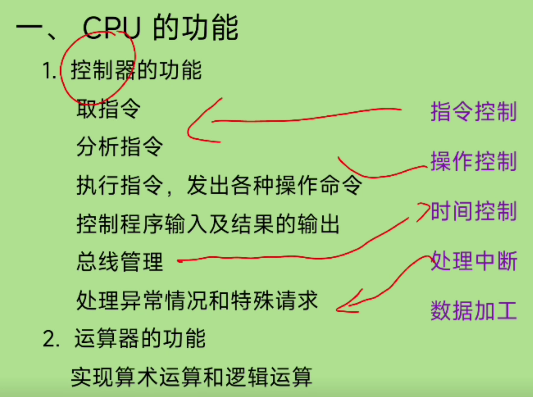

1. CPU的功能

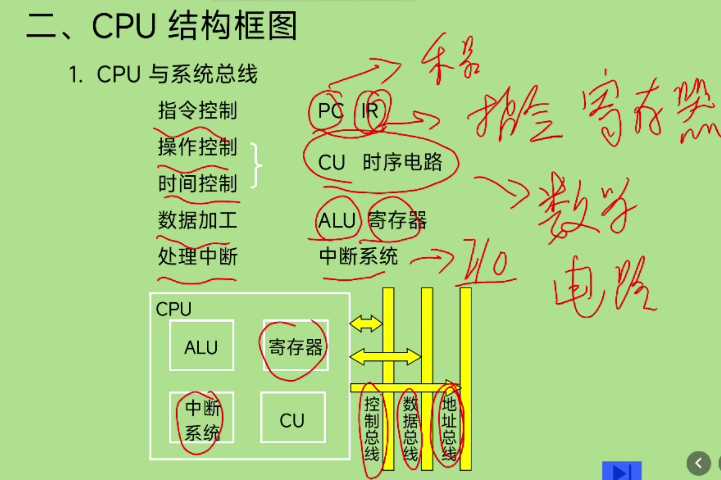

2. CPU的组成与结构

-

系统总线

-

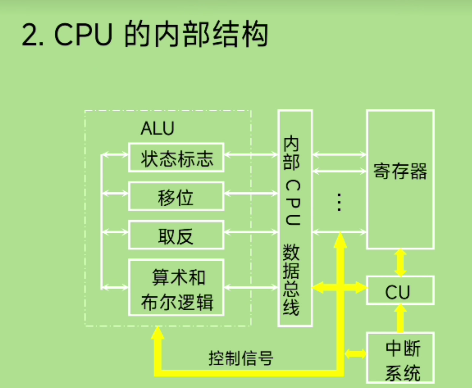

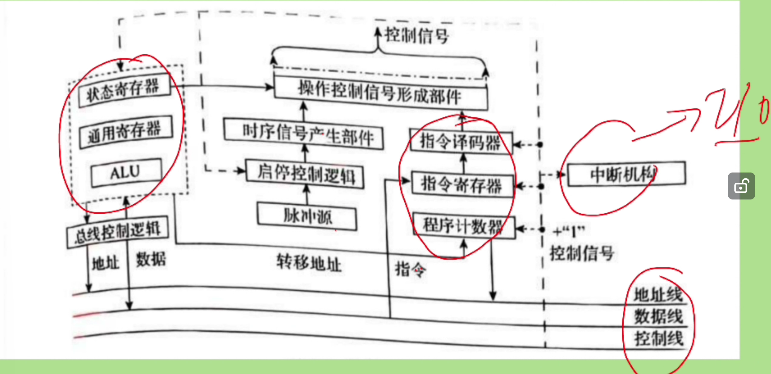

CPU的内部结构

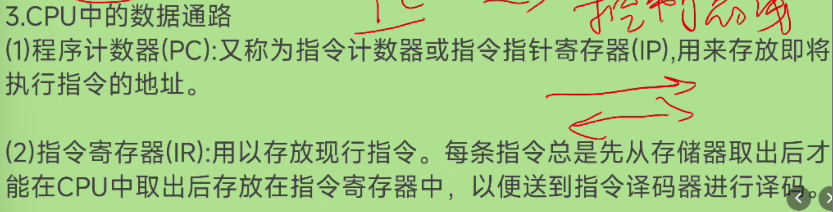

3. CPU中的数据通路

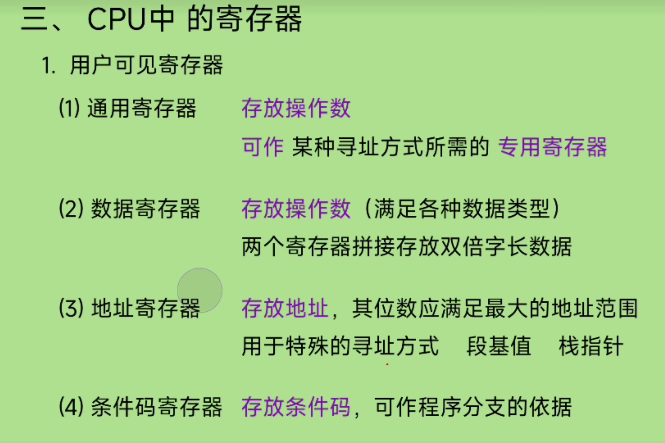

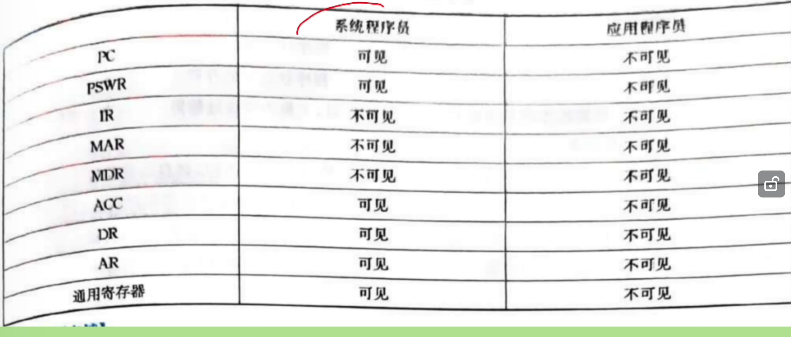

4. CPU中的寄存器

-

用户可见

-

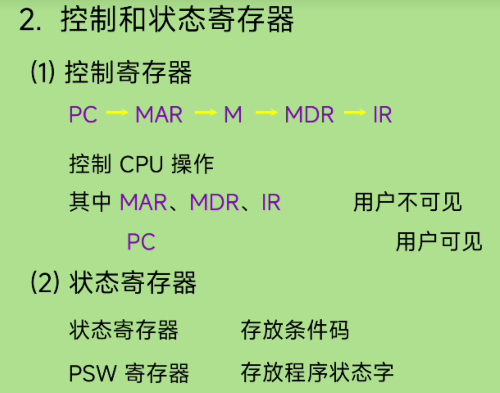

控制和状态寄存器

-

PC 程序计数器

用于存放下一条执行指令的地址

-

IR 指令寄存器

用于保存当前正在执行的指令

-

MDR 存储器,数据寄存器

暂时存放由主存储器读出的一条指令或一个数据字;

当向主存写入时也用于暂存

-

MAR 存储器 地址寄存器

用于保存当前CPU所访问的主存单元

-

程序状态字寄存器

用于存放程序状态字,表征程序和计算机运行的状态

-

ACC 累加寄存器

为ALU暂时保存一个操作数或运算结果

-

DR 数据缓冲寄存器

保存从内存读取的数据或将要写道内存的数据

-

地址缓冲寄存器

保存当前CPU所访问的内存单元的地址

考点二:CPU数据通路

1. 时序系统

-

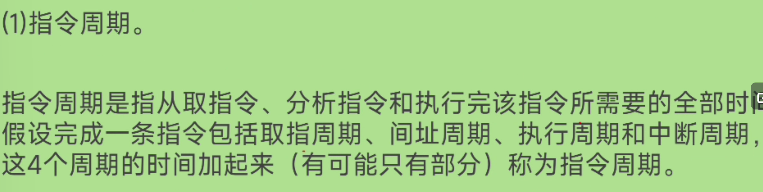

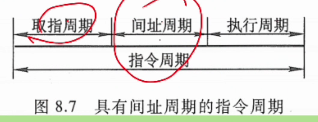

指令周期

-

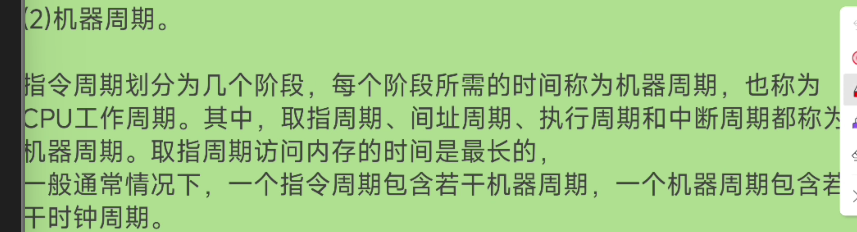

机器周期

-

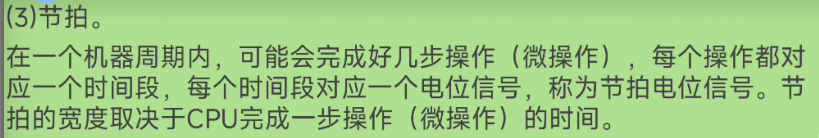

节拍

2. CPU的控制方式

-

同步控制方式

-

异步控制方式

-

联合控制方式

3. CPU内部的数据通路

-

取指周期

-

间址周期

-

加法周期ADD X

-

存取周期STA X

-

取数周期 LDA X

-

转移周期

-

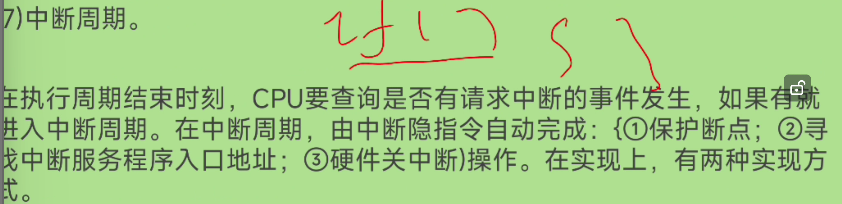

中断周期

考点三:CPU设计原理

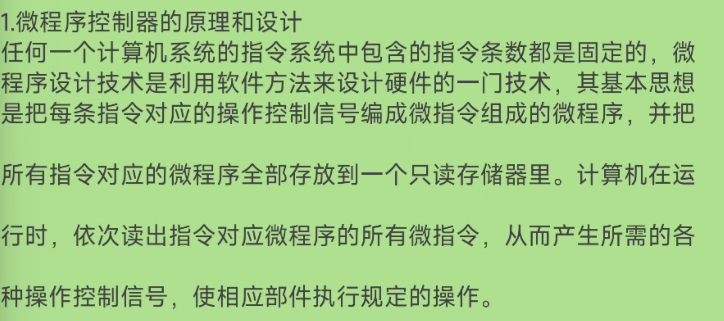

1. 微程序控制器的原理和设计

-

微程序控制器的设计思想

-

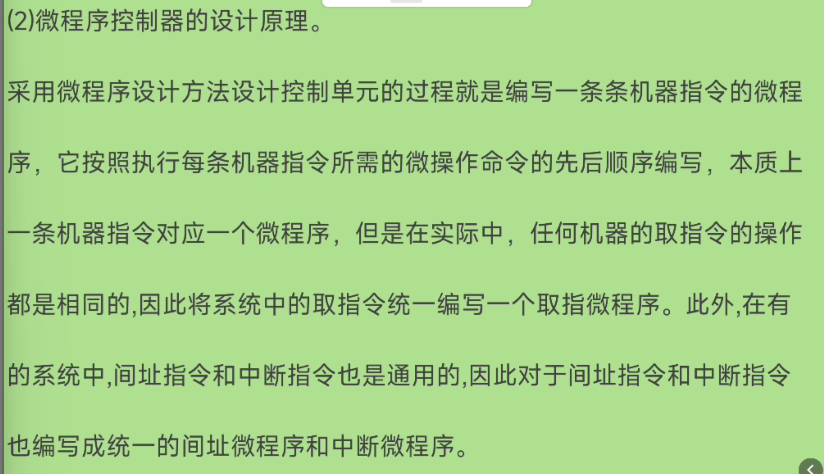

微程序控制器的设计原理

-

微程序控制器的基本结构

-

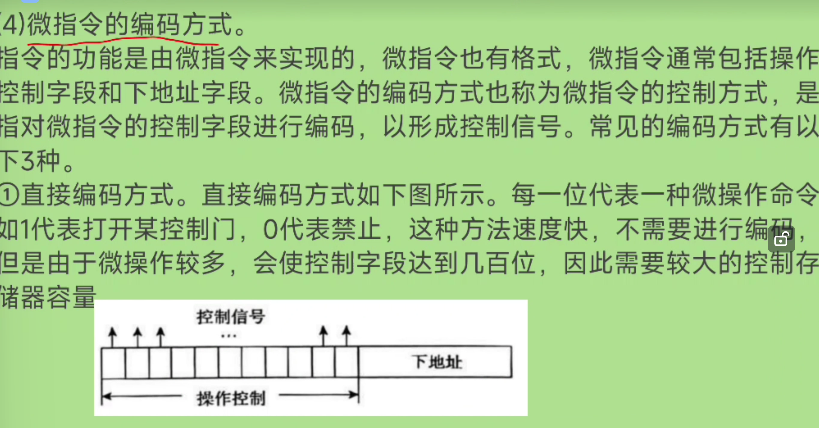

微指令的编码方式

-

直接编码

-

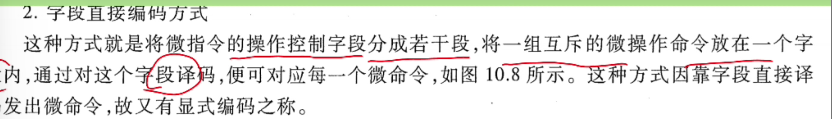

字段直接编码

-

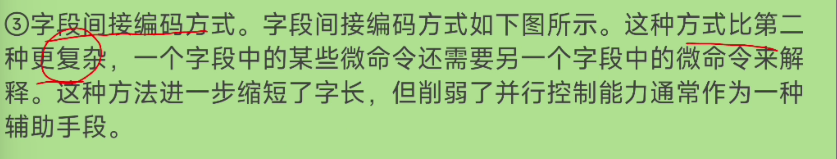

字段间接编码

-

-

微指令序列地址的形成方式

-

微程序控制器的工作过程

-

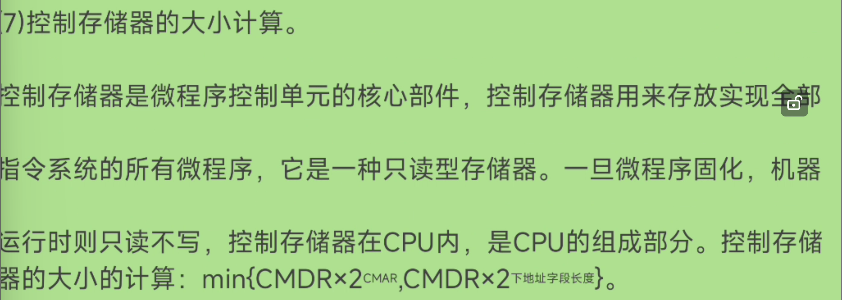

控制存储器的大小计算

-

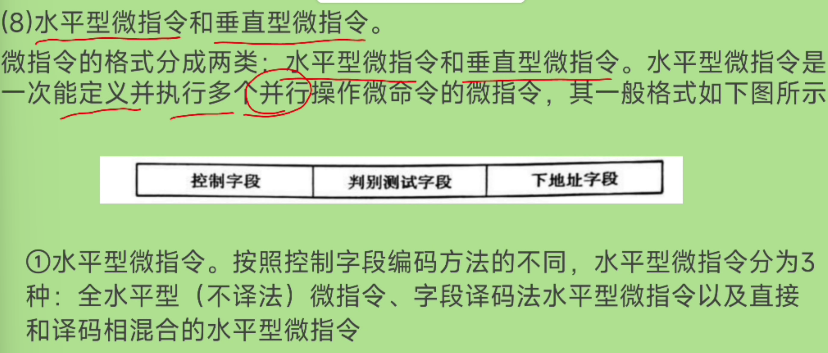

水平型微指令和垂直型微指令

2. 组合逻辑控制器的原理和设计

考点四:指令流水线

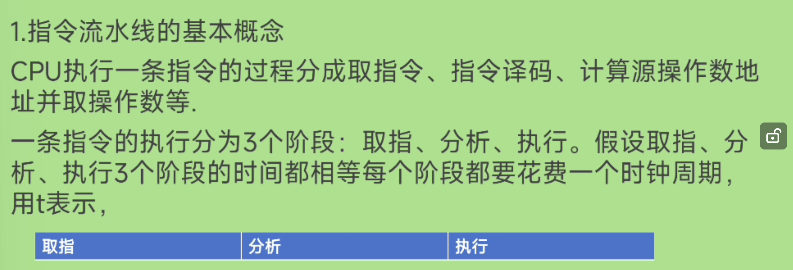

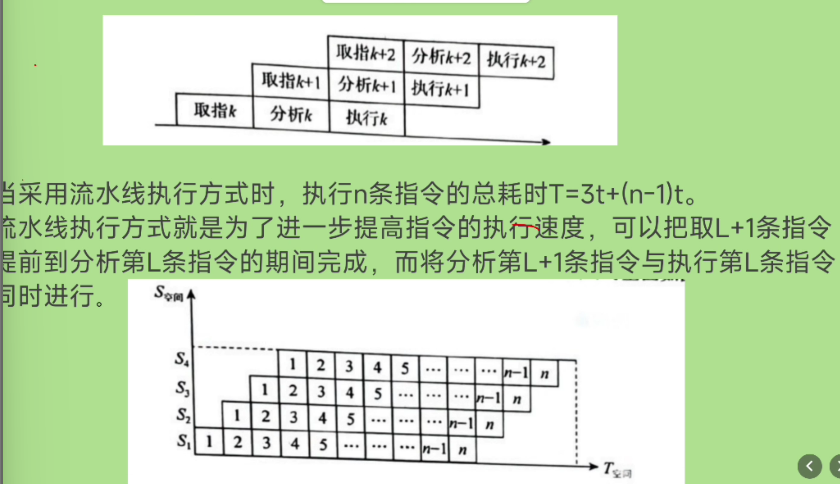

1. 指令流水线的基本概念

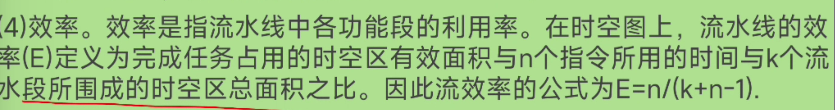

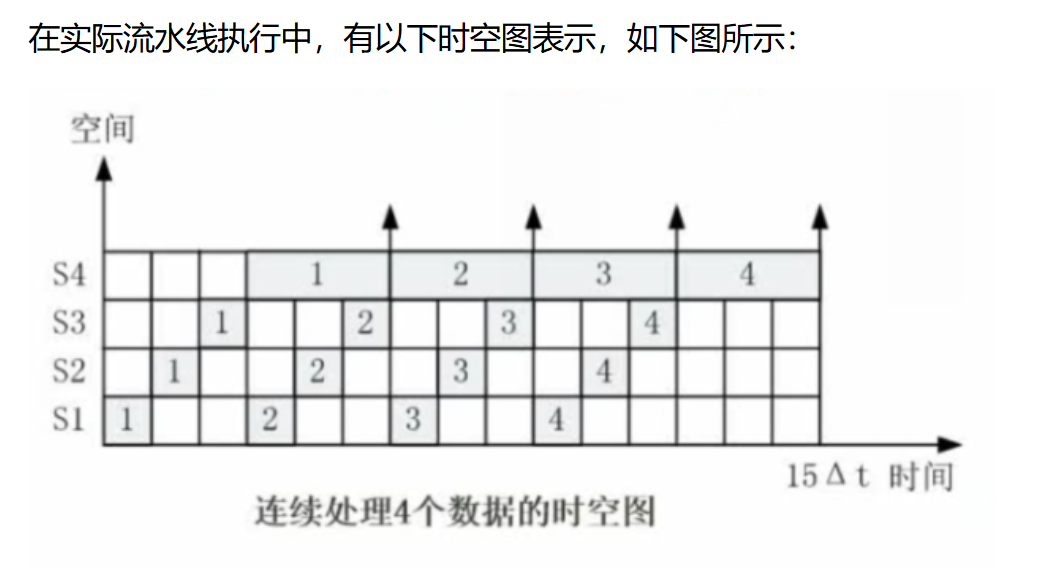

2. 指令流水线的性能指标

-

执行时间

执行n条指令

每条分为k段

每段完成时间为t

用时:\(T_n=kt + (n - 1)t\)

-

吞吐率

-

加速比

-

效率

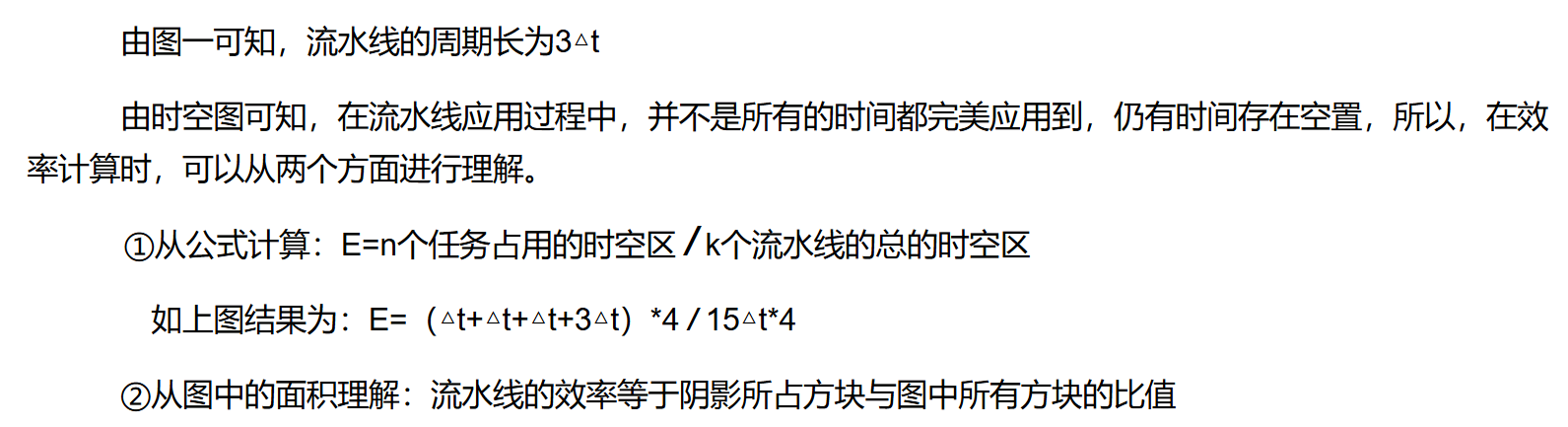

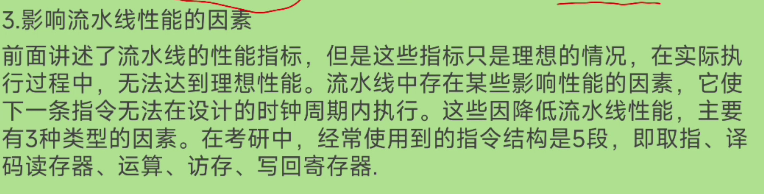

3. 影响流水线性能的因素

-

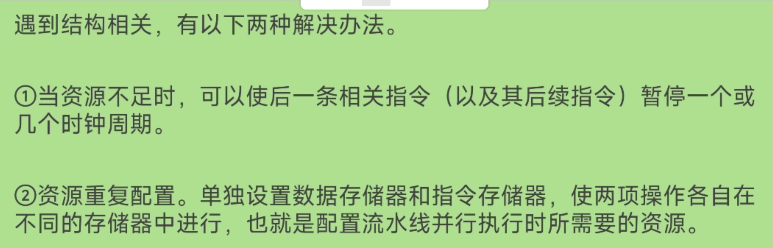

结构相关

-

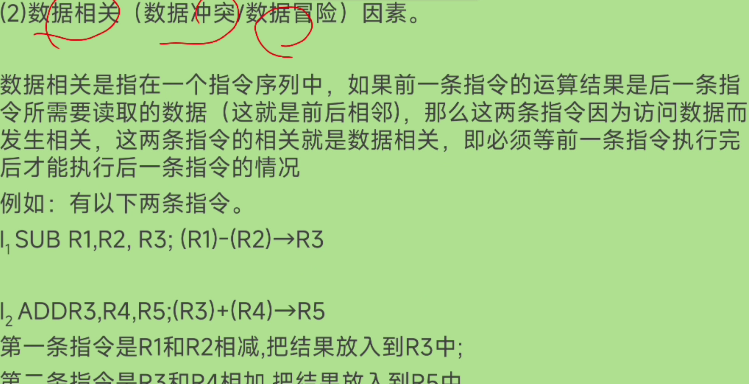

数据相关

-

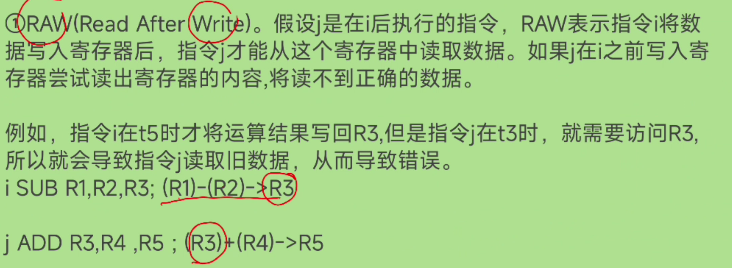

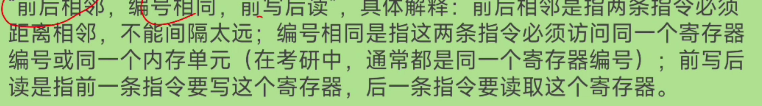

读在写之后RAW

-

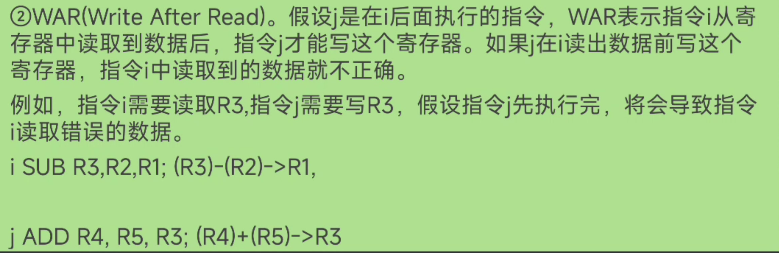

写在读之后WAR

-

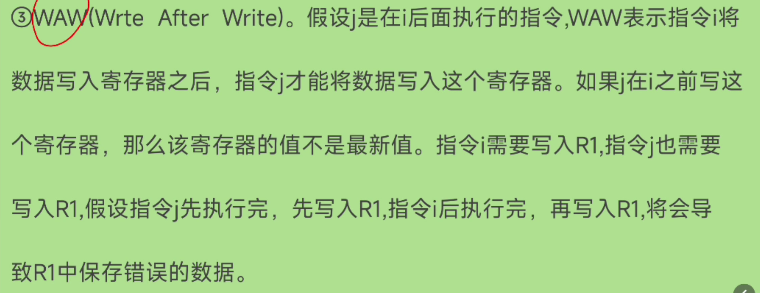

写在写之后,按严格顺序写入WAW

-

-

控制相关

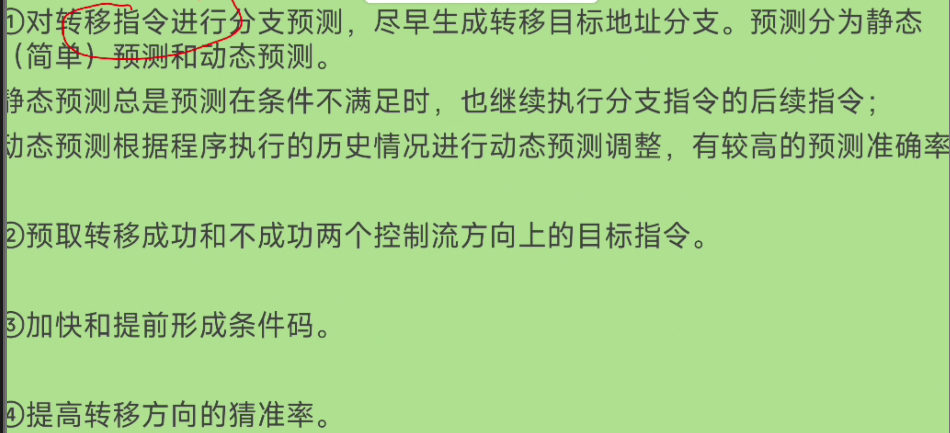

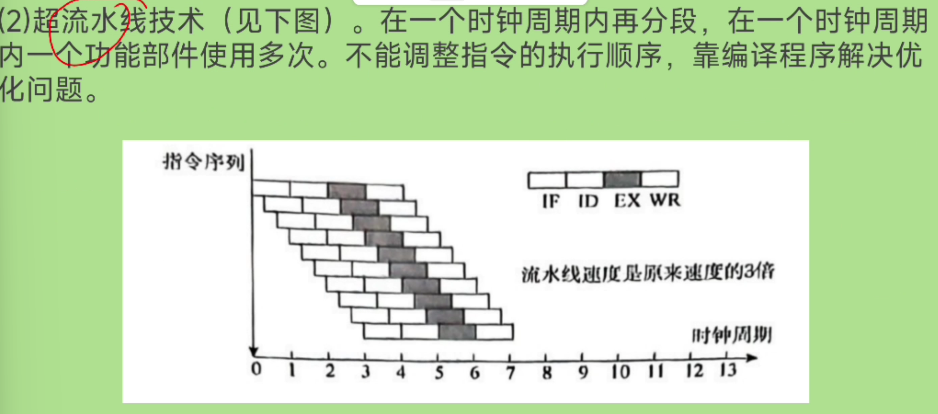

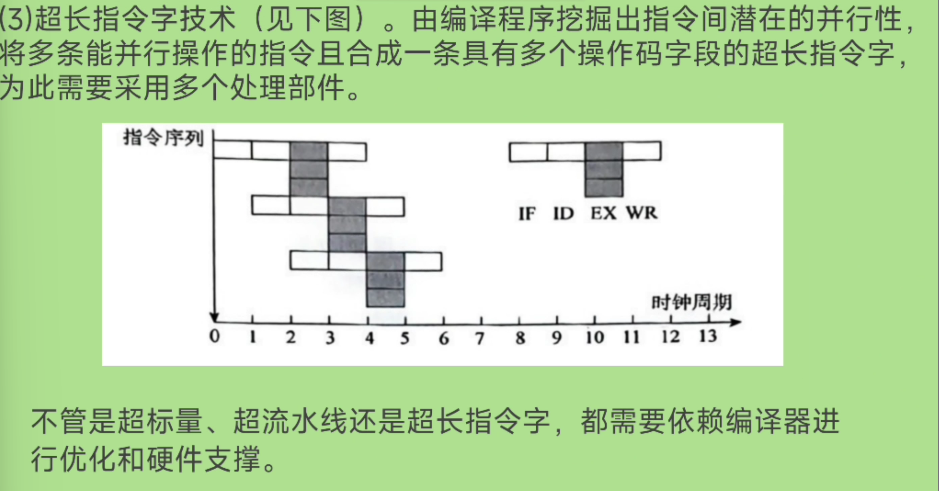

4. 超流水线技术

浙公网安备 33010602011771号

浙公网安备 33010602011771号