计算机组成原理基础第3讲

计算机组成原理基础第3讲 主存储器

考纲

考点一:存储器的概念

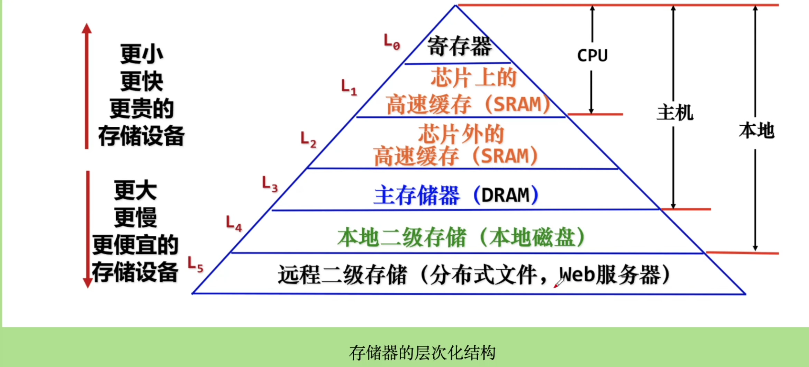

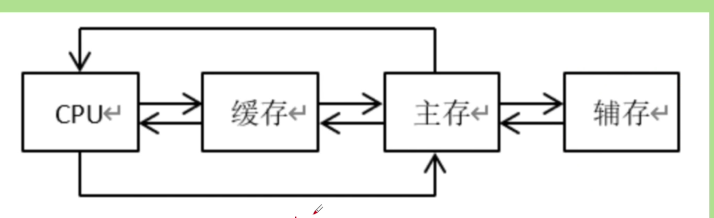

1.存储器的系统结构

-

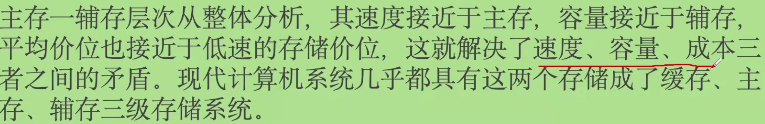

两级存储结构

缓存——主存层次和主存——辅存层次

2.存储器的分类

-

按计算机系统中的作用分类

-

按信息的存取方式分类,存储器课分为RAM,ROM,SAM和DAM

-

按存储介质分类

-

按信息的可用保存性分类

-

按用途分类

考点二:半导体随机存储器和只读存储器

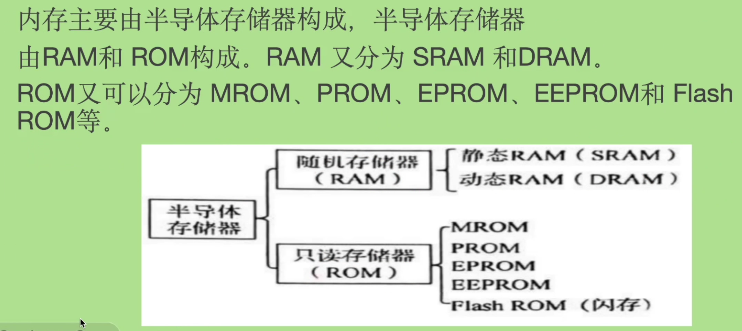

1.半导体存储器的分类

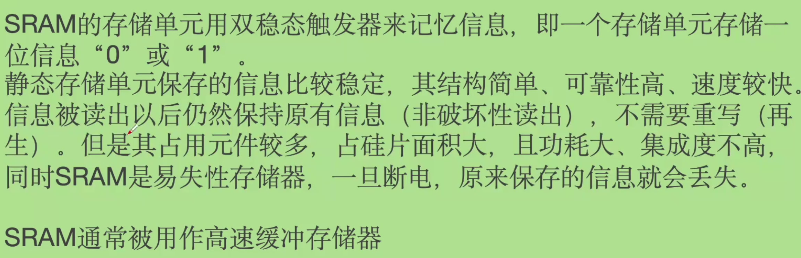

2,SRAM的工作原理

非破坏性读出

易失性存储器,一旦断电内容丢失

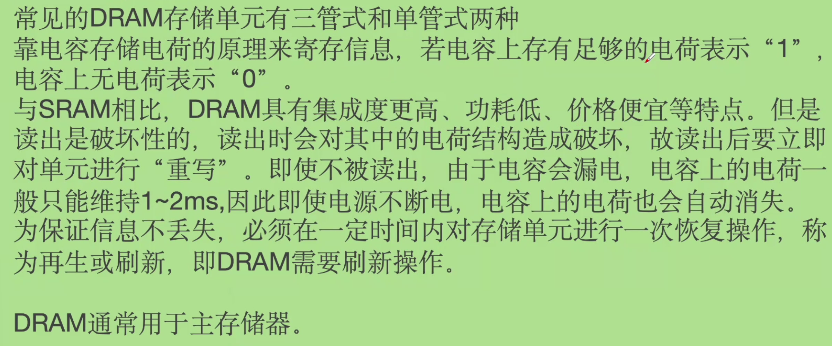

3.DRAM的工作原理

破坏性读出

需要刷新

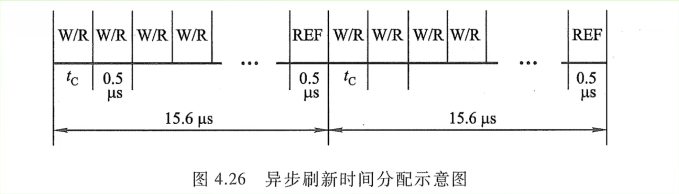

4.DRAM刷新

-

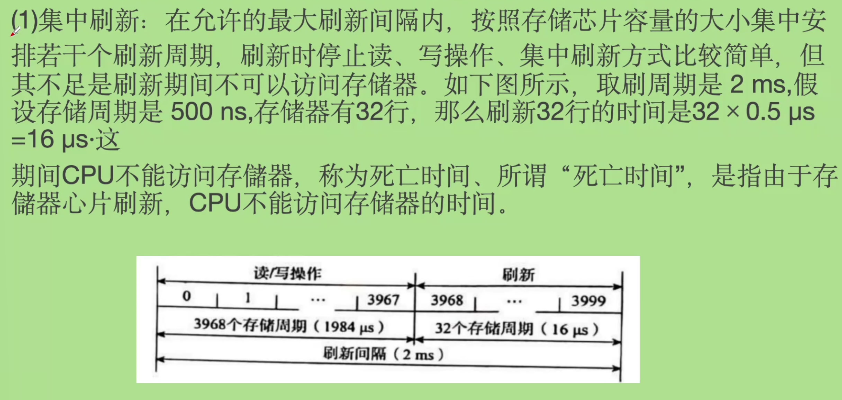

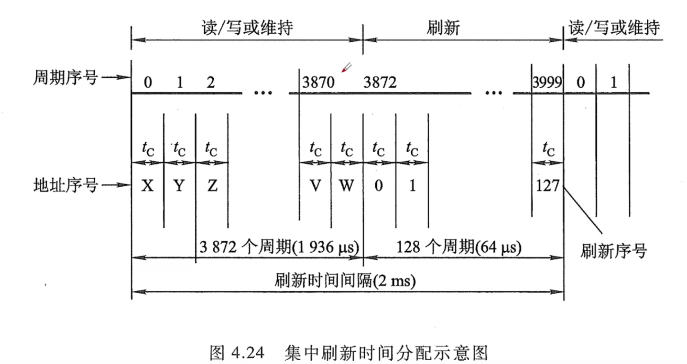

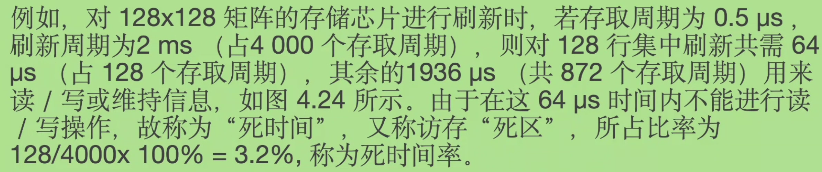

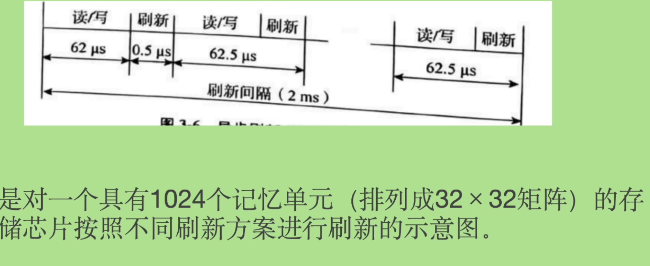

集中刷新

例子

-

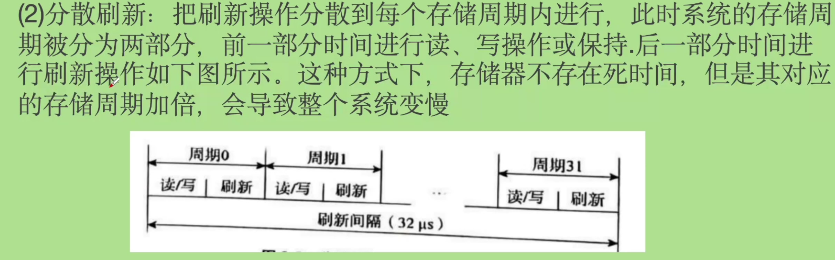

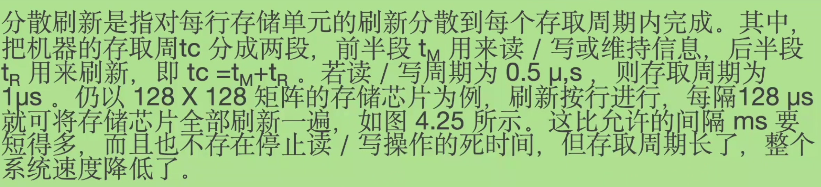

分散刷新

-

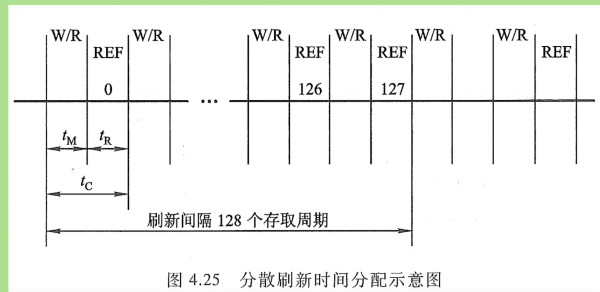

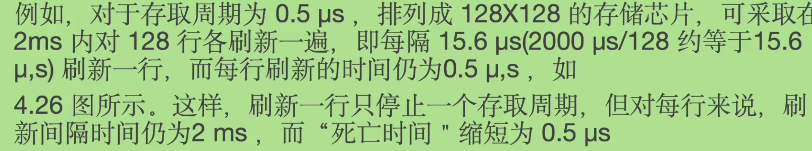

异步刷新

例子

5.只读存储器

-

掩模型只读存储器(MROM)

只读不写

-

可编程只读存储器(PROM)

熔丝式,只能写一次

-

可擦除可编程只读寄存器(EPROM)

紫外线可擦除

-

电可擦除可编程只读存储器(EEPROM)

电可擦除

-

快速读写存储器(Flash Memory)

还是属于ROM范畴

-

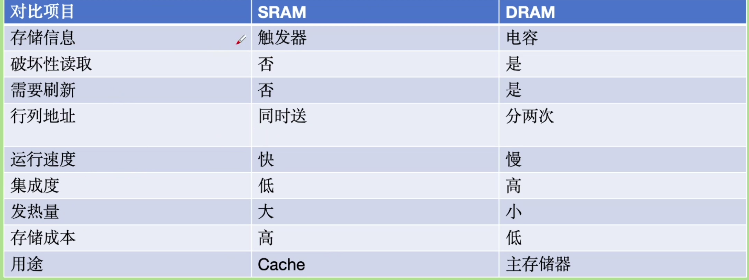

SRAM与DRAM对比

-

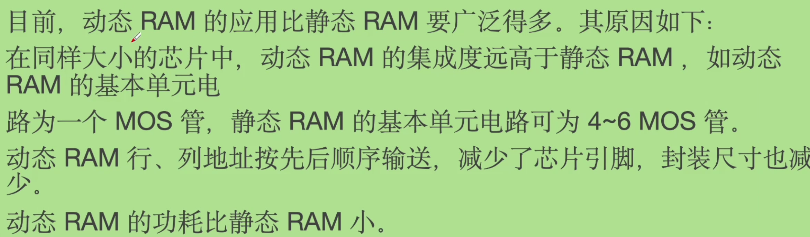

动态RAM与静态RAM的比较

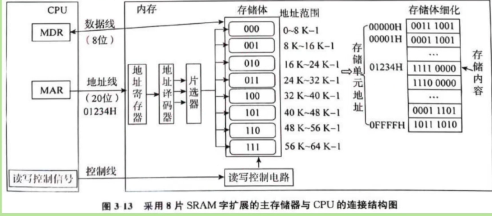

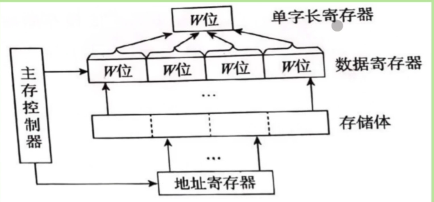

考点三:主存储器与CPU的连接与控制

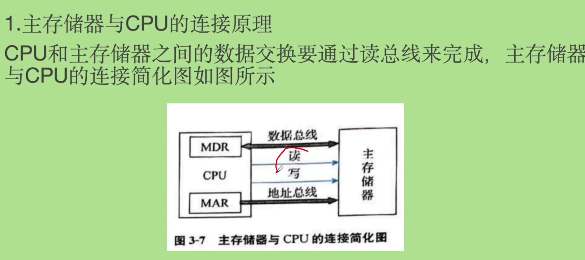

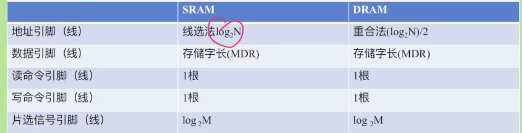

1.主存储器与CPU的连接原理

-

MAR

-

MDR

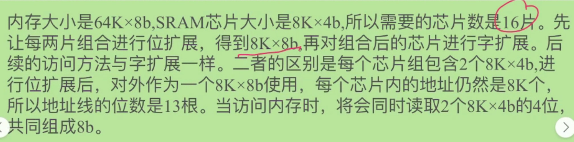

2.主存储器容量的扩展

-

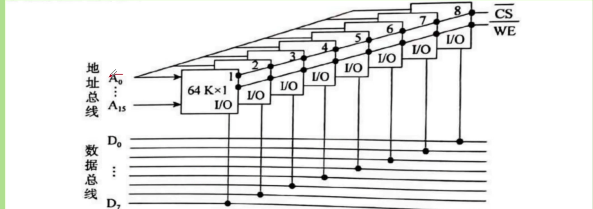

位扩展

-

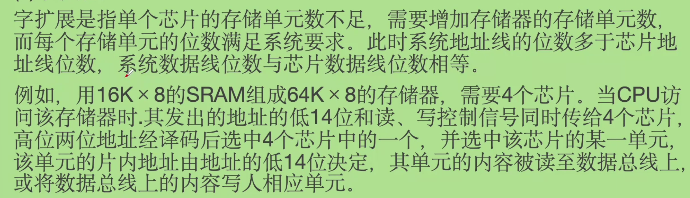

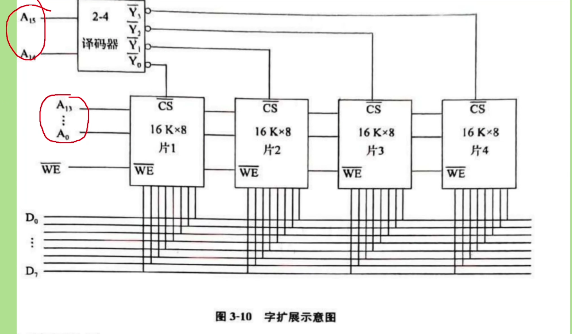

字扩展

-

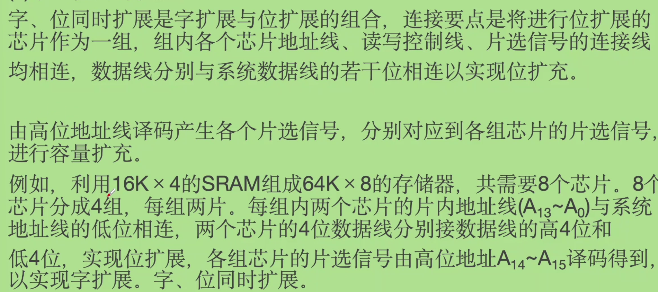

字位同时拓展

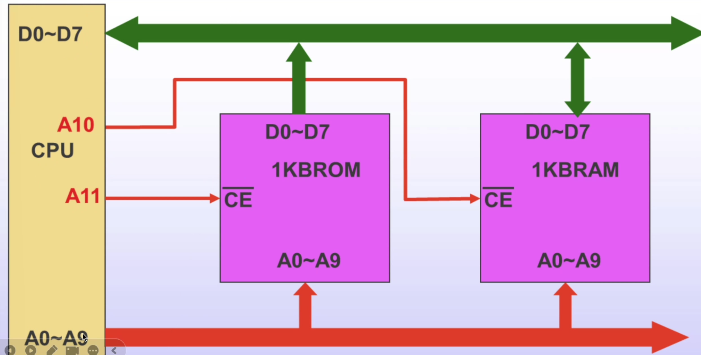

3.芯片组的地址译码法

-

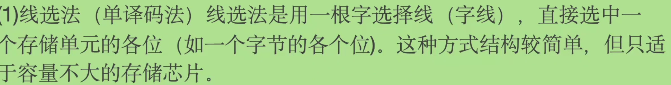

线选法

-

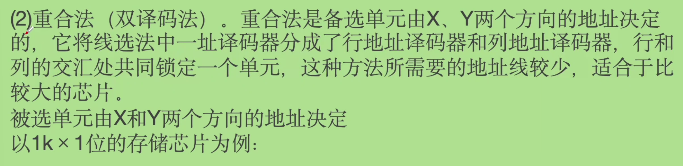

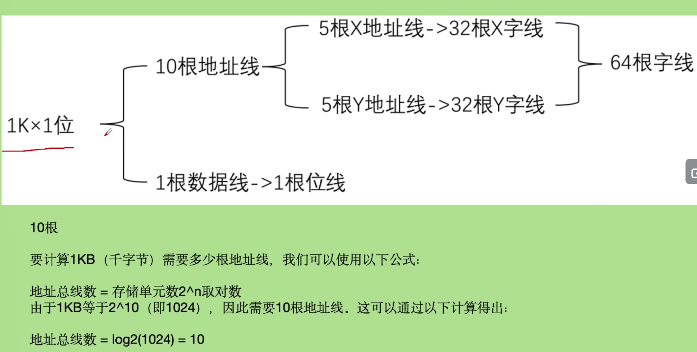

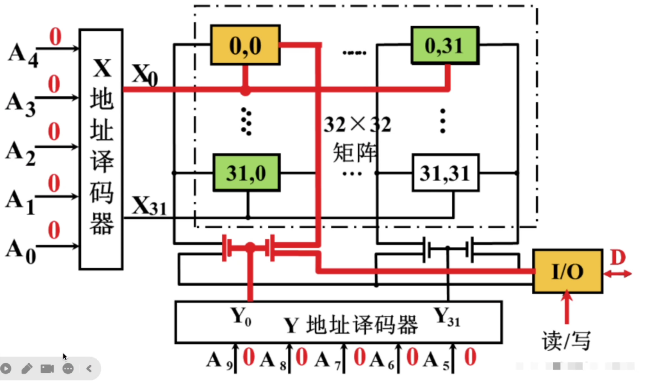

重合法

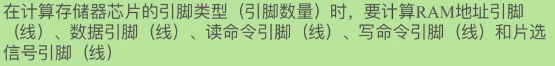

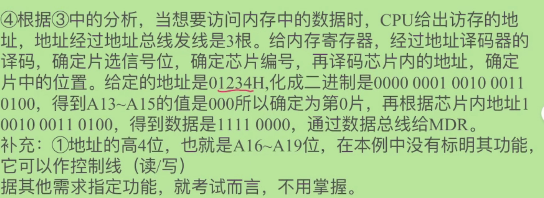

4.CPU与主存储器连接的引脚计算

-

计算芯片类型和数量

-

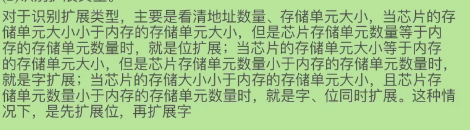

识别扩展类型

-

不同的存储器芯片引脚数量

-

芯片的地址空间的计算

按位运算(bit)= 存储单元个数 * 存储的字长

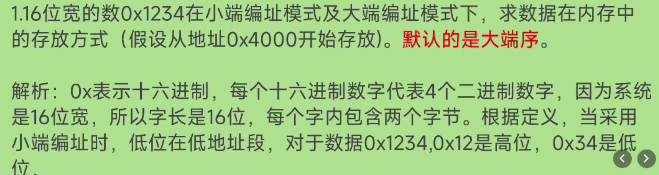

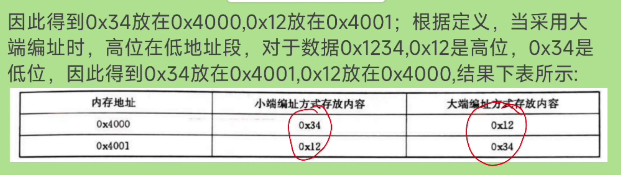

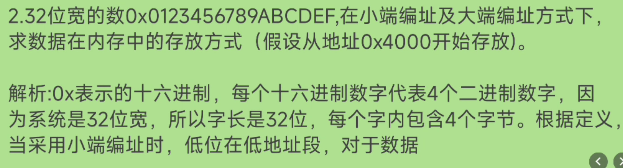

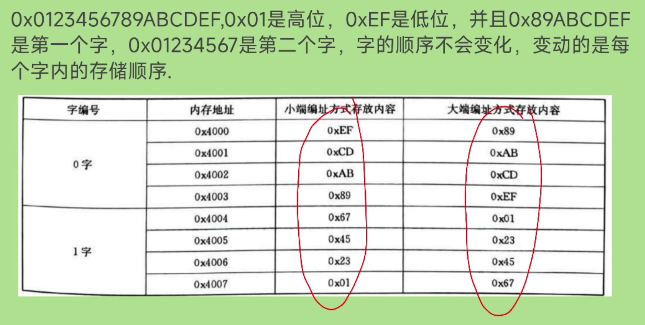

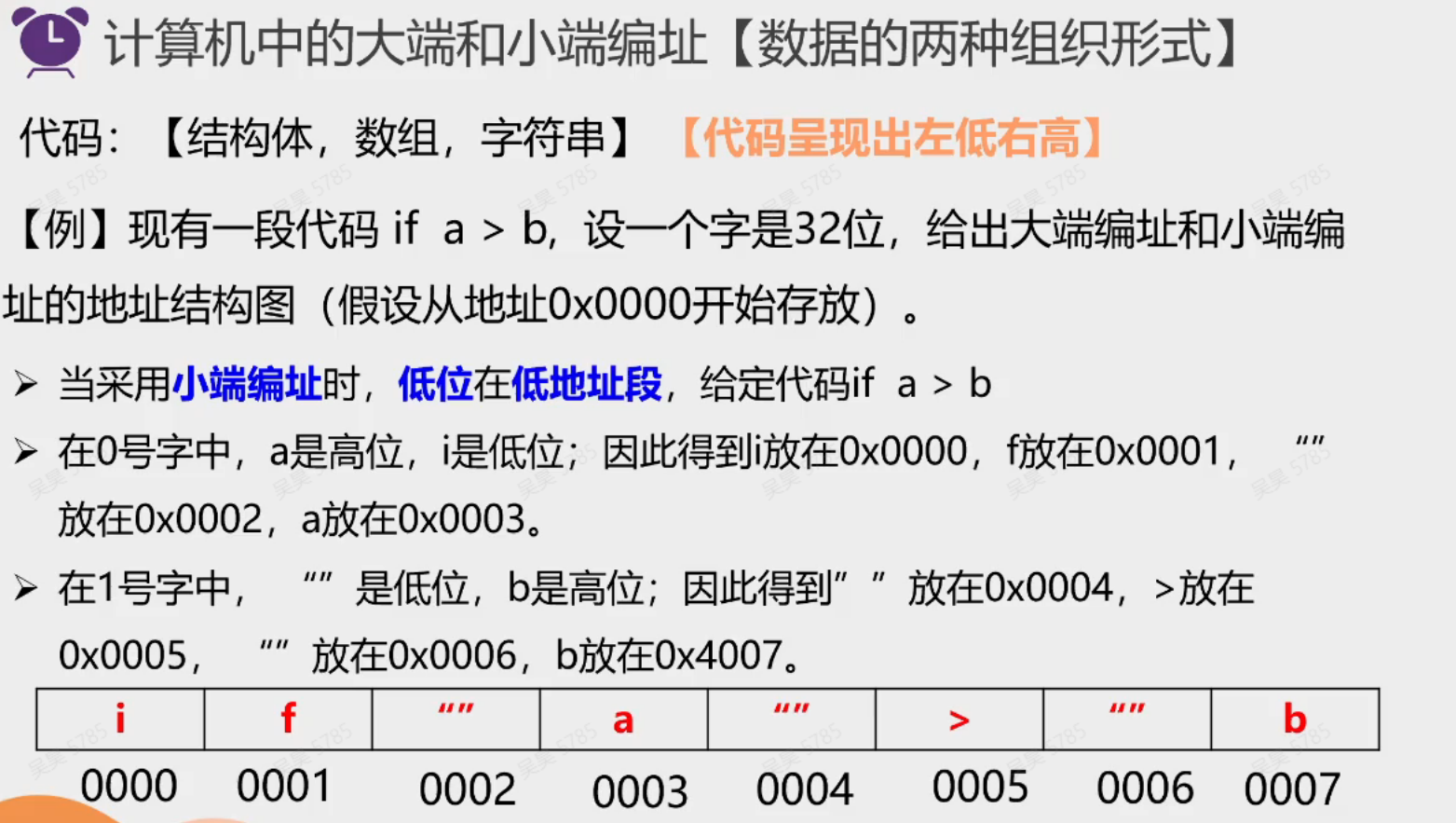

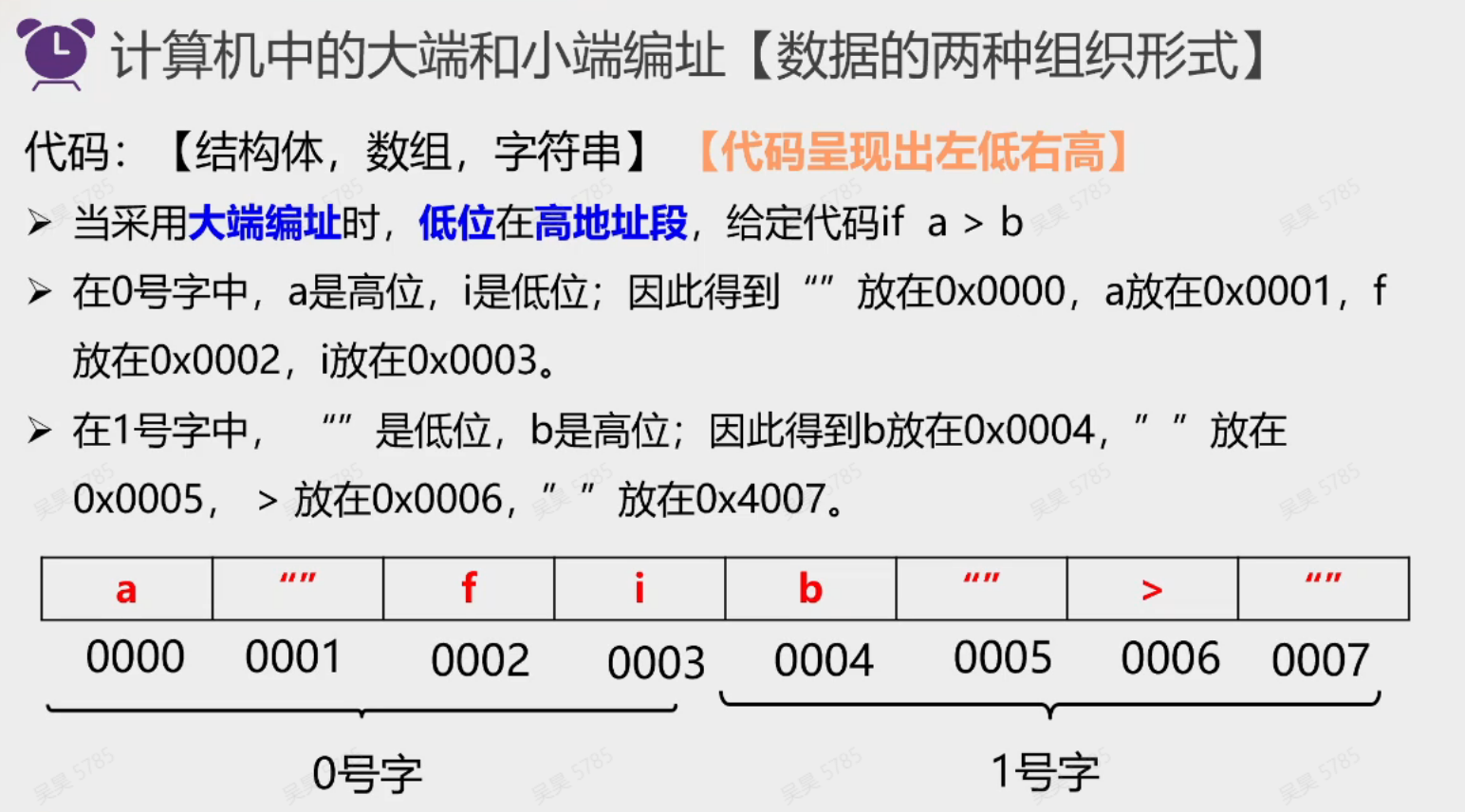

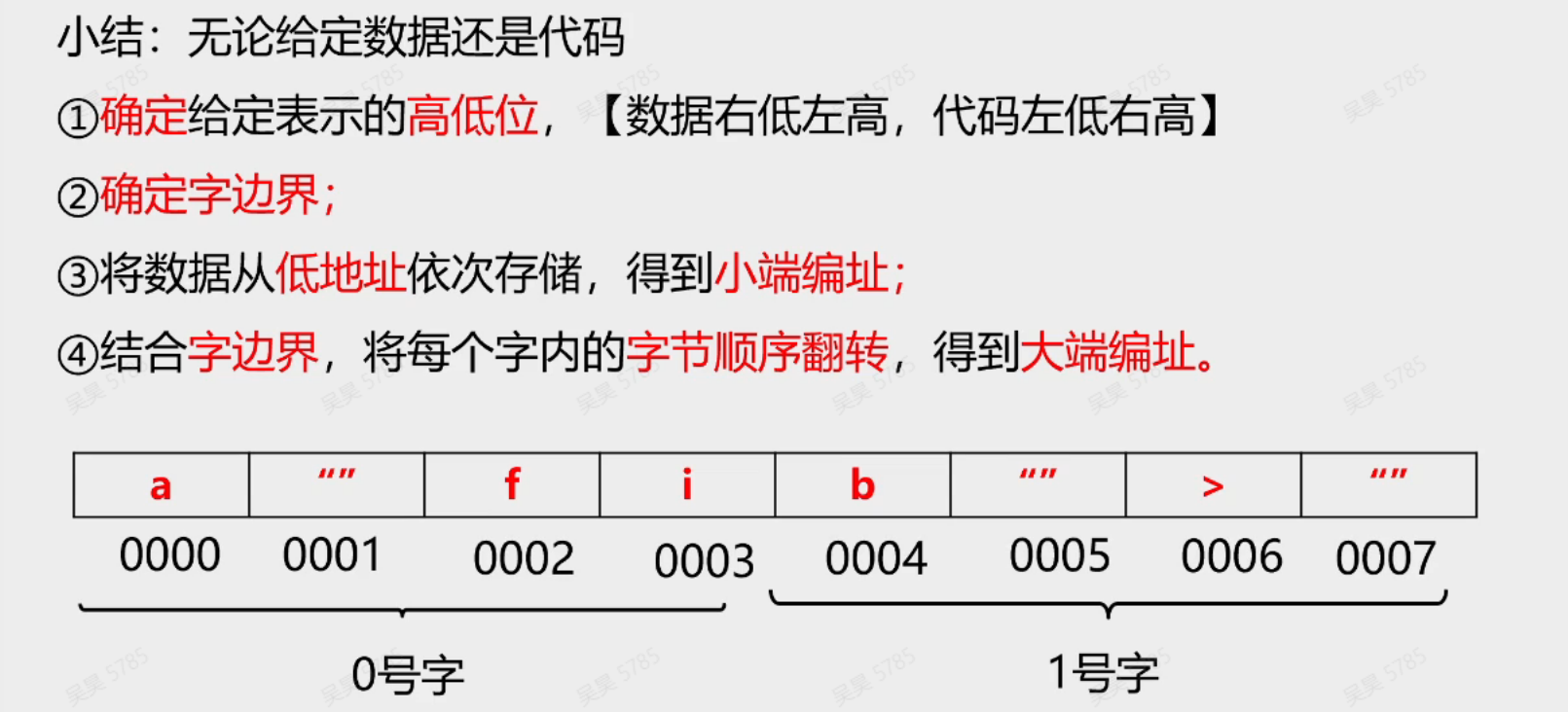

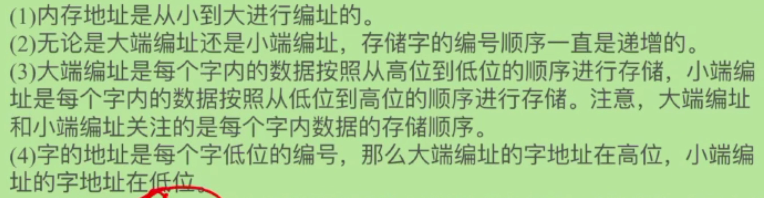

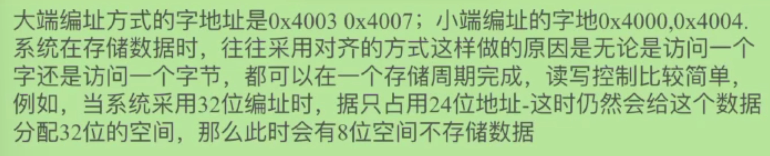

5.操作数在存储器中的存放方式

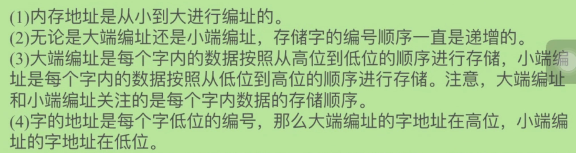

决定什么位在低地址端存放,大端就是高位放在低地址,小段就是低位放在低地址端

小端编址:

大端编址:

一个内存地址对应计算机的一个存储单元,默认按字节为单位1B=8b因此一个单元内存放两位16进制数,按大端即将数据按从左往右顺序两位两位存放,小端反过来。

0号字一定在1号字之前

数字呈现左高右低:ox1234,12高位,34低位

代码[结构体,数组,字符串]呈现左低右高:if a>b,i低位,b高位

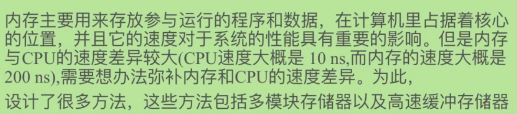

考点四:多模块存储器

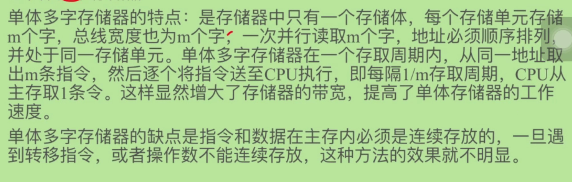

1.单体字存储器

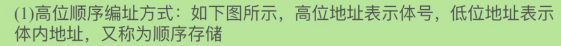

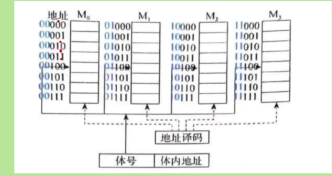

2.多体并行存储器

-

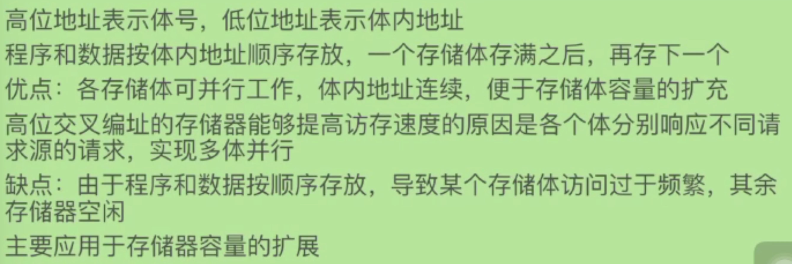

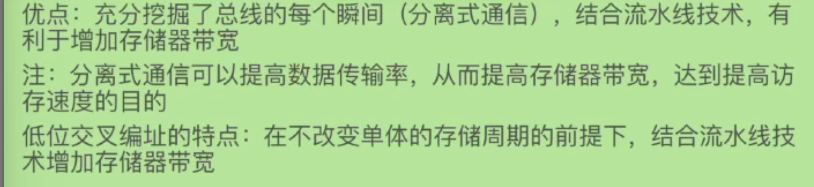

高位顺序编址方式

-

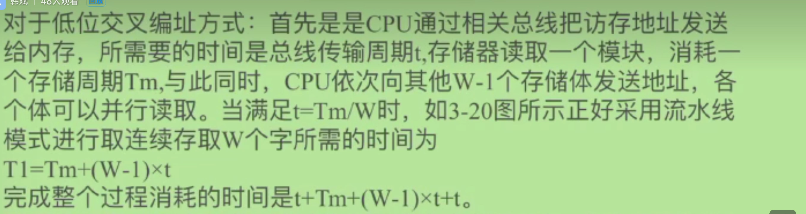

低位交叉编址

考点五:主存——Cache系统

1.存储器访问的局部性原理

-

时间局部性

-

空间局部性

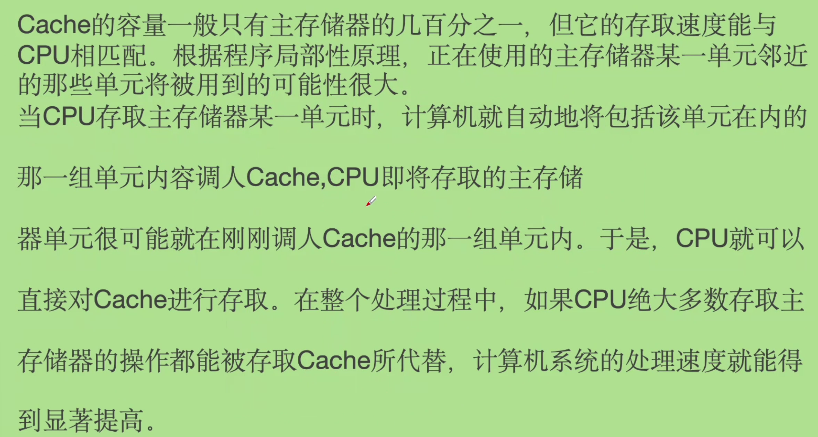

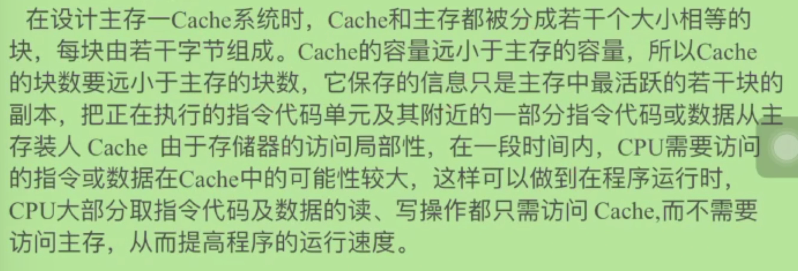

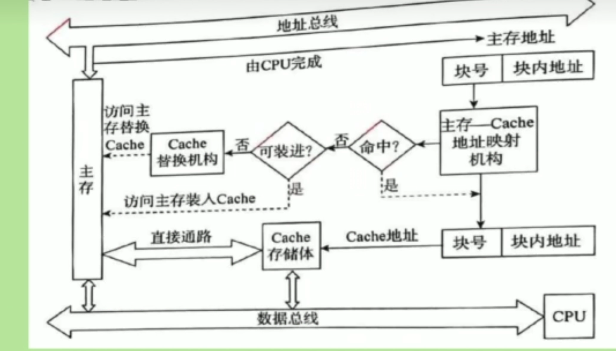

2.主存——Cache系统概述

3.Cache的工作原理

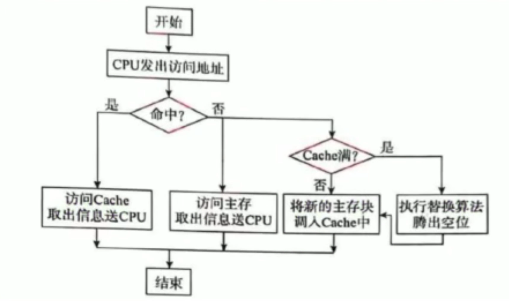

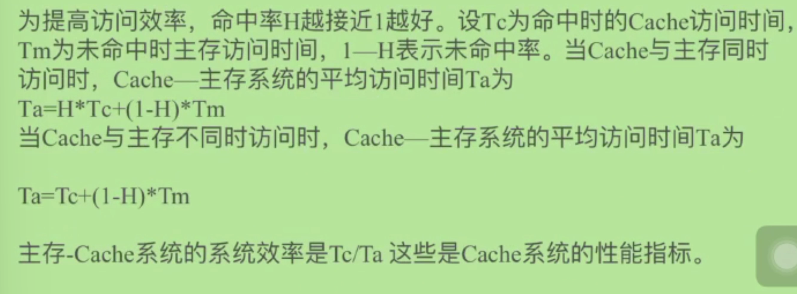

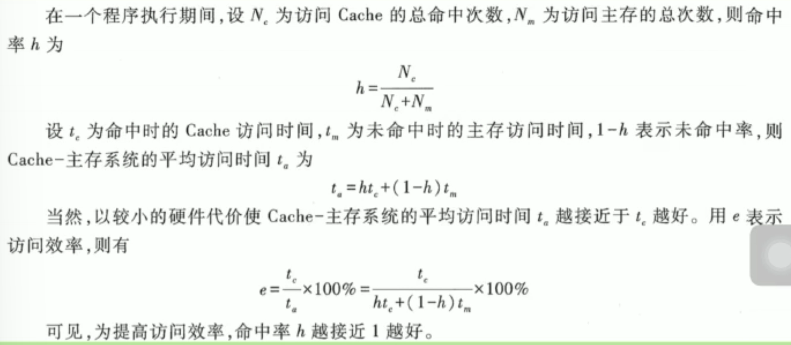

4.Cache的基本操作和性能

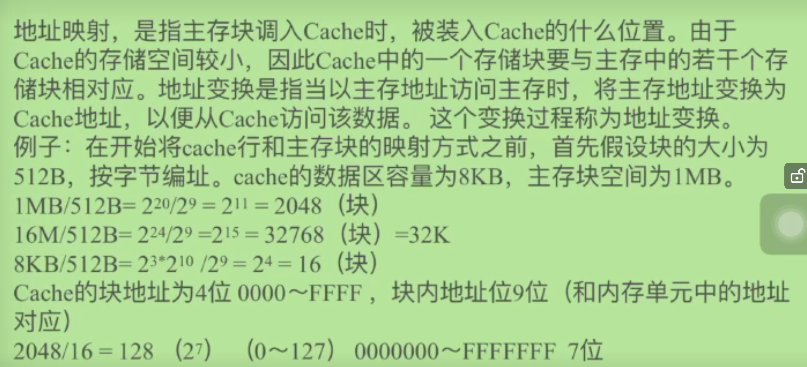

5.Cache和主存之间的映射方式

-

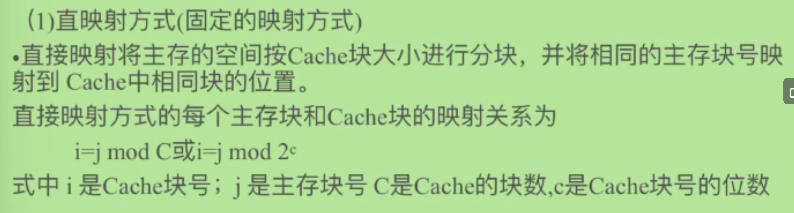

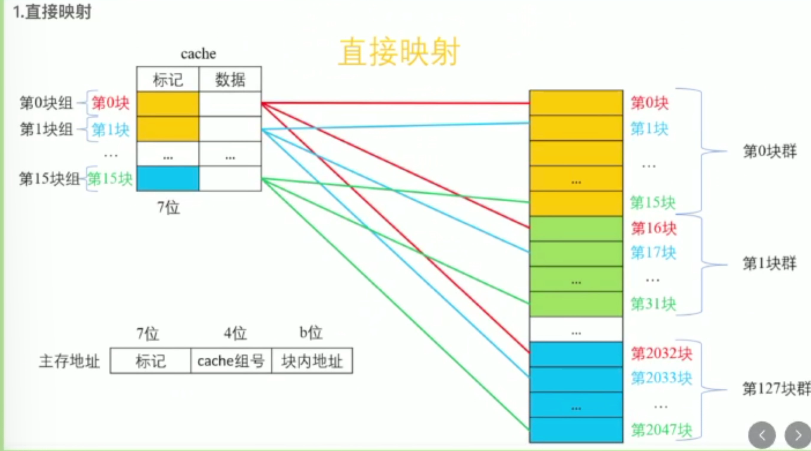

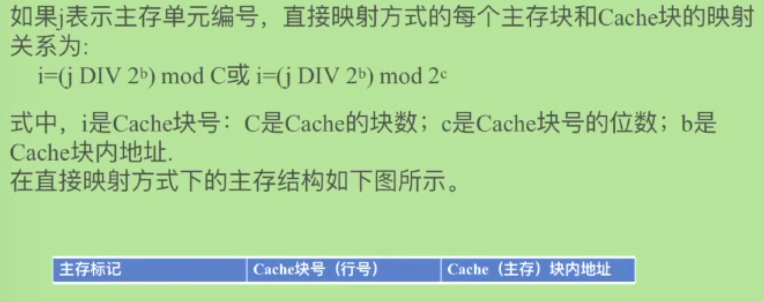

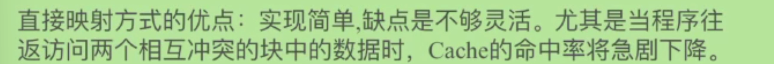

直接映射

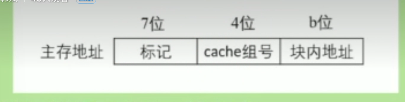

cache块号:看cache块的多少,用于表示组数索引的二进制位数

块内地址:cache块中有多少个存储单元(每单元1B)的二进制索引数

主存标记位:根据主存容量确定主存地址可表示的大小位数以此减去组号及块内地址

以此形成一条数据的完整地址

-

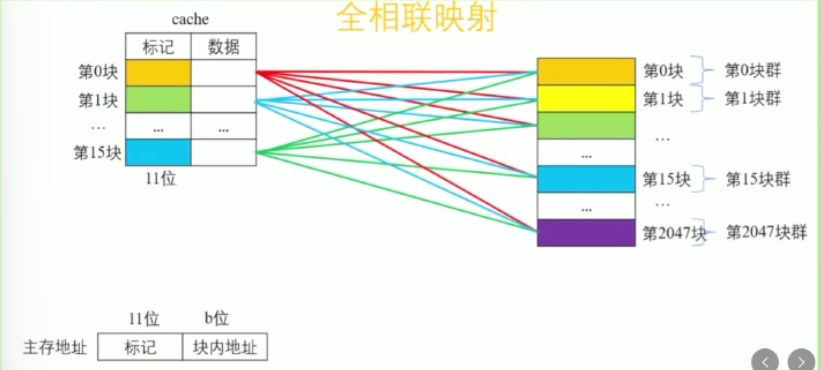

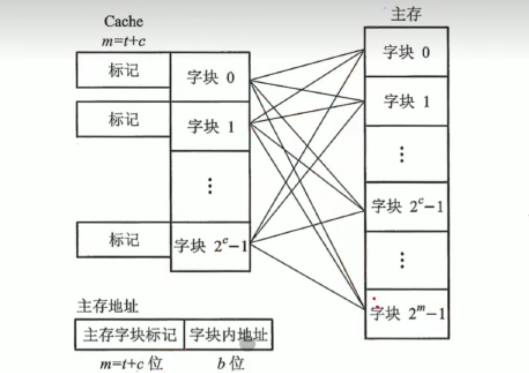

全相联映射方式(灵活性大的映射关系)

cache块大小就是主存块大小

-

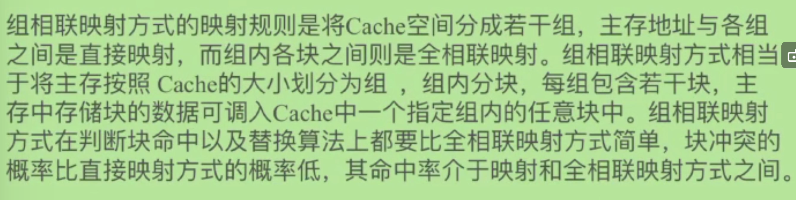

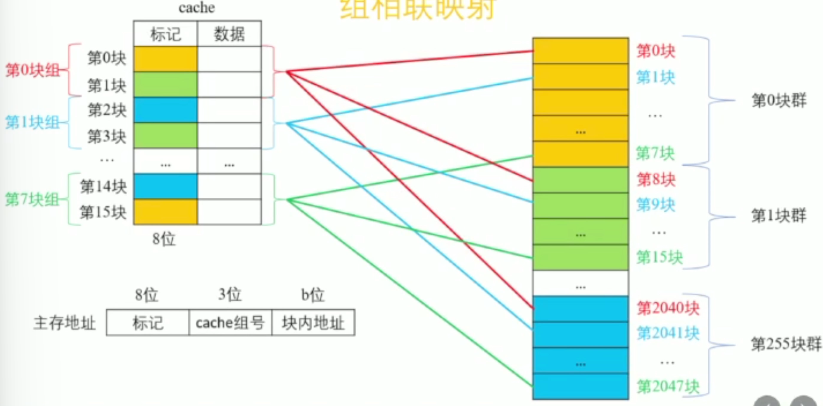

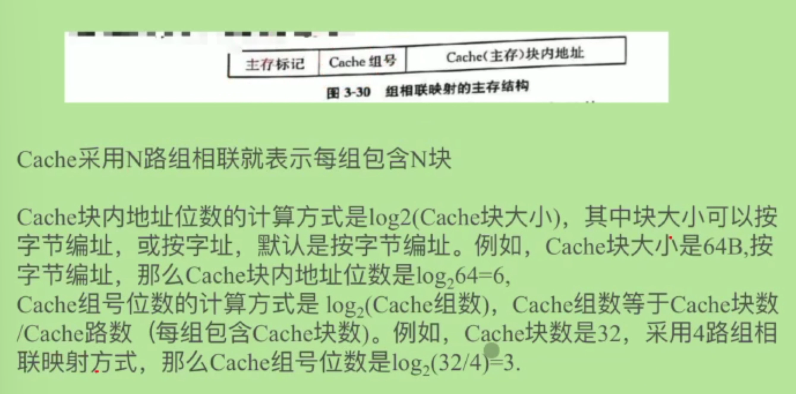

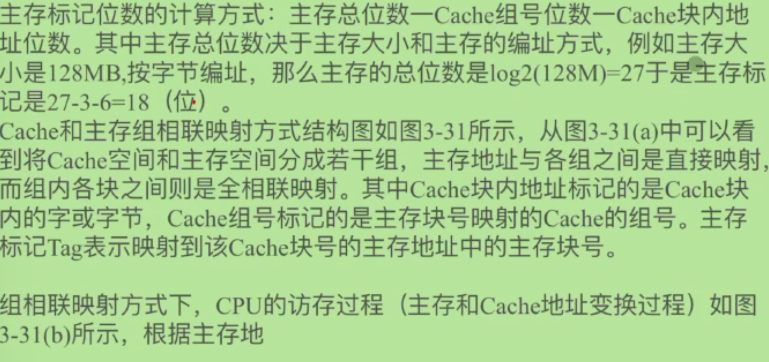

组相联映射方式(直接映射和全相联映射的折中)

6.cache中主存块的替换策略

位置被占,直接把整个单元替换掉

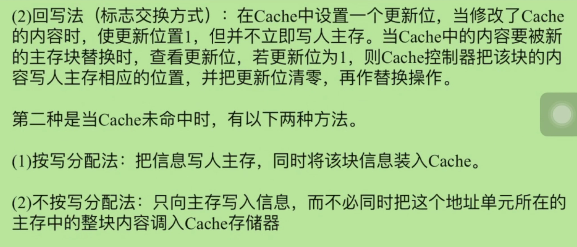

7.cache更新策略

不必整个替换cache块,修改部分数据

cache中数据与主存中不一致,更新一个数据

先取cache中数据的因此可以暂时不修改主存数据,当cache中被修改过数据要被替换时,需要把数据传回主存。

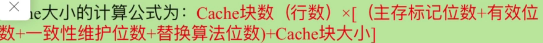

8.cache结构和大小计算

有效位为1位,确定数据是否有效

一致性维护位1位,也叫脏位,表示cache与主存数据是否一致 回写法需要

替换算法位: 一般不考虑

-

直接映射替换算法

不需要该位

-

组相联映射

\[\log_2N \]N为N路组相联

-

全相联

\[\log_2M \]M为cache块数

考点六:虚拟存储系统

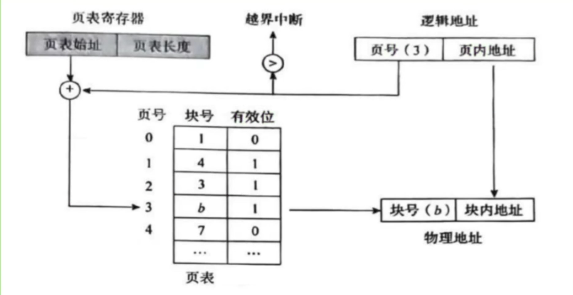

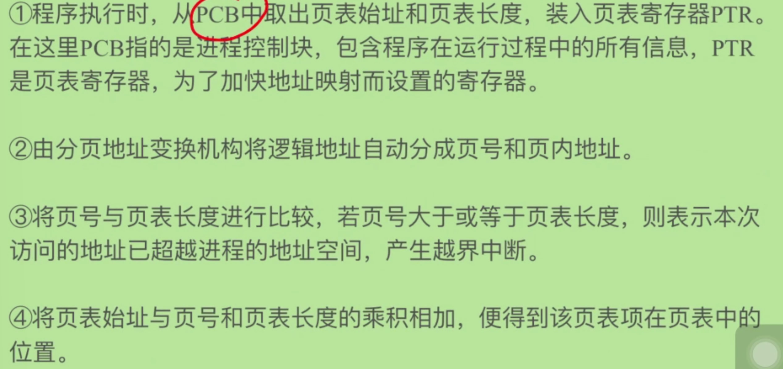

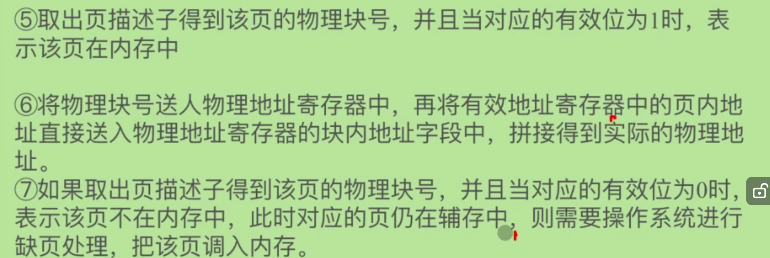

3.虚拟存储器的实现

-

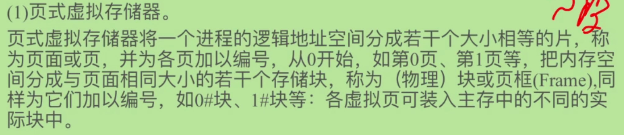

页式虚拟存储器

逻辑地址:由页号和页内地址组成

内存地址(物理地址):由块号和块内地址组成

页内地址和块内地址相同

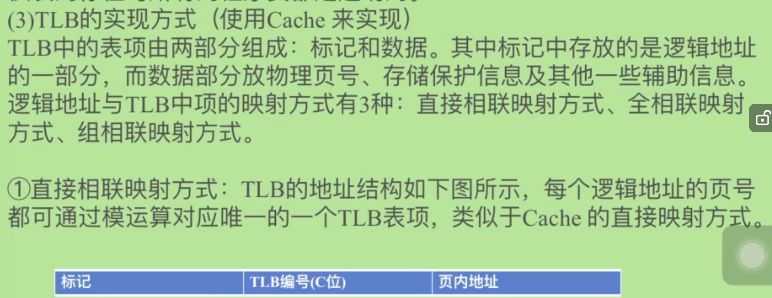

TLB快表

浙公网安备 33010602011771号

浙公网安备 33010602011771号