Verilog仿真实践

- Verilog必须掌握

- 逻辑仿真工具(VCS)和逻辑综合工具(DC)

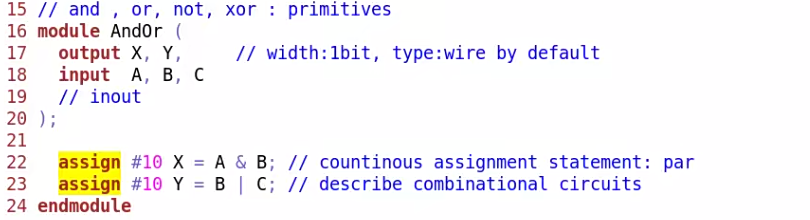

AndOR

module AndOr(

output X,Y,

input A,B,C

);

// A B进行按位与运算

assign #10 X = A & B;

// B C按位进行或运算

assign #10 Y = B | C;

endmodule

- #表示延时10个仿真单位

`timescale 1ns/1ps

- assign语句时并发执行的

- coding style - 在coding中不添加#延时

-

延时信息时不可综合的

- 使用RTL级写法

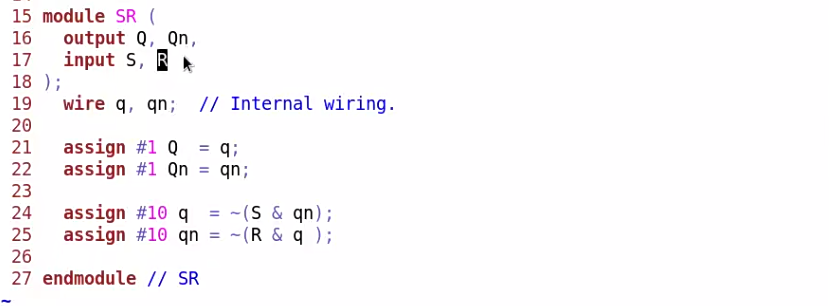

SR(latch)

- Coding之前,需要先写Design Spec

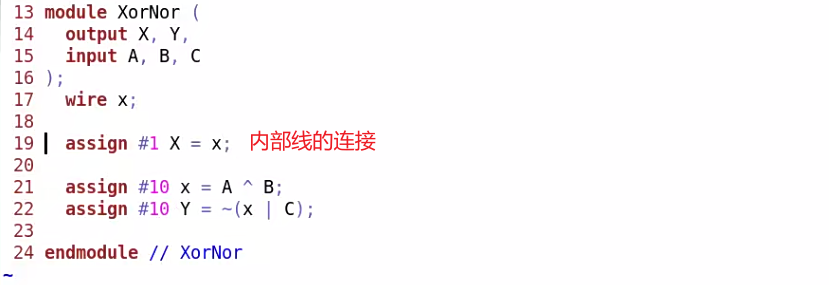

XorNor

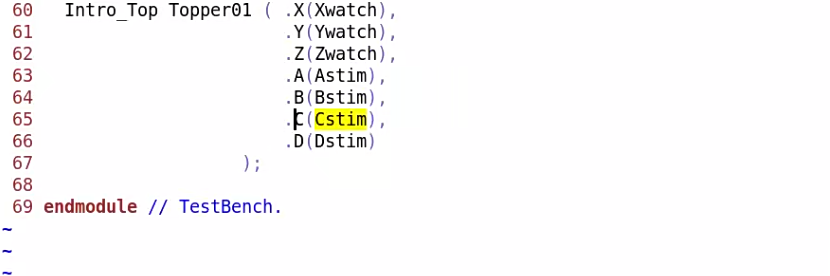

顶层

- 例化子模块,连接子模块

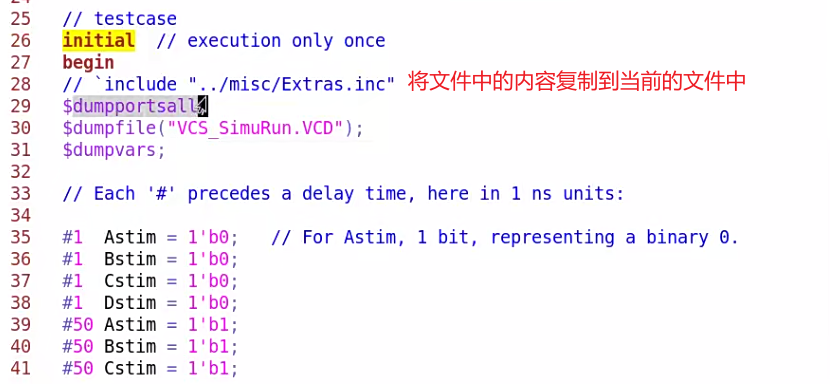

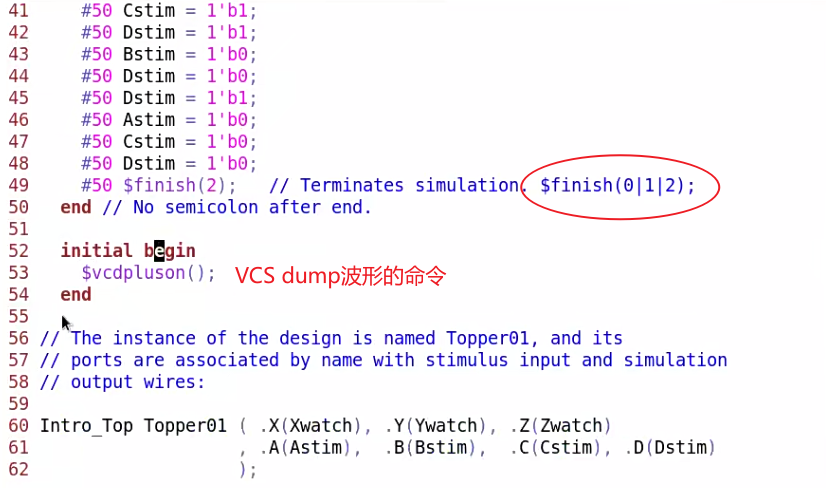

Testbench

- initial begin中左侧的变量使用reg类型

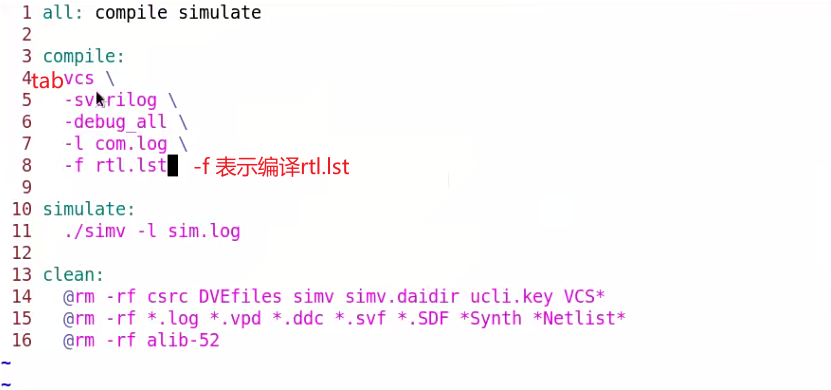

Makefile

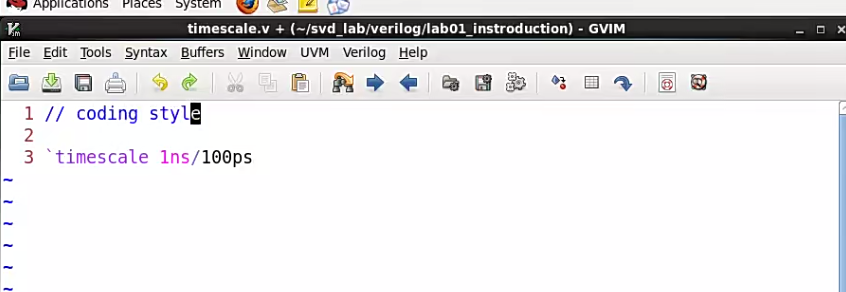

timesacle

- 可以将timescale单独写一个.v文件,然后包含在filelist.lst中

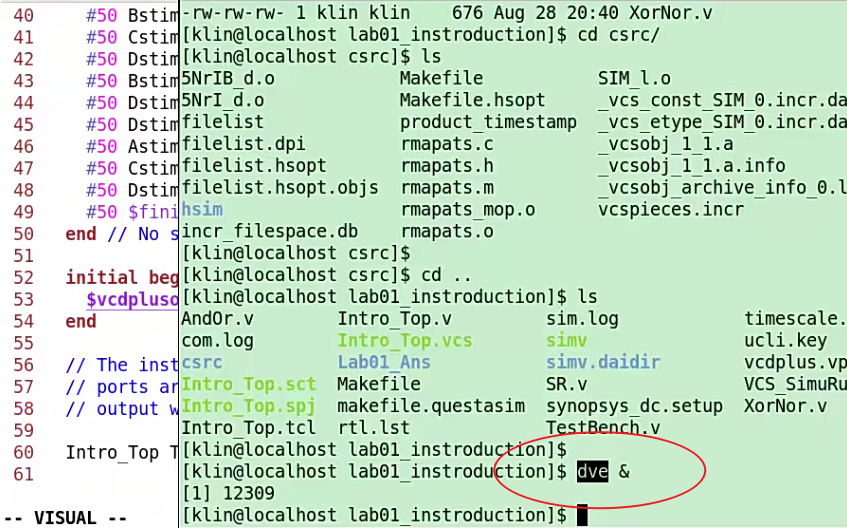

执行仿真

浙公网安备 33010602011771号

浙公网安备 33010602011771号