ASIC 功能验证VTB

目标

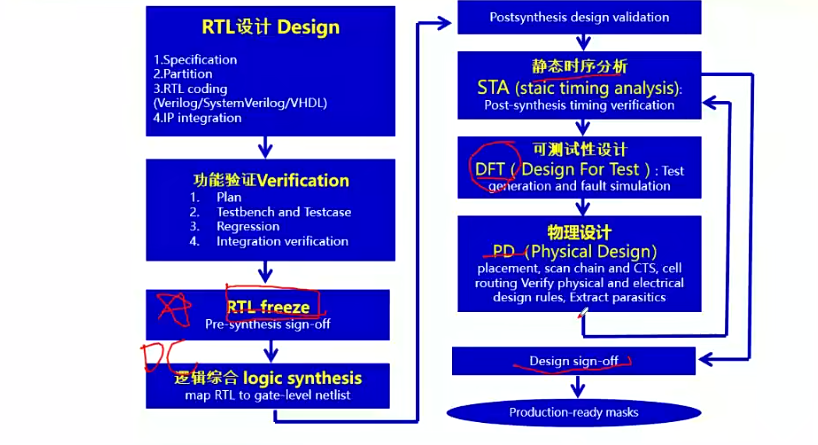

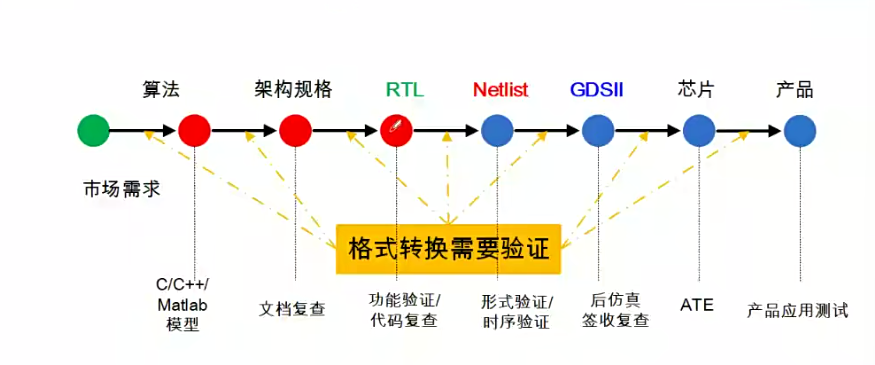

设计流程

- 验证设计文档和RTL code之间的关系

- RTL code(DUT) - 可以当作是一个黑盒,DUT内部是完全不可见的

- 白盒验证 - DUT内部RTL完全可见

- 灰盒验证 - DUT内部的RTL部分可见

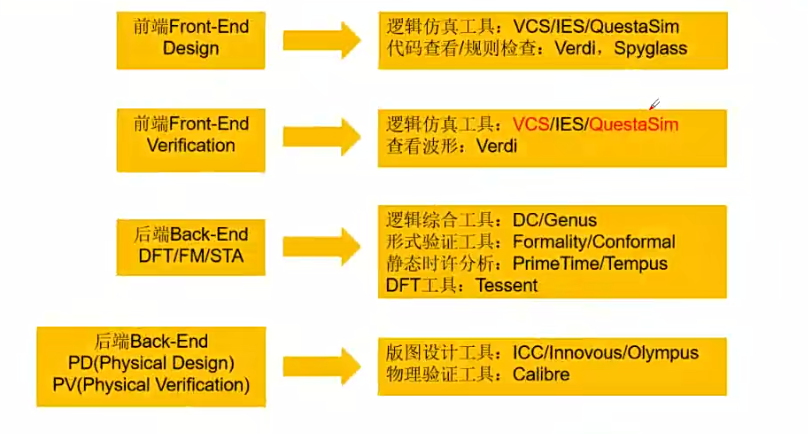

工具

主流EDA

设计节点

- DV - 特指是功能验证,主要是system verilog和UVM

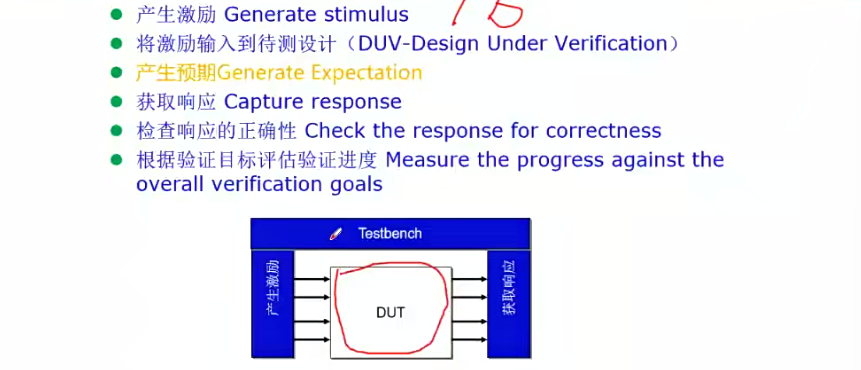

Verilog Testbench功能

- 验证的难点:能否将DUT所有信号的输入和组合都能找到

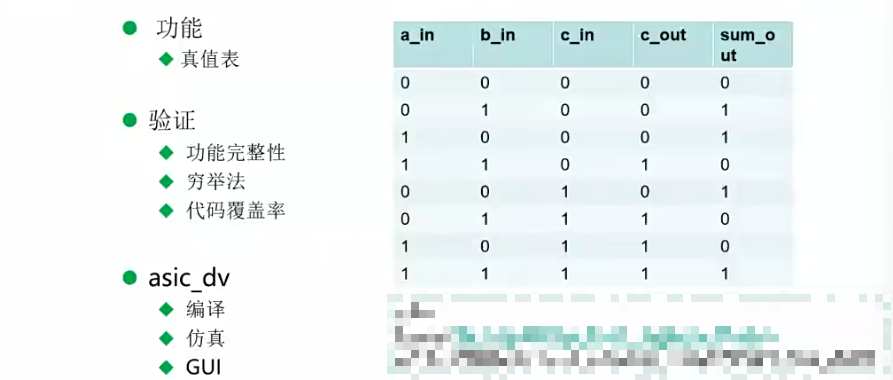

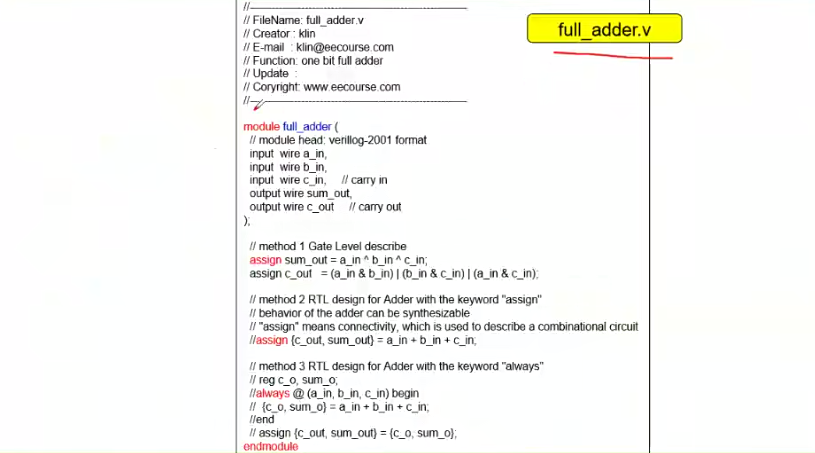

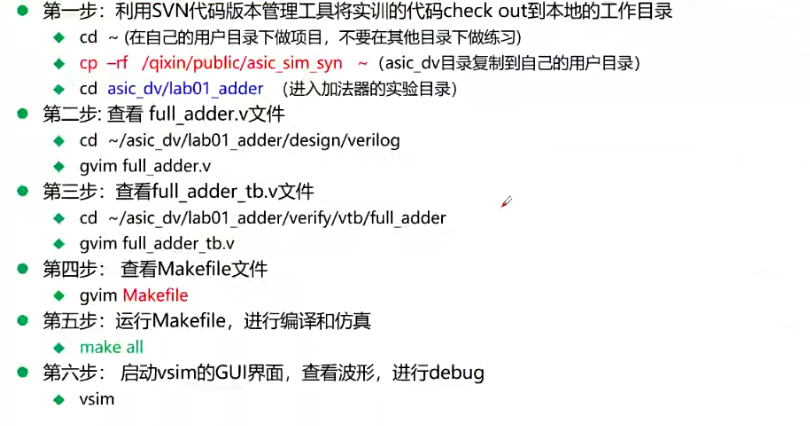

全加器验证

- 所有的输入可以穷举出来,从功能的角度进行验证

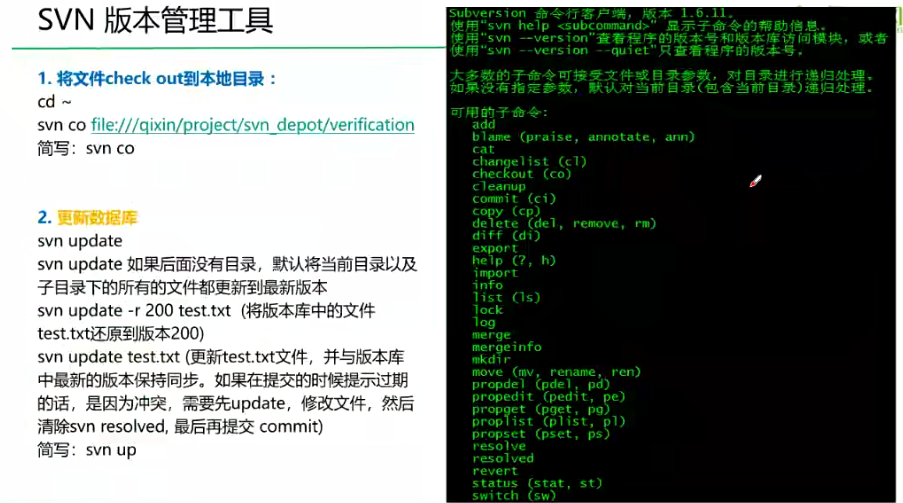

- svn - 代码管理工具

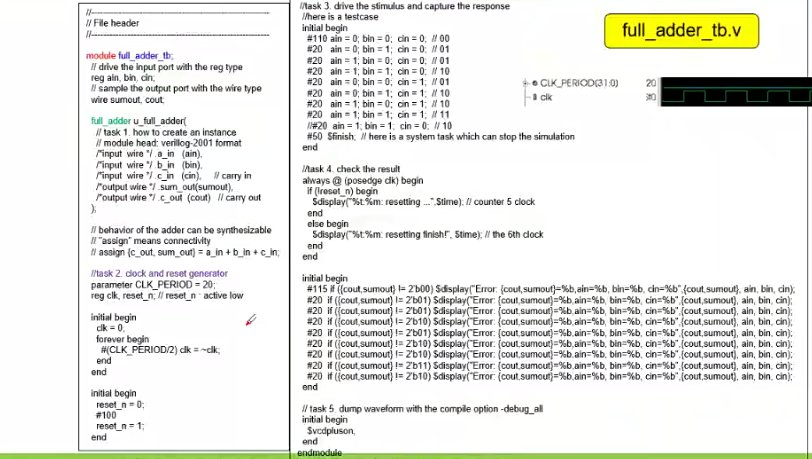

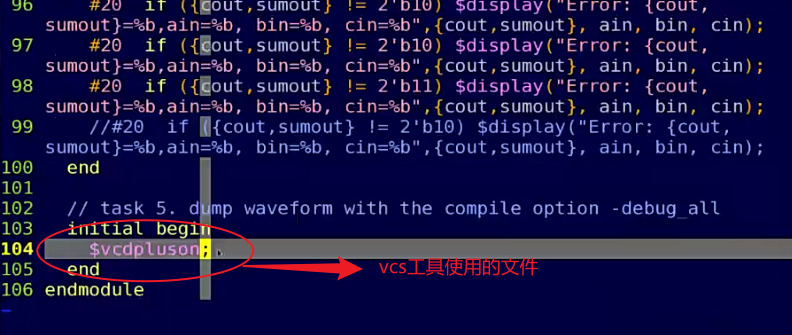

# vcs工具dump波形的语句

initial begin

$vcdpluson;

end

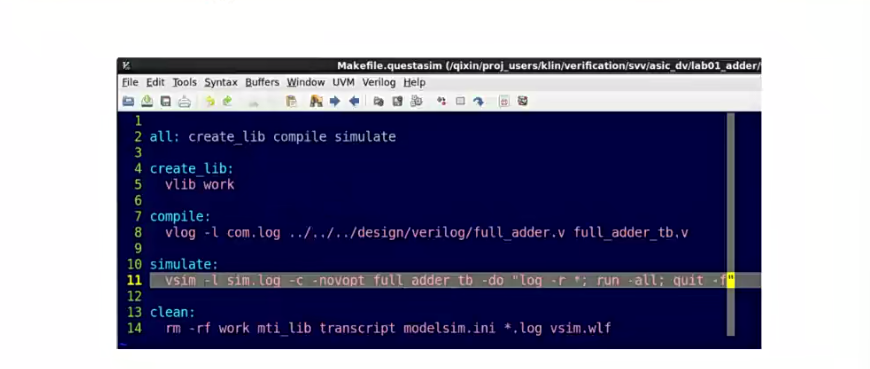

Makefile.questasim

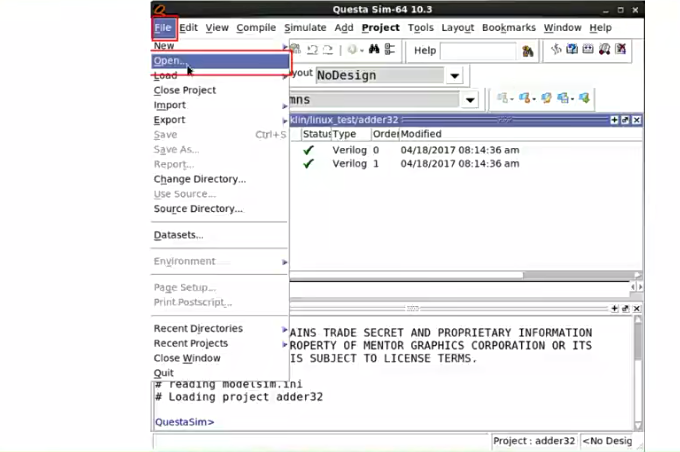

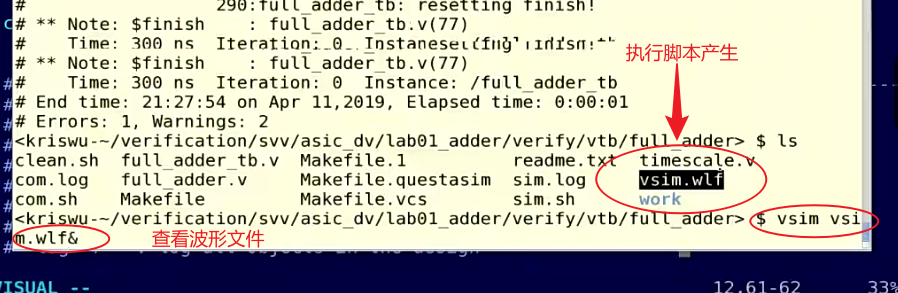

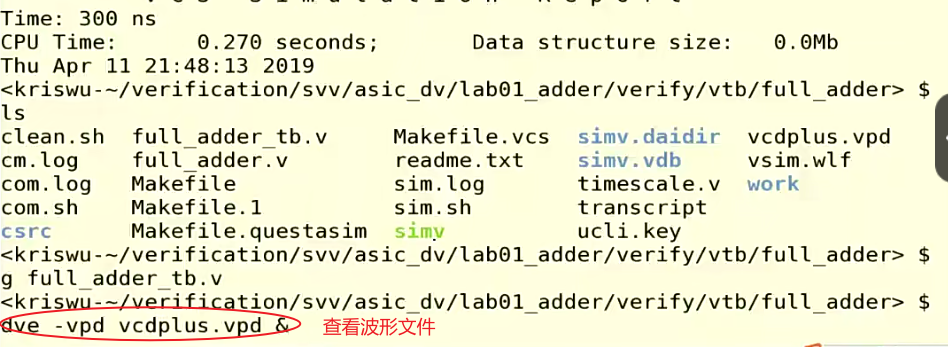

查看波形

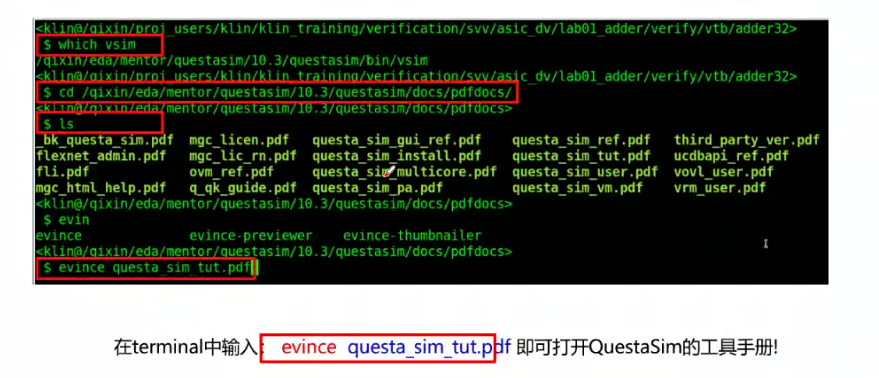

查看工具手册

使用help查看命令使用

服务器的使用方法

代码管理工具

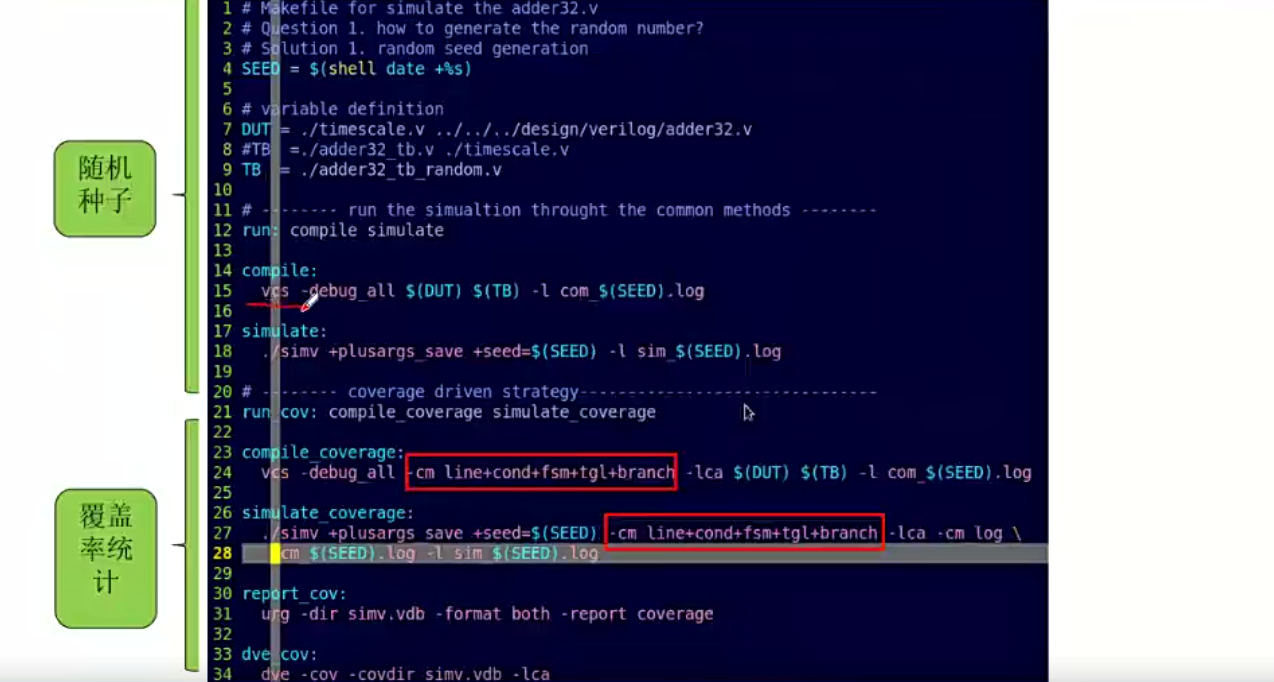

随机化验证策略

- $value

- $value$plusargs

*** 如何设置随机测试仿真的时钟周期?**

*** 当在随机仿真中出现错误,如何复现错误?**

Makefile.questasim

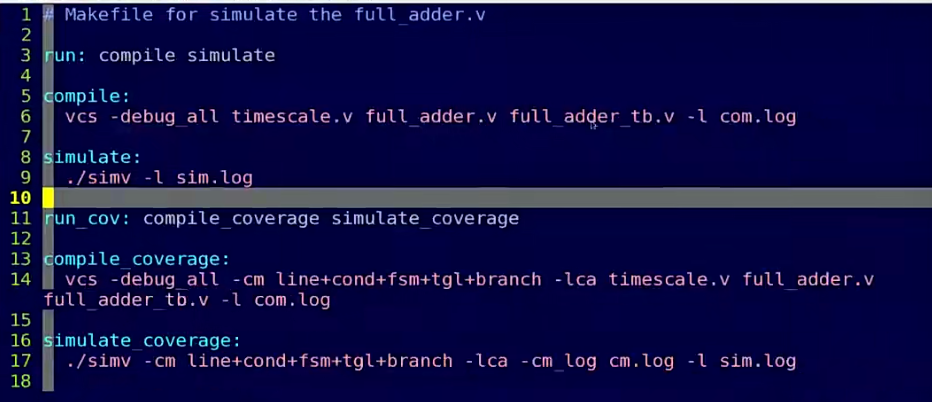

Makefile for VCS

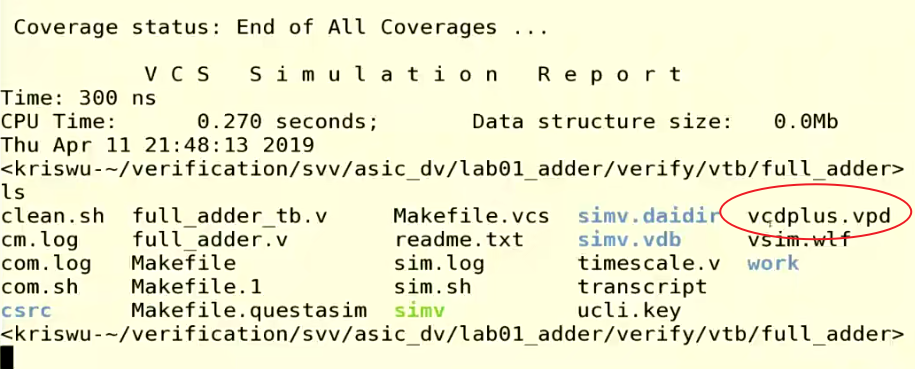

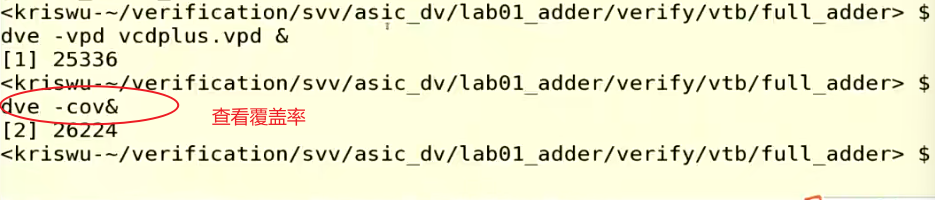

覆盖率驱动

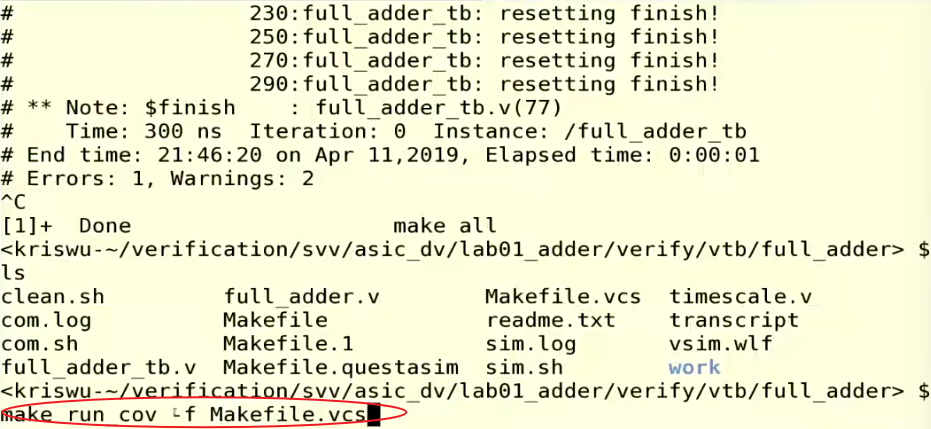

VCS仿真

浙公网安备 33010602011771号

浙公网安备 33010602011771号