DC - 设计和工艺数据

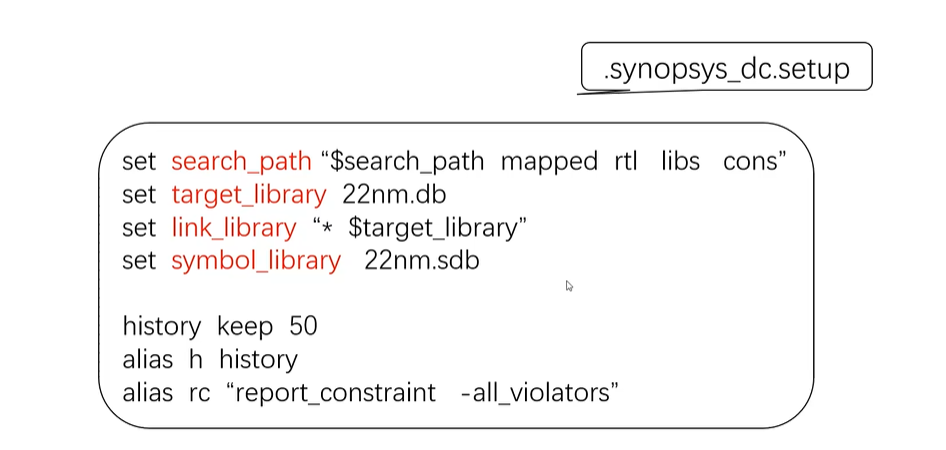

环境建立命令与变量

- 综合主要的三部分:RTL\目标工艺库\约束文件

- DC综合过程中timing > area,在时序满足的条件下进行面积优化

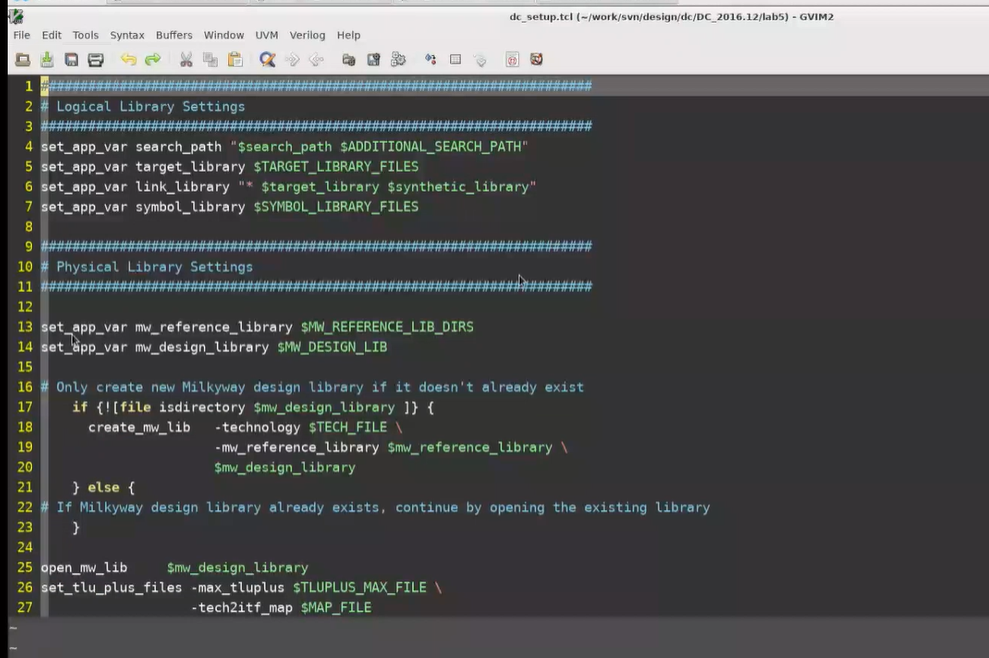

- RTL一般会映射为standcell(与非门),需要将对应的目标工艺库(target library)

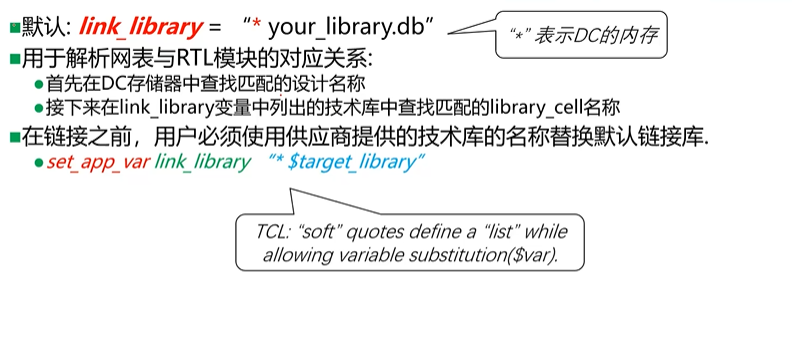

- 如果在RTL中不止使用了target library中的器件例化了其他的IP,这些IP不是以RTL的形式给出的,所以要设置link_library

- search_path - 类似于环境变量,在执行命令的时候,名令执行后到相应的路径中寻找执行的文件

- symbol_library - 符号库,电路的具体形式

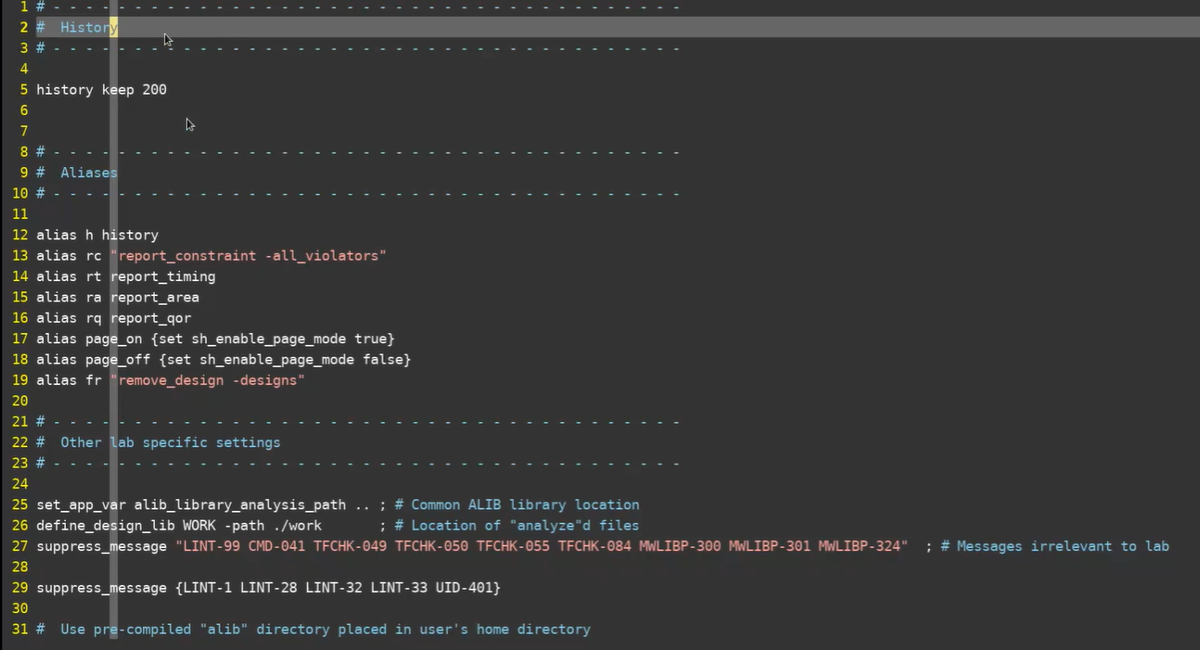

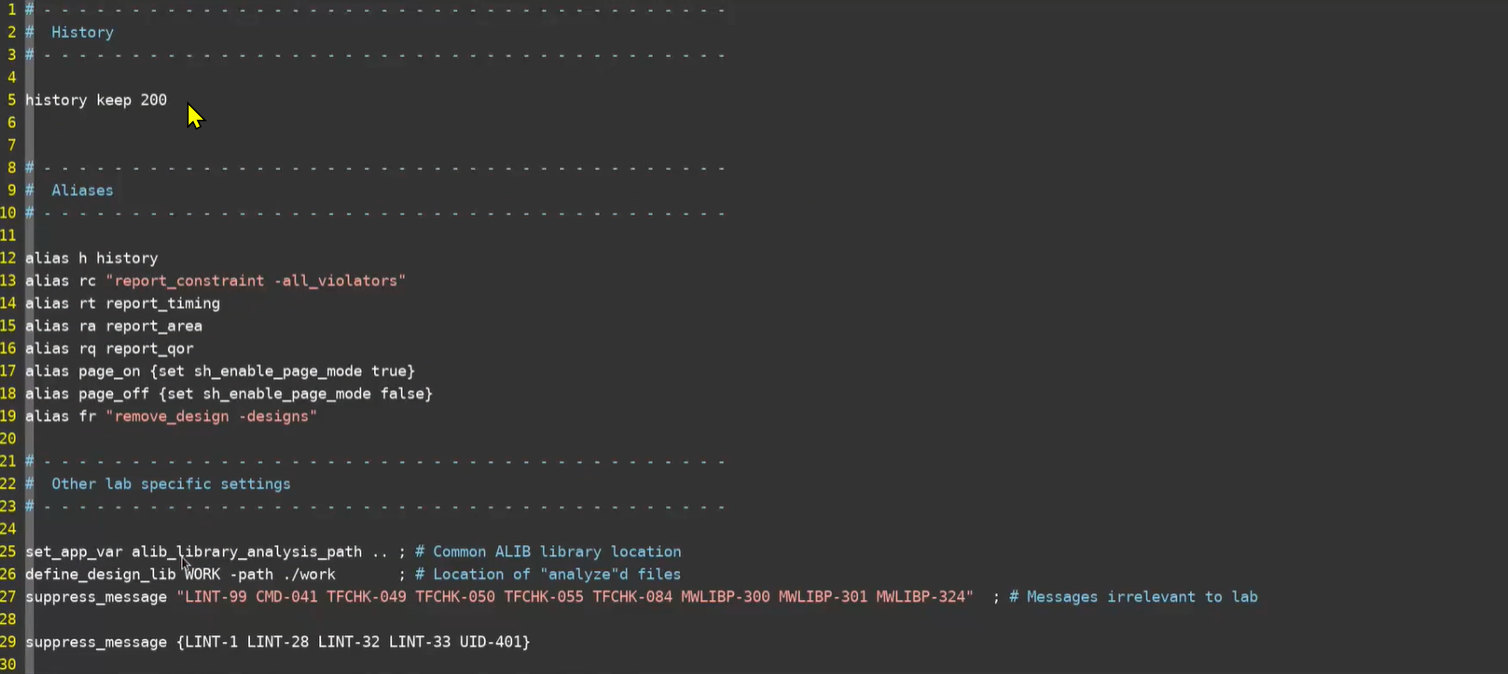

- 使用alias关键字将命令进行重命名

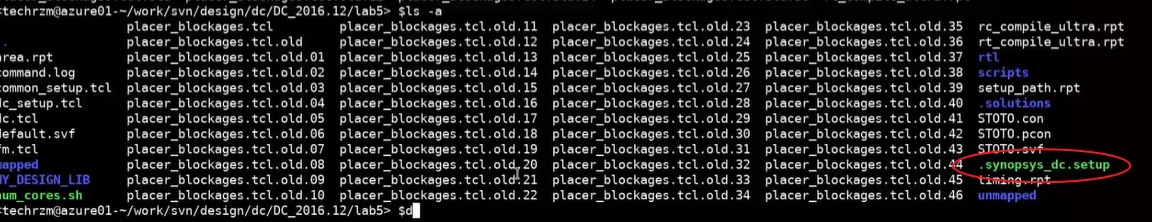

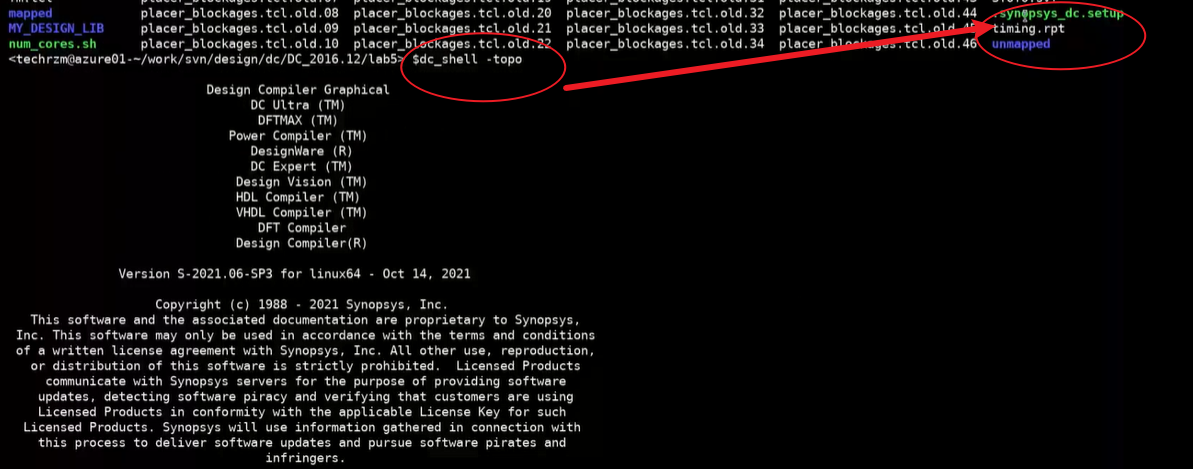

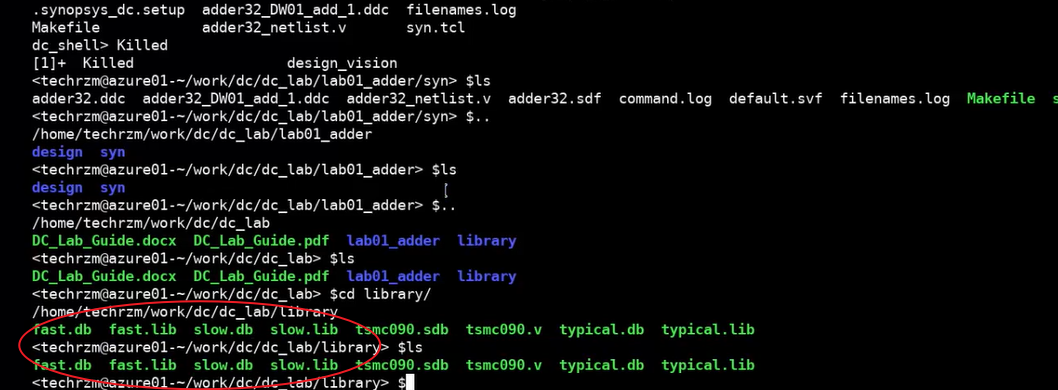

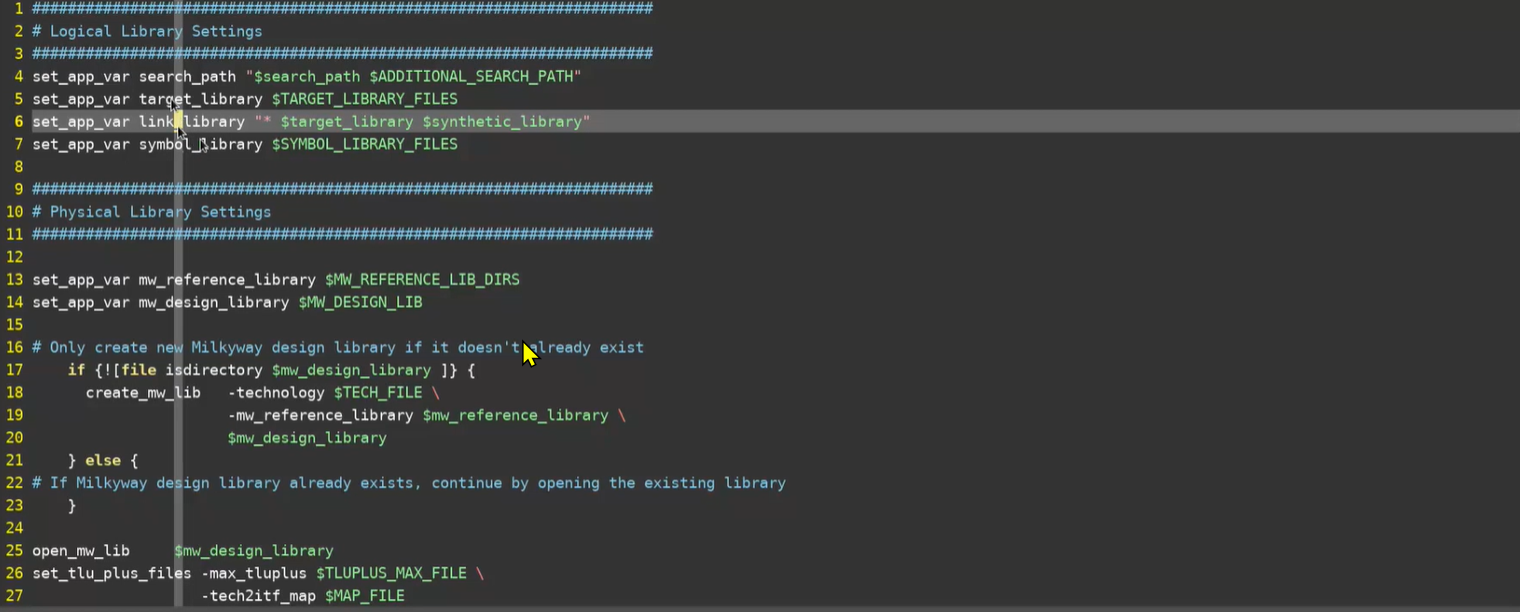

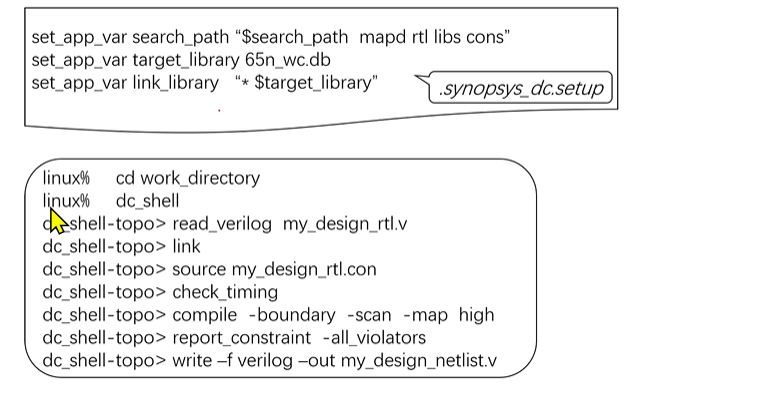

*.sysnopsys_dc.setup - 在启动dc_shell的时候,会自动进行执行

.sysnopsys_dc.setup

- .synopsys_dc.setup文件存在于三个地方:

1、dc工具安装路径下

2、用户的home路径下

3、脚本运行路径下

Loading RTL

打开DC并读取RTL文件

读入rtl代码

read_verilog rtl/my_design.v

读取VHDL RTL设计文件

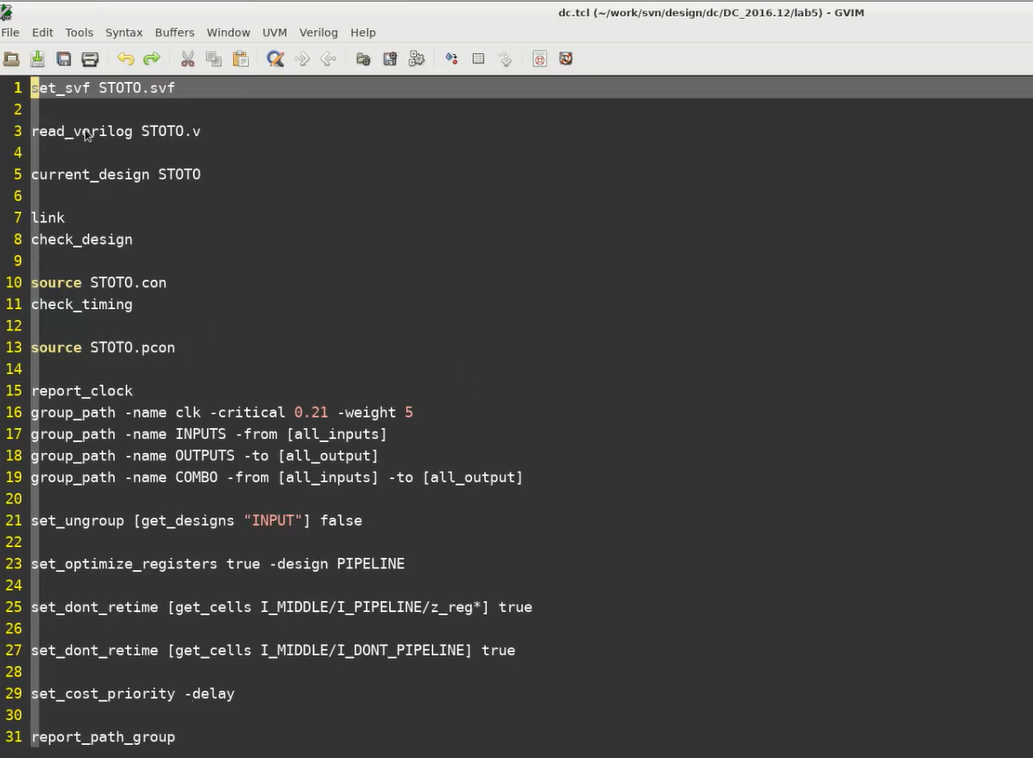

约束和编译未映射的RTL

- 没有设置target library,会进行报错

- source cons - 约束

- check_timing - 检查时序约束

- library文件有两种形式:一种是.db的形式,另一种是.lib的形式

- .db - 二进制形式,给DC工具进行使用

- .lib - 给工程师看的

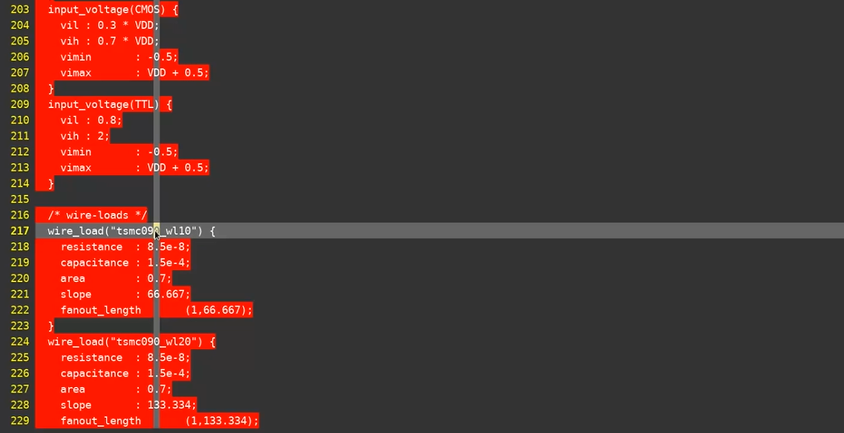

逻辑技术库实例

- 不同cell,面积大小不同,面积越大,驱动能力越强

如何使用target library?

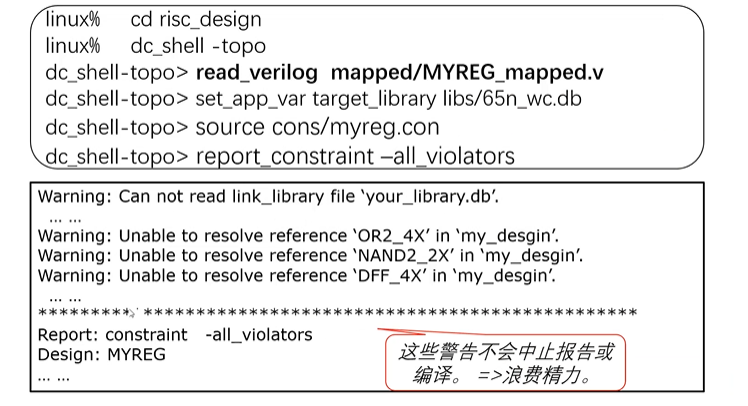

- printvar target_library - 打印名称,如果显示your_library,说明没有设置target library

- your library是在DC安装路径下的,如果没有被设置的target library覆盖表示没有设置target library

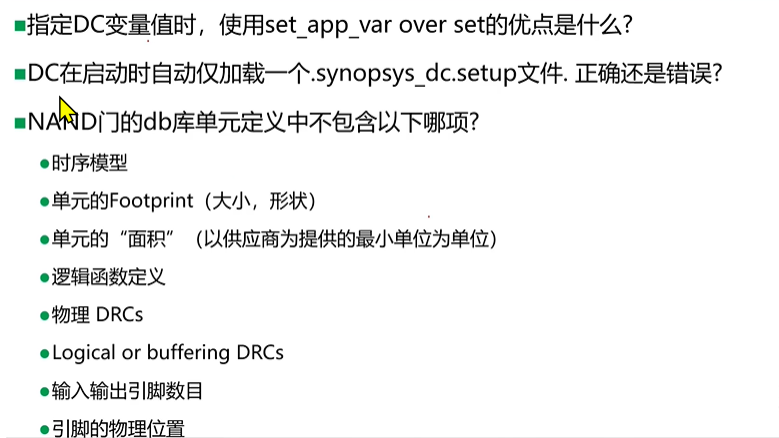

- set 和 set_app_var的区别:set指令是tcl脚本语言的指令,set_app_var只能针对DC内置的变量进行设定

退出前保存门级网表

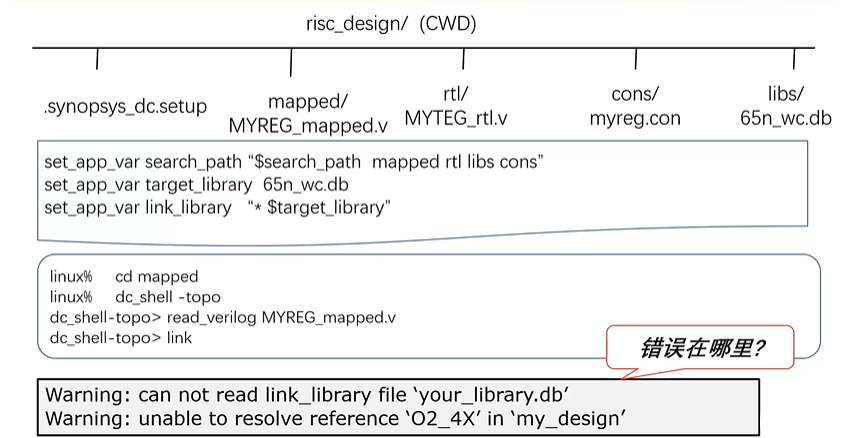

读取并分析网表

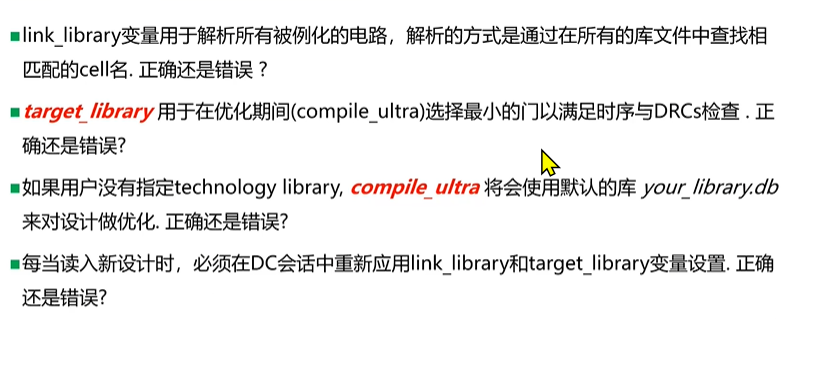

- 读取RTL代码的时候读入网表,没有设置link library,就会报错

- 读入网表之后需要找到对应的link library,从而找到所需要的门器件

使用link library解析reference

- *表示DC的内存,依次读取Top.v,B.v,c.v,三个模块是独立存在于DC内存中的,对Top进行link的时候如果需要B和C,就会在DC内存中进行寻找

- link library一般就是target library

在链接之前指定link_library

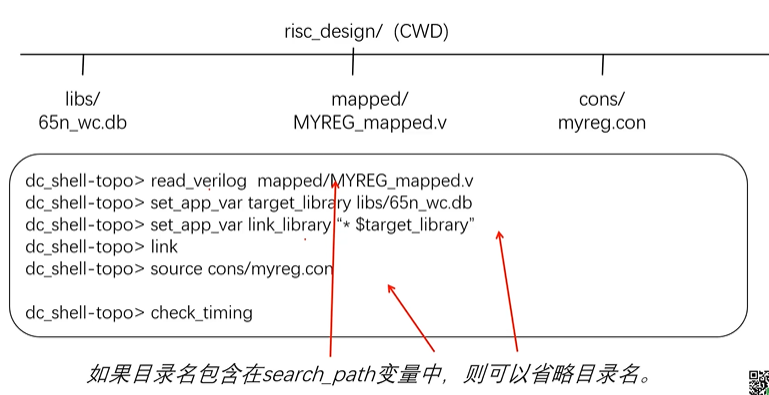

- 设置完target library和link library

- link - 将各个模块建立层级关系

- source cons/myreg.con - 读入约束脚本

- check timing

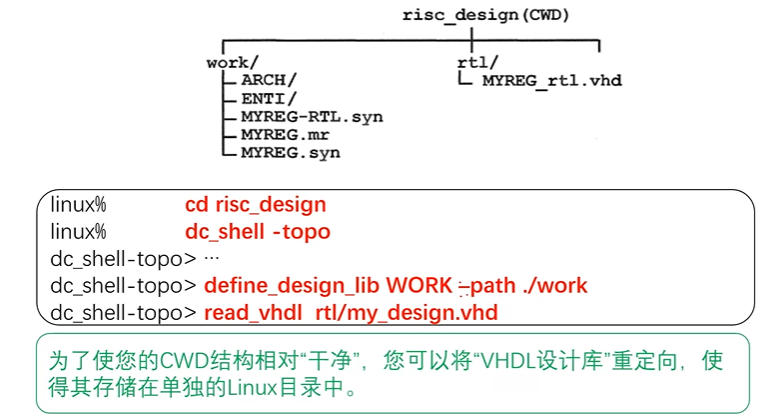

缩短文件路径

- 在risc_design路径下启动仿真,设置库的时候需要设置相对路径

可以设置search path

- dw - designware下的库

# 查看dc_shell的安装路径

which dc_shell

位于三个不同位置的启动文件(setup file)

dc安装目录下

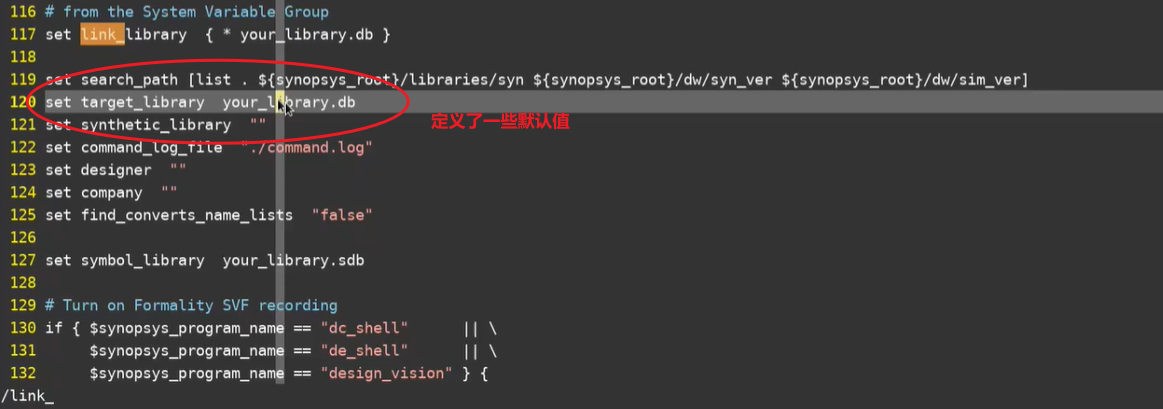

- 设置了一些默认值

user目录下

cd ~目录下

dc_shell启动目录下

- target library和link library会被覆盖

- search path是在原来的基础上进行追加

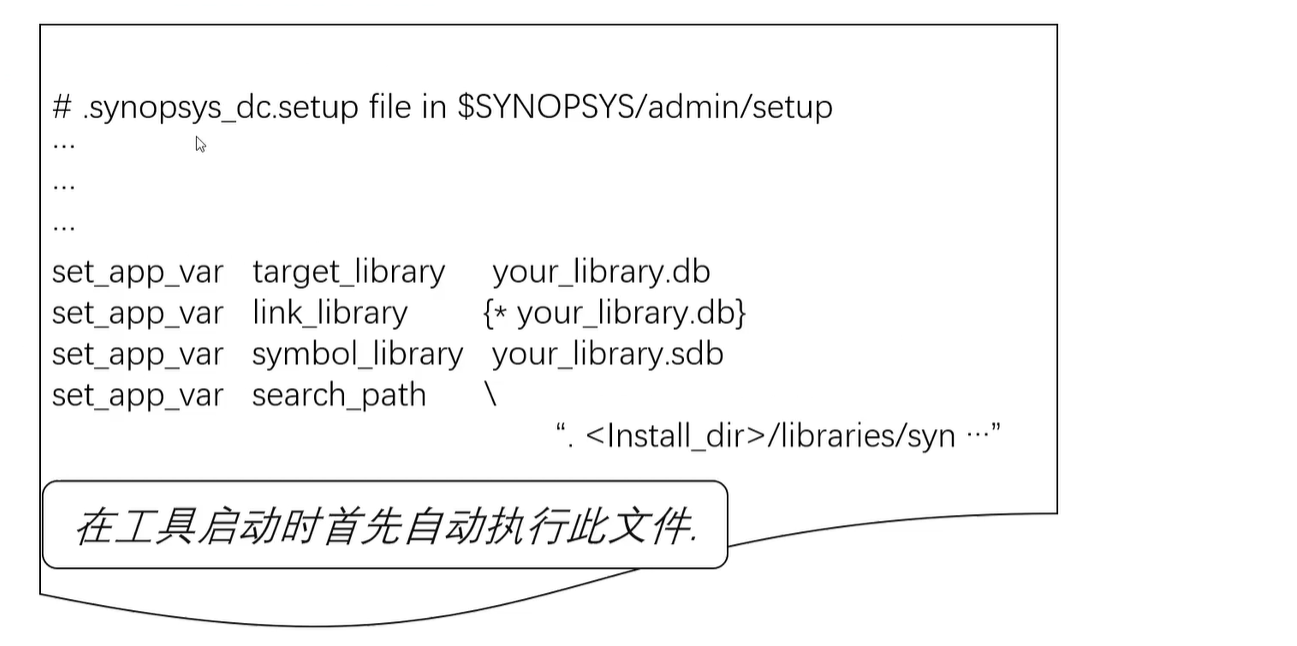

默认的DC setup file

CWD DC setup file

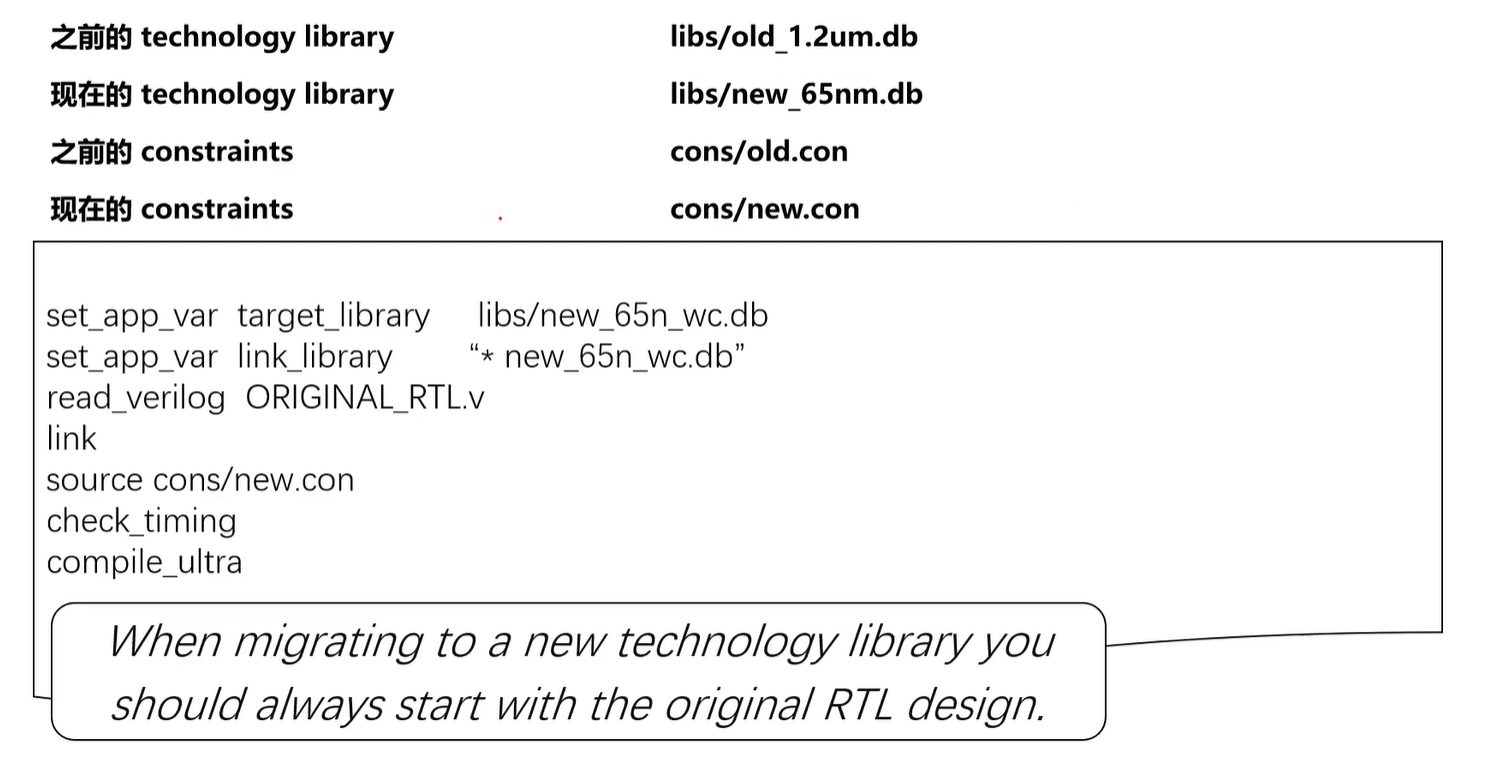

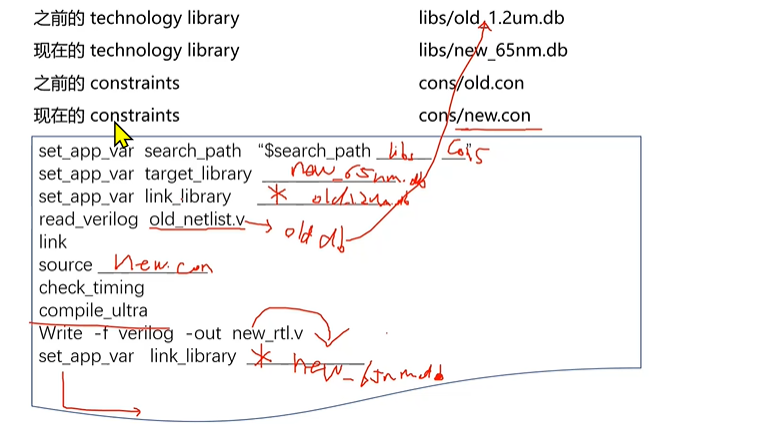

示例:替换技术库

- 假设有两个版本的设计,第一个版本用的1.2um的库,第二版是65nm的库;跑第二版的时候,target library和link library需要更新到新的库,约束也需要使用最新的

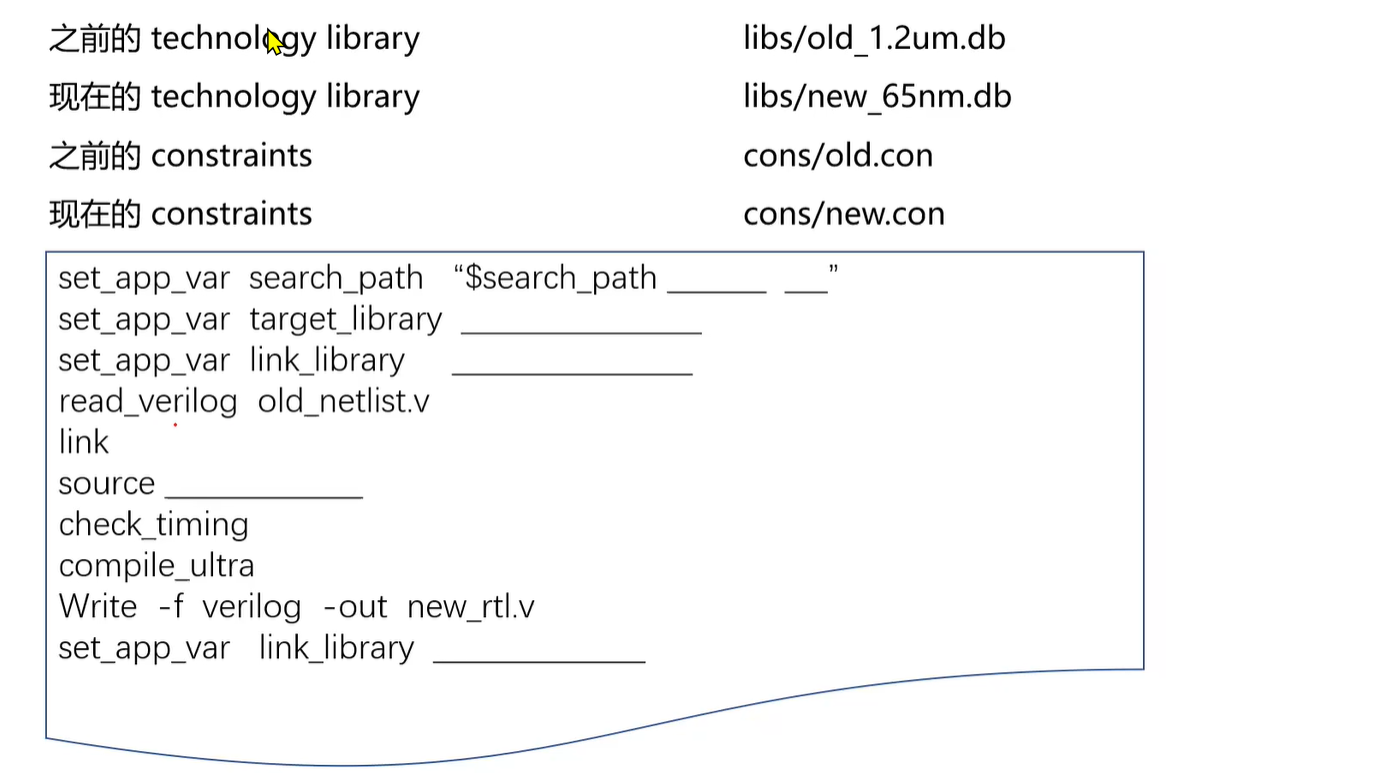

示例:输出网表

- 读入旧工艺的网表,如何输出新工艺的网表,旧的网表包含的是旧的standcell,设置link_library的时候,需要设置为旧的工艺的link library;

target library要设置成新的网表 - search path 设置为libs,cons

- 约束也需要设置为新约束

当前用到的命令

练习:库文件的建立

测试

- 对对对错

- 扇入扇出\电容\大小\面积\逻辑函数定义

- 不含形状

- 包含logic DRC不包含物理DRC

- 不含引脚的物理位置

层次化设计

- 顶层模块包含多个子模块

- A,B是以RTL形式存在

- RAM以库的形式存在(.db文件)

- encoder,decoder以网表的形式存在

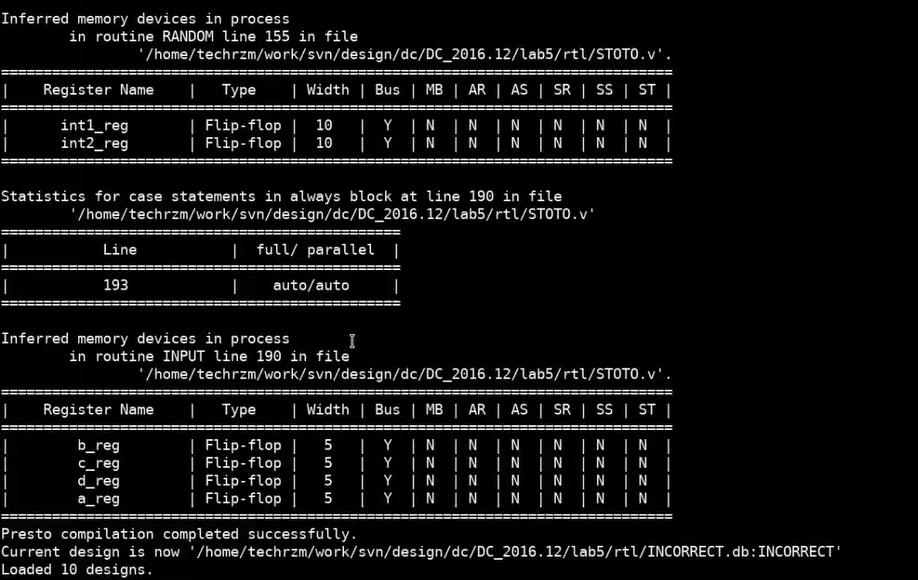

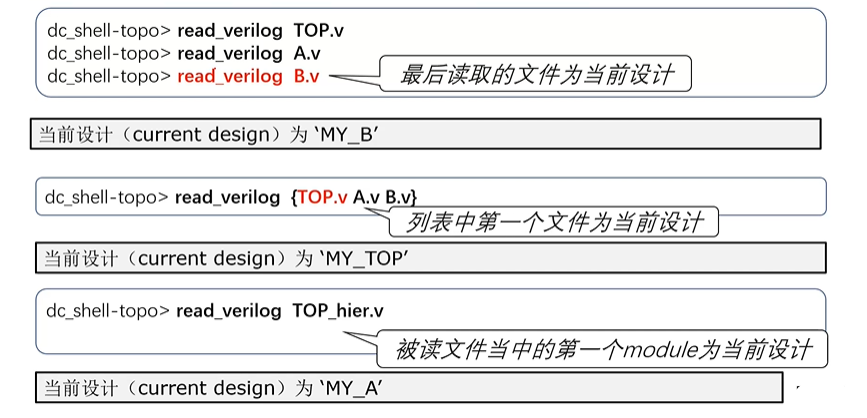

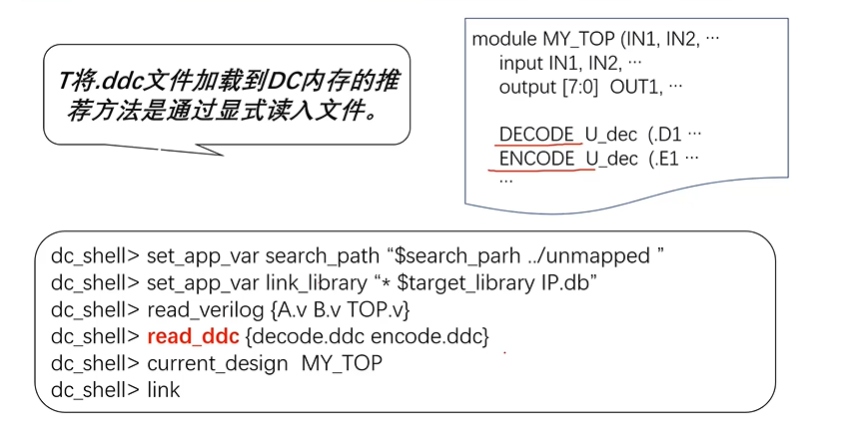

读入层次化的RTL设计

- current design - 读入多个设计,需要指定一个设计作为top顶层进行

- 不显示指定current design - 读入的最后一个RTL作为current design

- 以列表的形式读入 - 第一个RTL作为current design

- 读入的.v文件中包含多个module - 其中第一个module作为current design

指定current design

- 指定current design - 是以module名字指定的,不是指定文件的名字

- 在link之前指定current design

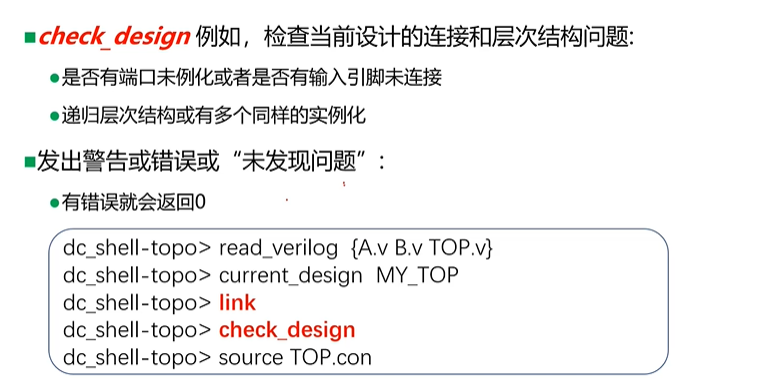

在link之后check_design

- check是否有输出引脚悬空,容易出现未知错误及亚稳态

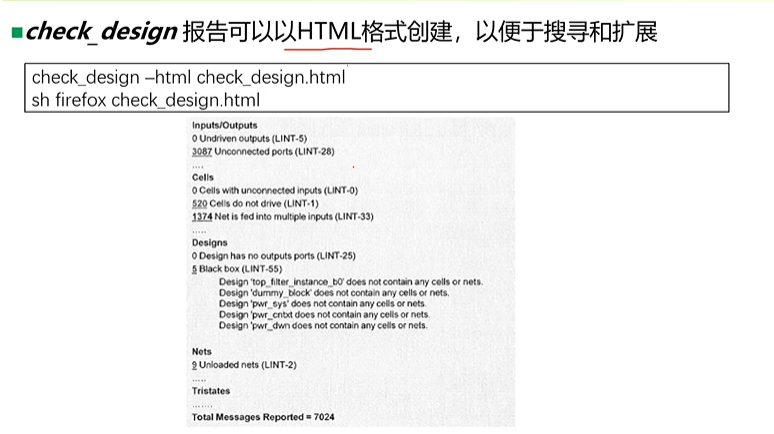

基于HTML的check_design报告

使用analyze & elaborate读取设计

- 使用这种方式不需要进行指定current design及link

使用elaborate修改参数

- 不修改RTL,使用elaborate可以直接修改参数

解析IP或者宏库单元

读取.ddc文件

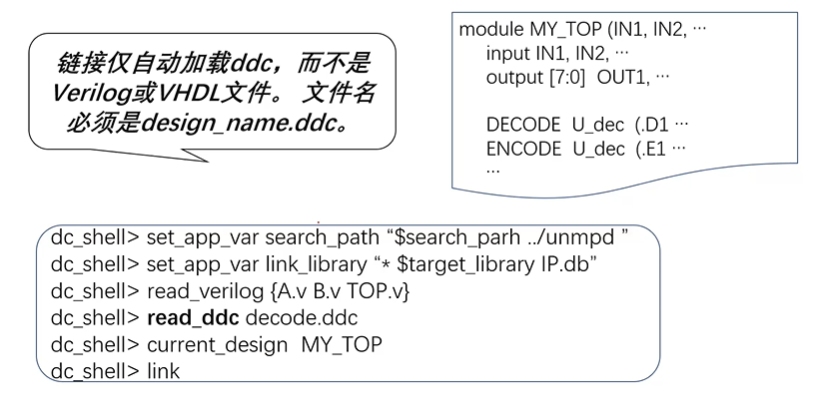

自动加载.ddc:不推荐

- ddc是二进制文件,只有dc识别

浙公网安备 33010602011771号

浙公网安备 33010602011771号