第十三课时:创建基本的时钟周期约束

1. 创建时钟的约束

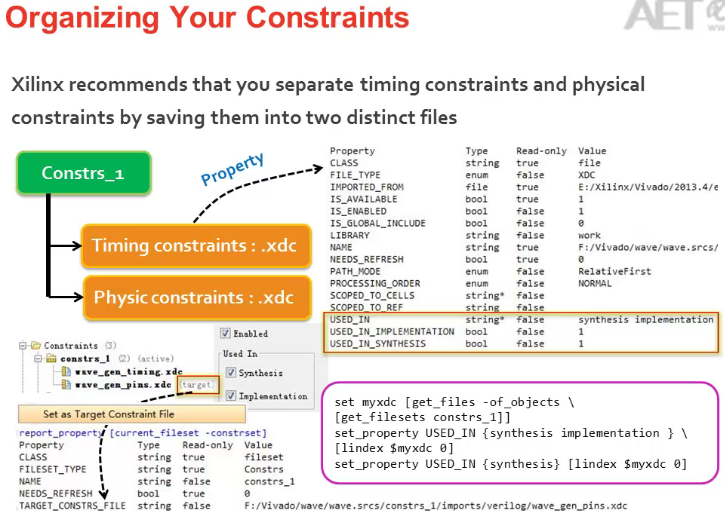

时序约束是综合和实现都要用到,有两个约束文件,其中一个是target

我们对约束进行设置的话,默认将保持到target

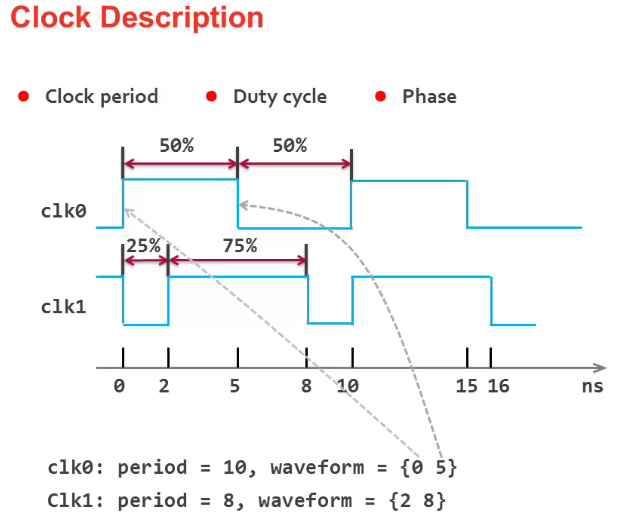

2. 时钟的描述

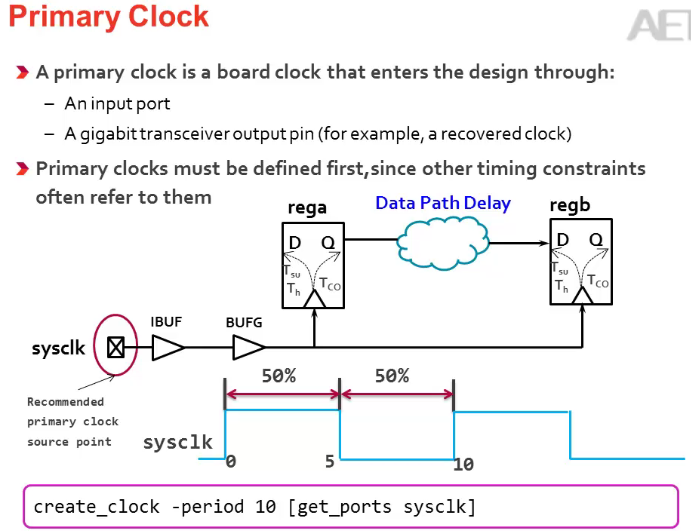

3. Primary Clock

通过IBUFG连接到FPGA内部的元件

缺省都是纳秒

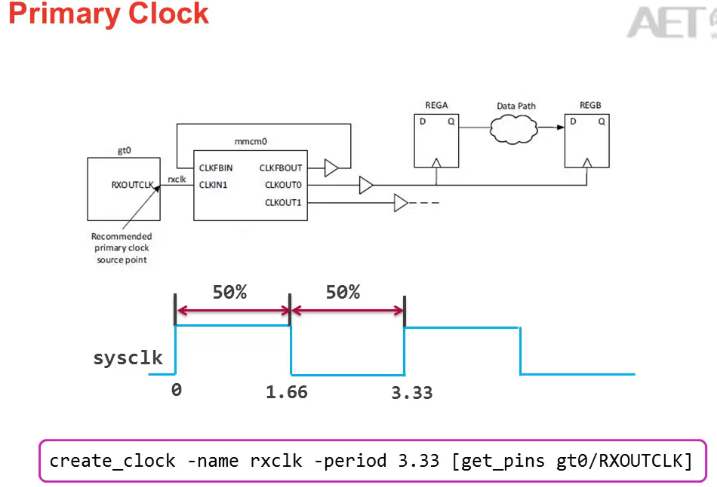

4. 用在gigabit

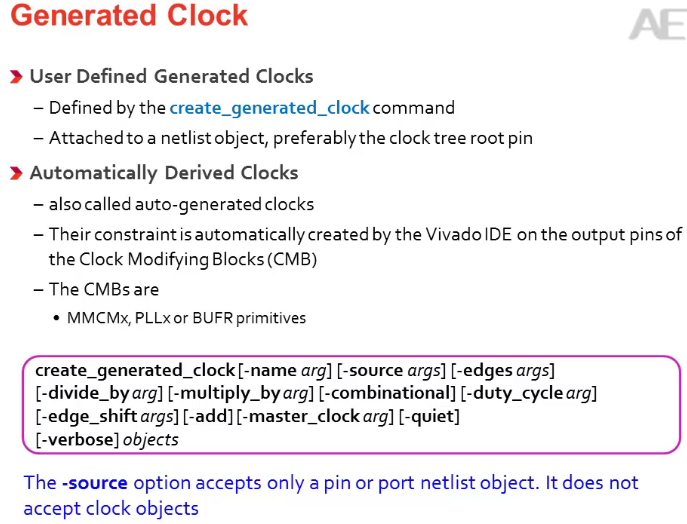

5. 生成时钟

source只能是pin port

create_generated_clock

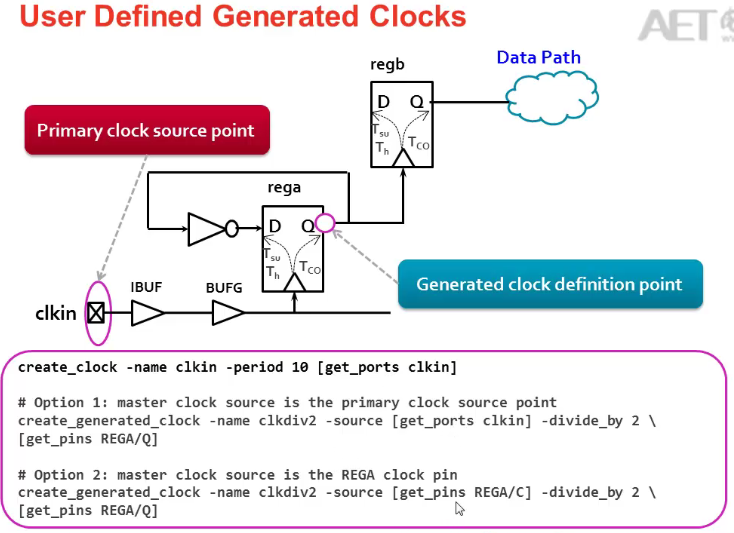

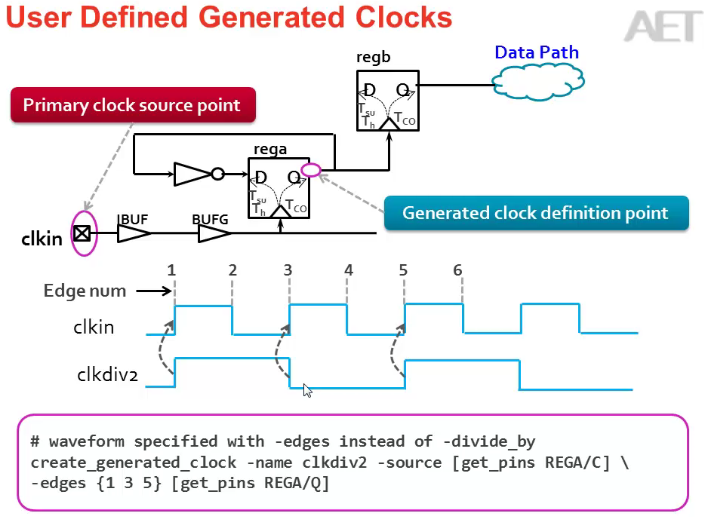

5.1 用户自定义时钟

create_clock -name clkin -period 10 [get_ports clkin]

create_generated_clock -name clkdiv2 -source [get_ports clkin] -divide_by 2 [get_pins REG/Q]

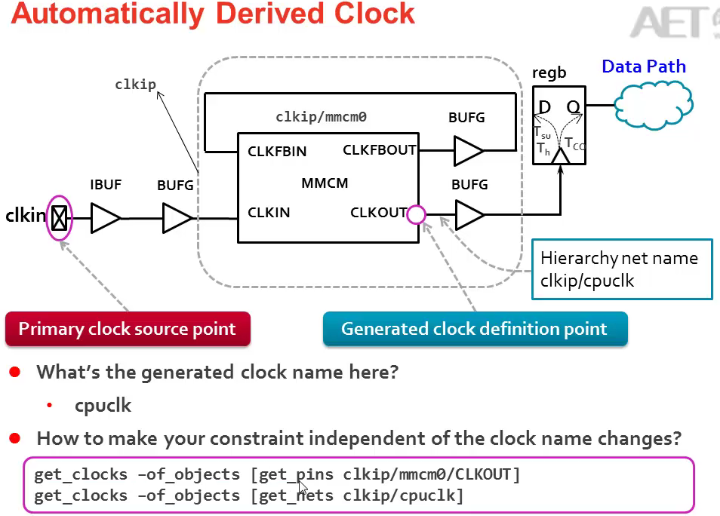

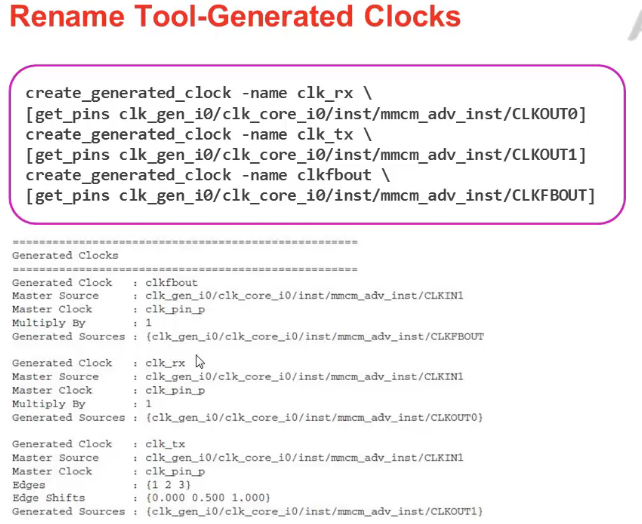

5.2 自动生成的时钟

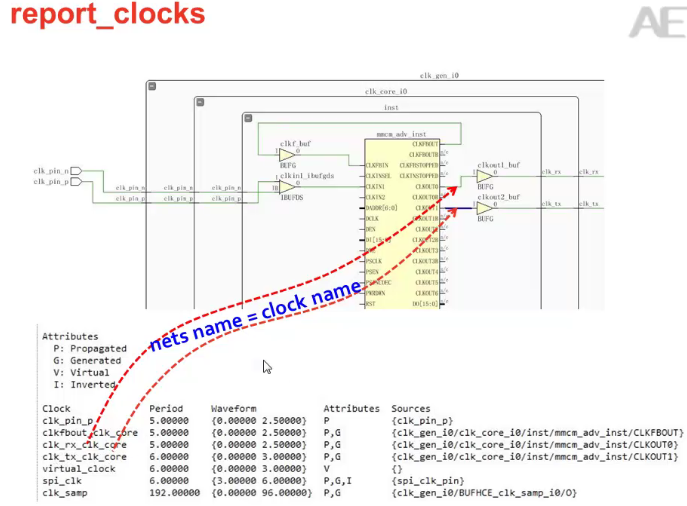

6. 报告时钟

显现当前的所有时钟

name name = clock name

网线的名字将呗命名为时钟的名字

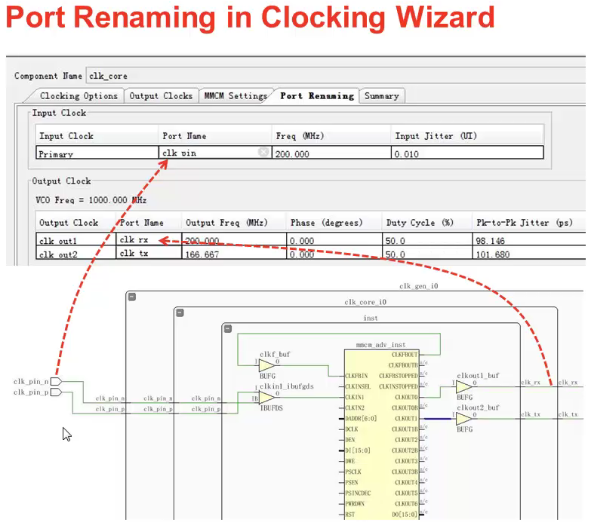

7. 时钟重命名

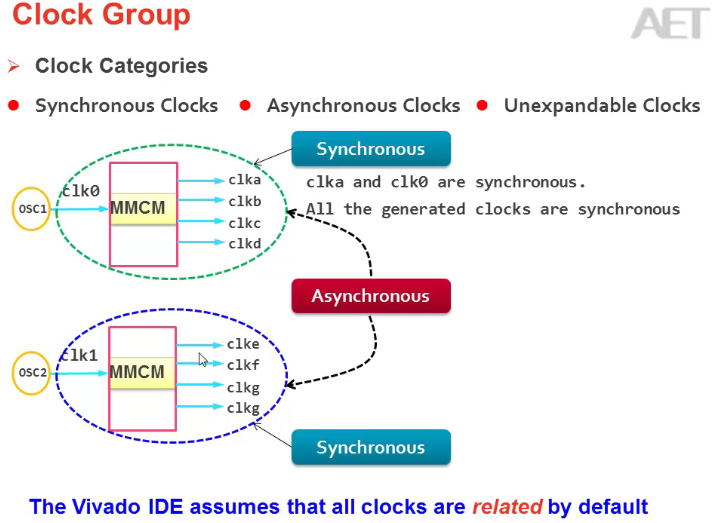

8. 时钟的分组

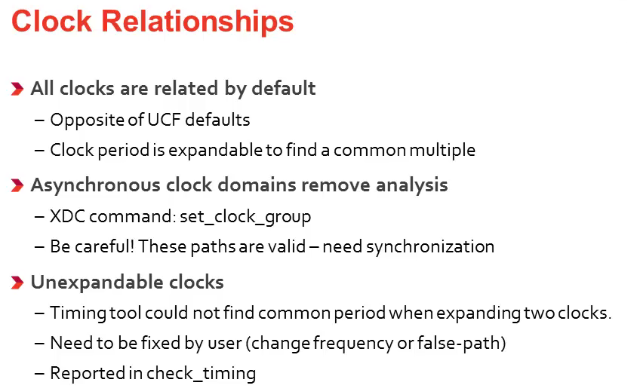

Vivado假设所有时钟是相关的

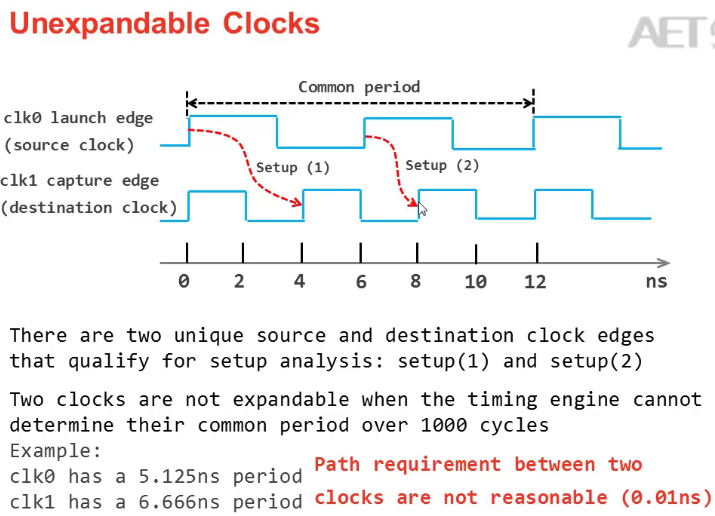

8.1 无法期望的时钟

发送时钟和捕获时钟,最小公倍数的关系,做设计的时候需要关注。跨时钟域的设计

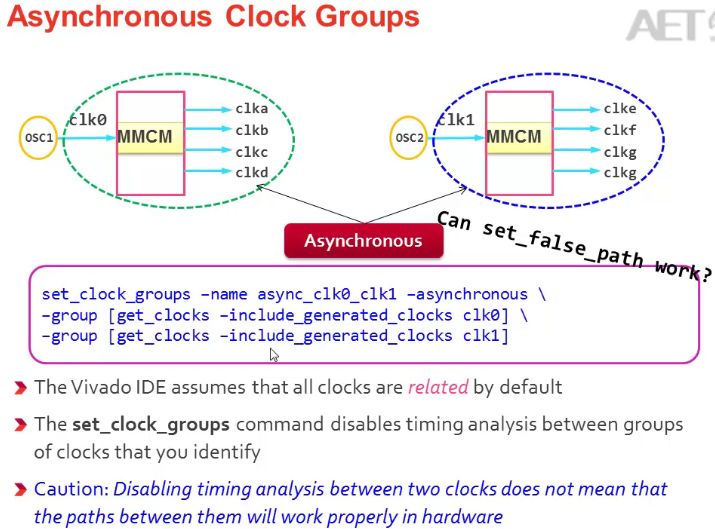

8.2 异步时钟组

可以通过set_false_path来让Vivado 不对其进行分析进行分析,记住是双向的

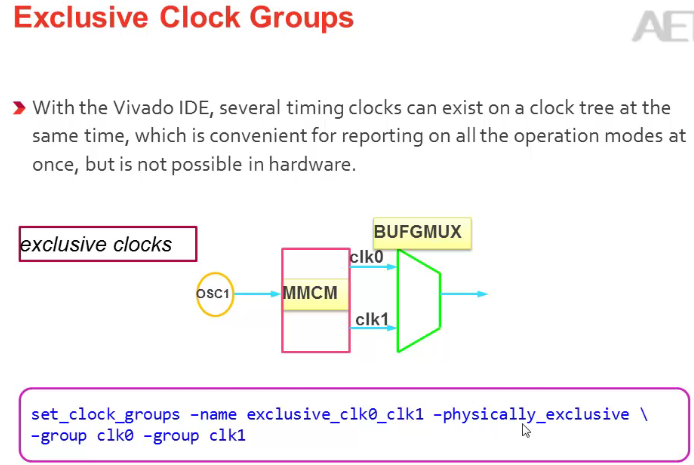

8.3 时钟组的选择

时钟的关系

浙公网安备 33010602011771号

浙公网安备 33010602011771号