第十课时:输入和输出引脚和时钟规划

IO和时钟是否符合规则

1. 管脚的基础知识

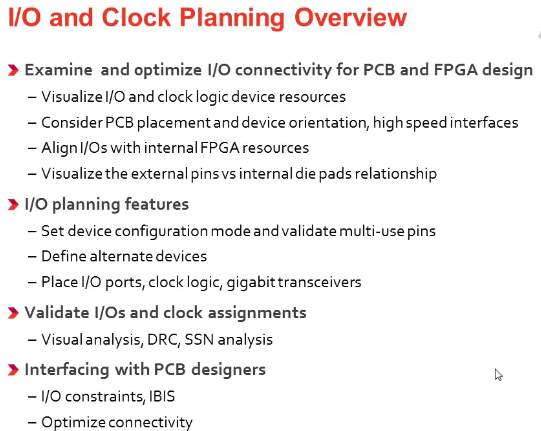

1. 1 I/O and Clock Planning Overview

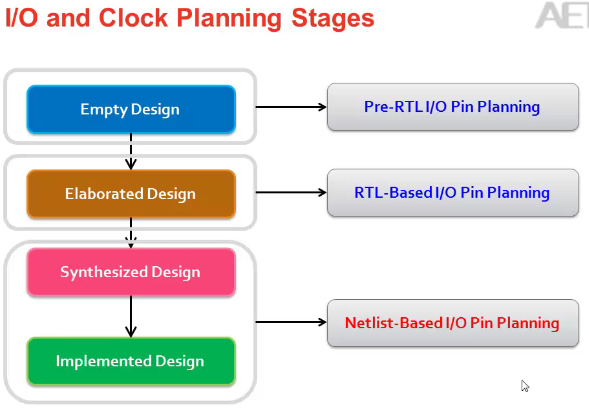

1.2 I/O and Clock Planning Stages

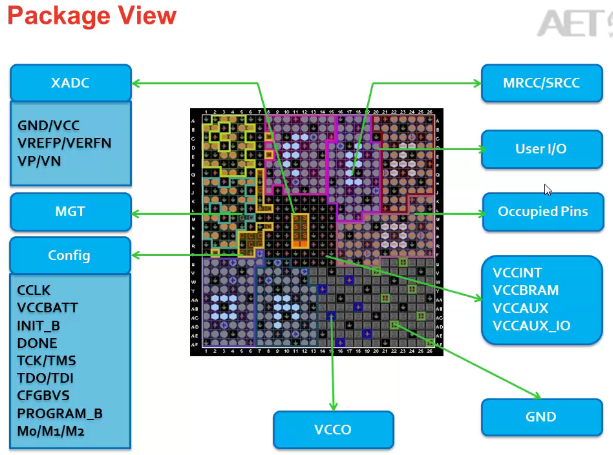

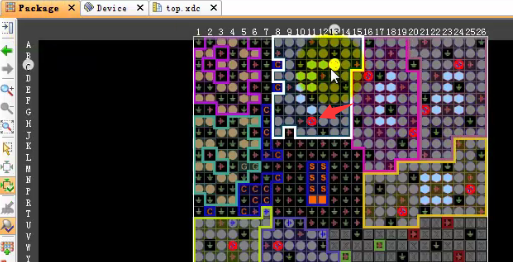

蓝色的六边形:时钟管脚

圆形:User IO

G:transiver有关

1.3 Package View

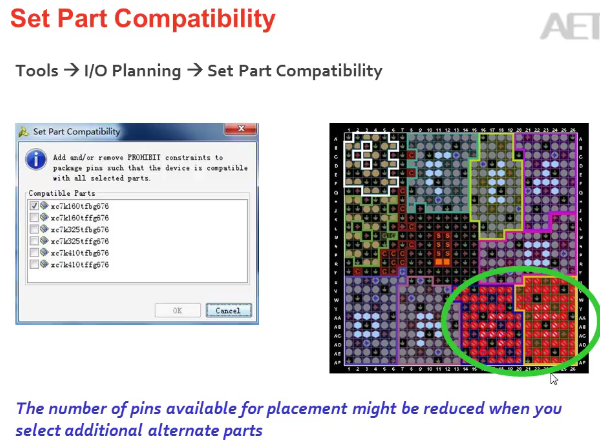

设计主板的兼容性

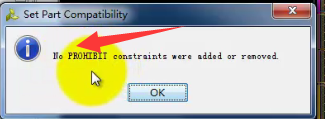

1.4 Set Part Compatibility

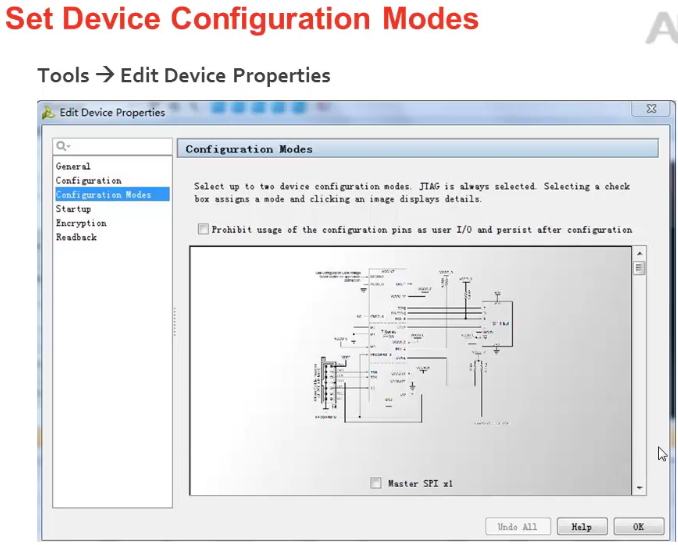

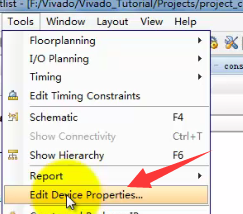

1.5 Set Device Configuration Modes

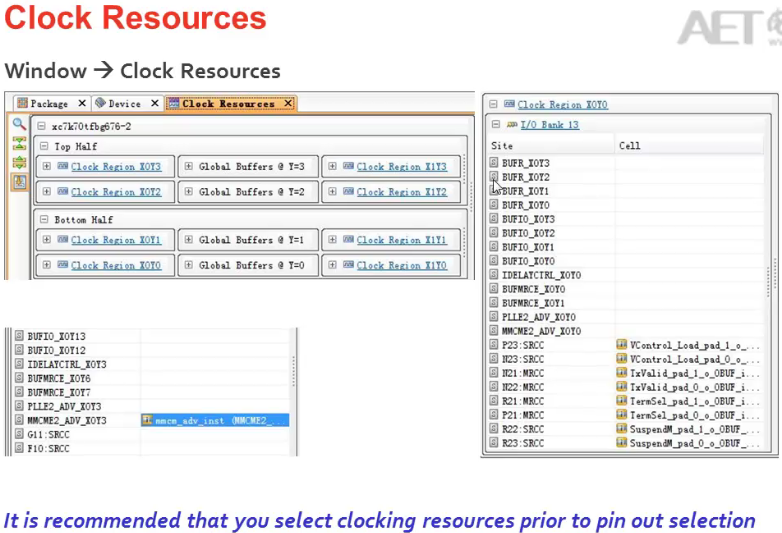

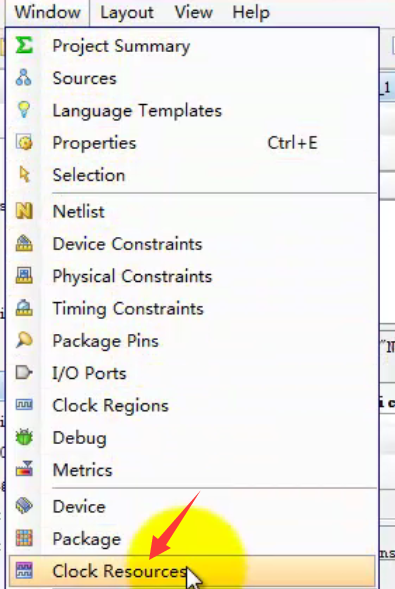

2. 时钟资源

根据时钟率显示时钟的资源

内部的时钟资源

管脚分配之前:确定时钟资源,引脚,位置等

3. 引脚分配

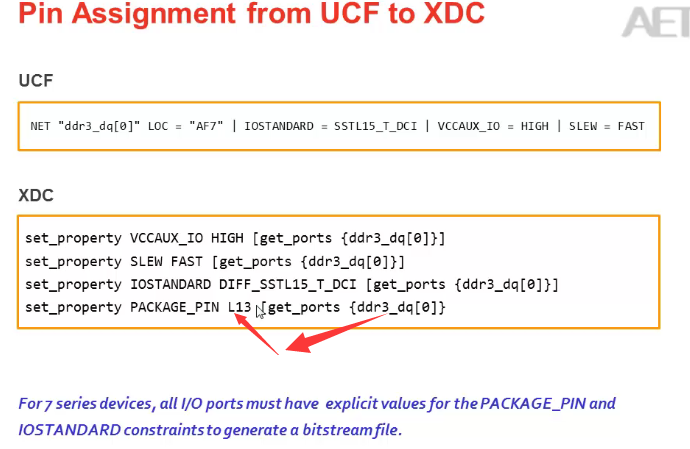

ISE中使用UCF进行约束

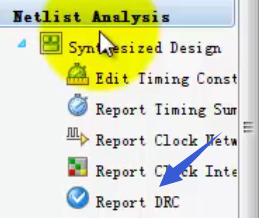

4 DEMO

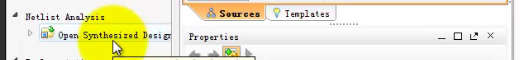

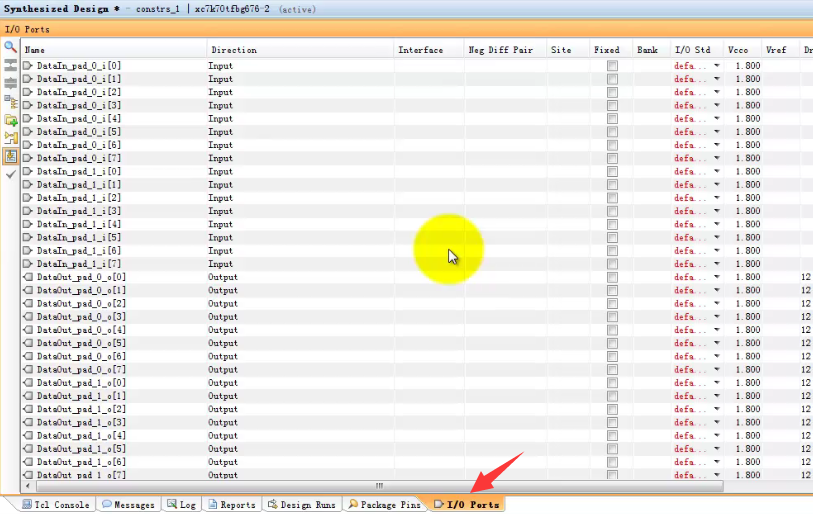

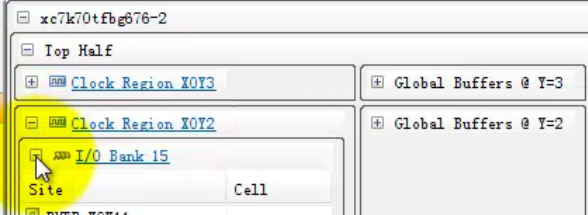

- 打开综合后的设计,网表文件

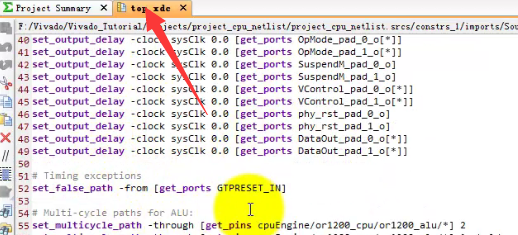

- 基本的约束,不包括管脚的约束

- 打开网表文件,vivado会自动切换到io planing

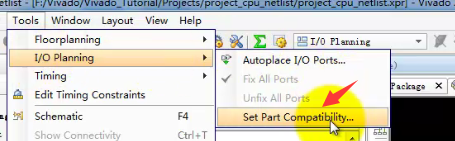

- 兼容性的设计

- configuration mode下可以看是如何配置的

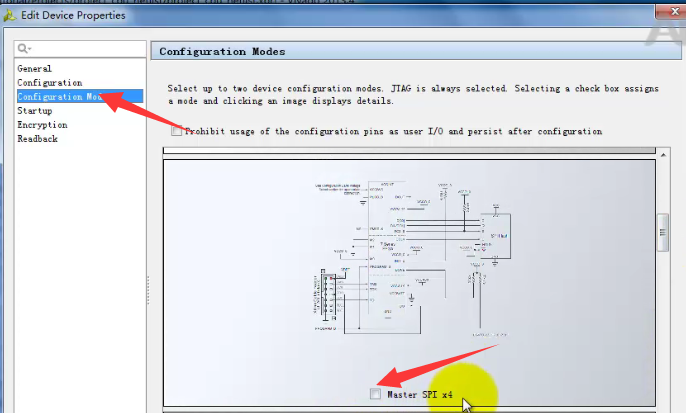

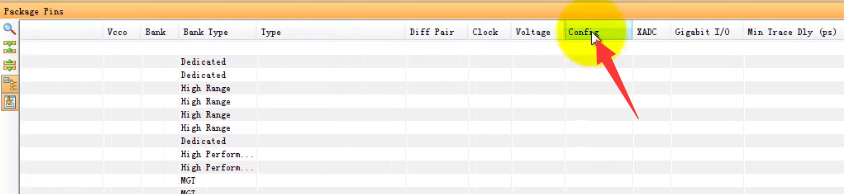

- package ping里面找和config相关的引脚

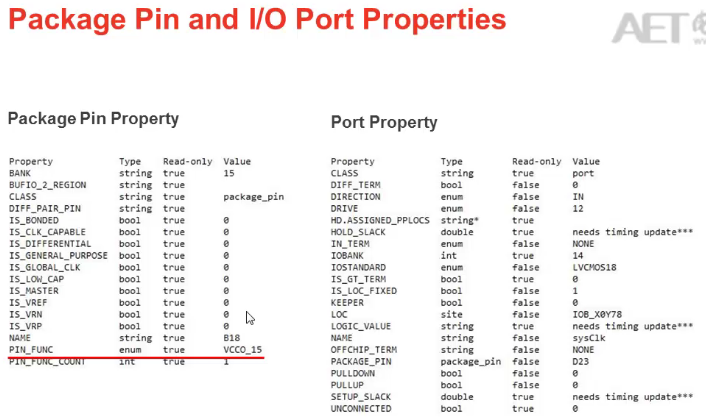

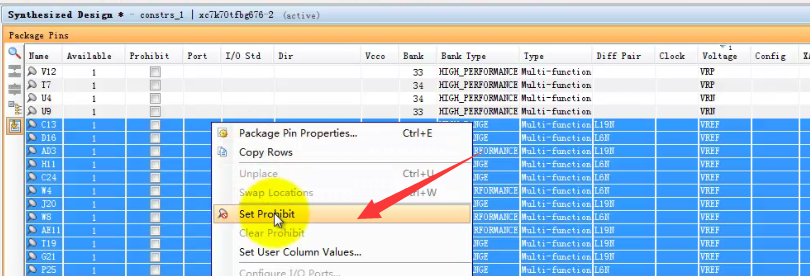

- 在config里面找相关的引脚的位置,VREF电压

- 红色管脚就不能使用了

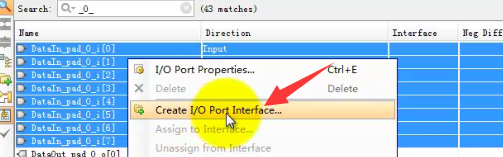

创建interface

Interface可以把相关的引脚分成一组,进行合理的放置

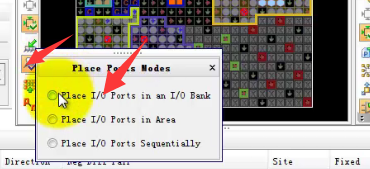

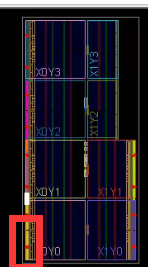

- 可以在device view看到大概的位置

- 选择一个区域放置

- 剩下 的一个放置

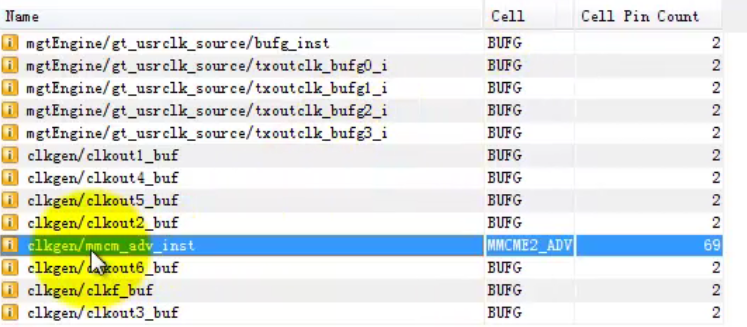

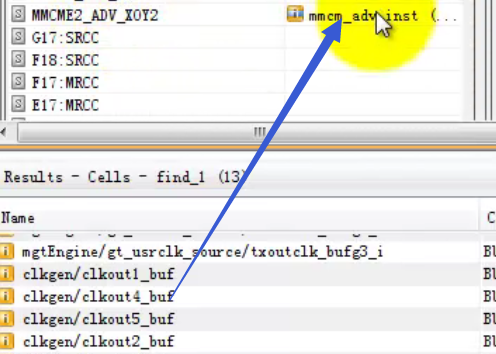

时钟资源

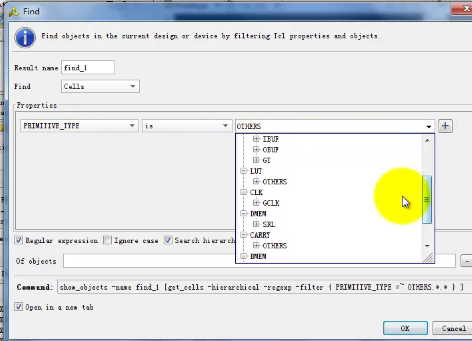

EDIT FIND

按F4以原理图的形式显示

拖拽过去进行时钟资源分配

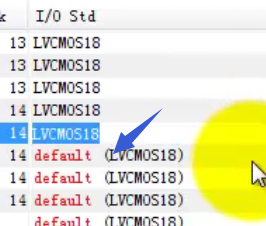

- 缺省情况下,以Default的形式,手工的设定

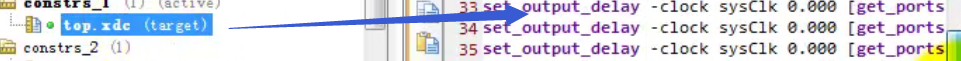

约束的保持

上面的设置信息将保存到,xdc文件中

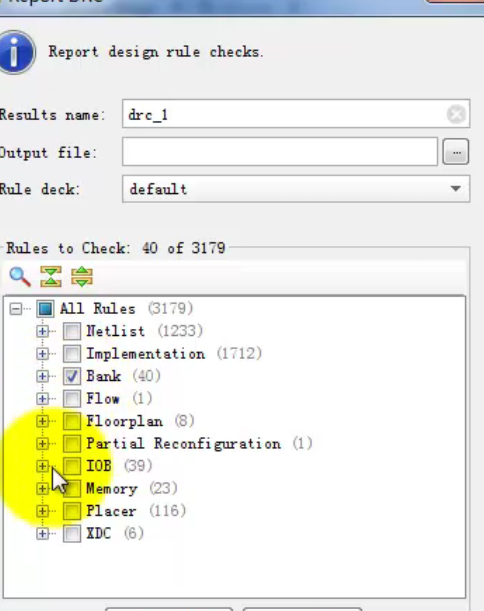

DRC检测

浙公网安备 33010602011771号

浙公网安备 33010602011771号