第九课时:编程与调试

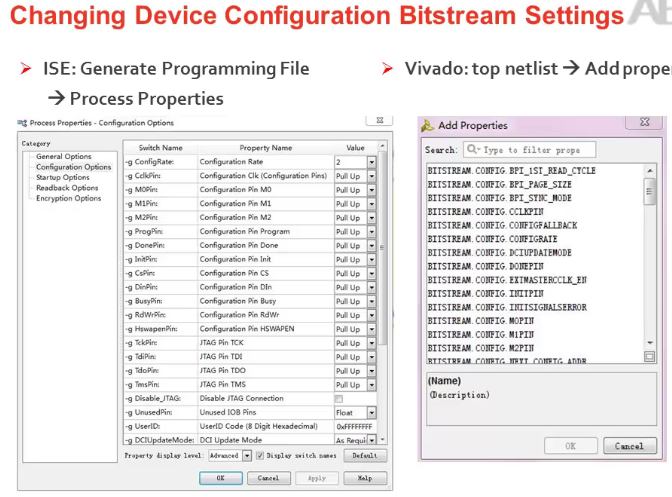

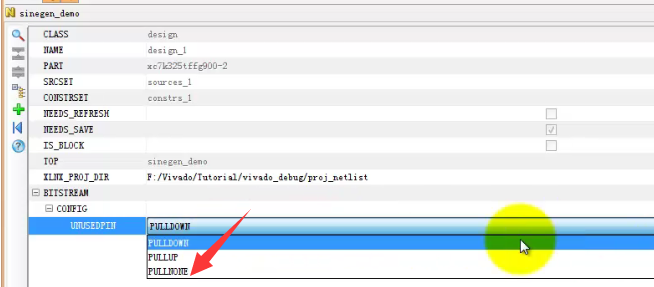

1. 比特文件的配置

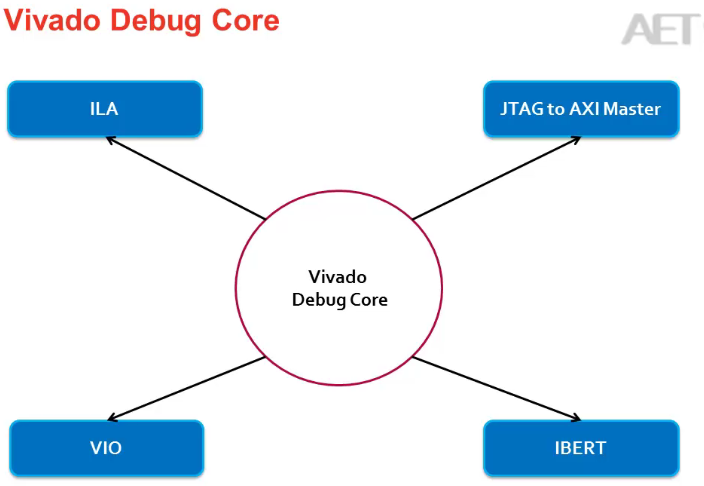

Debug Core

PPT1

PPT2

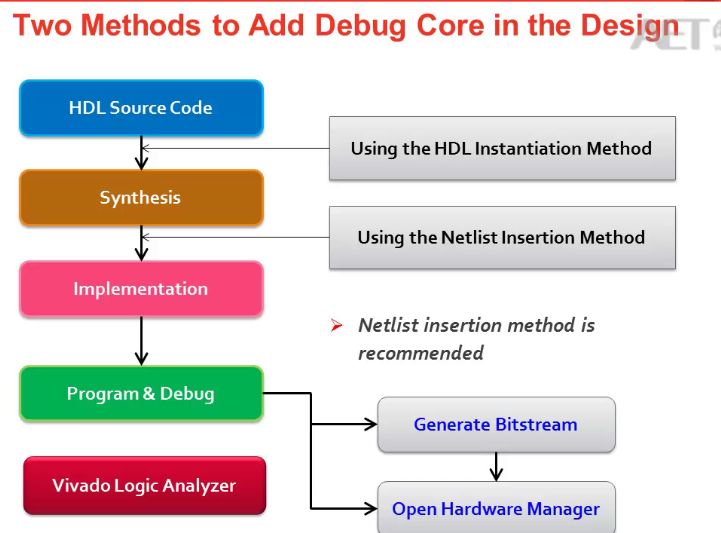

插入的时期

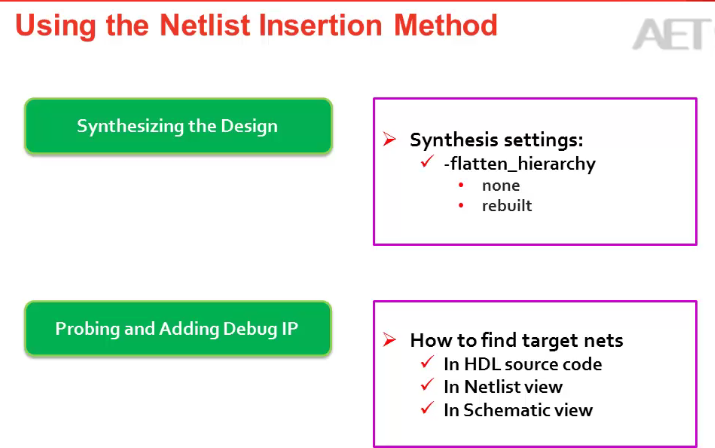

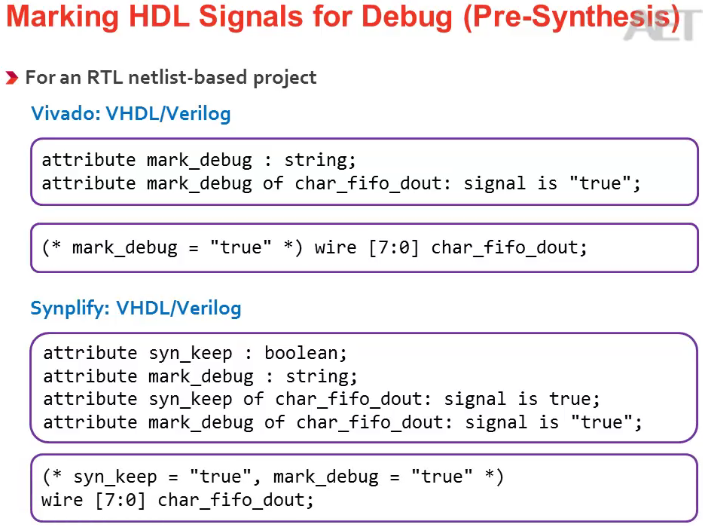

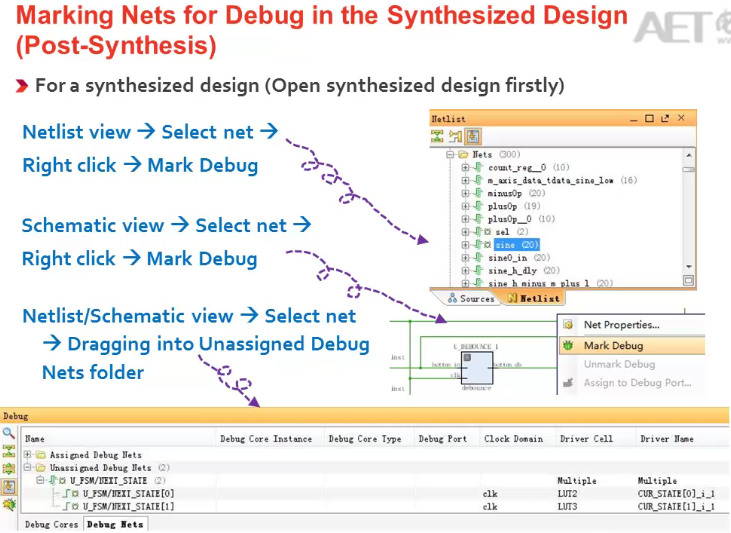

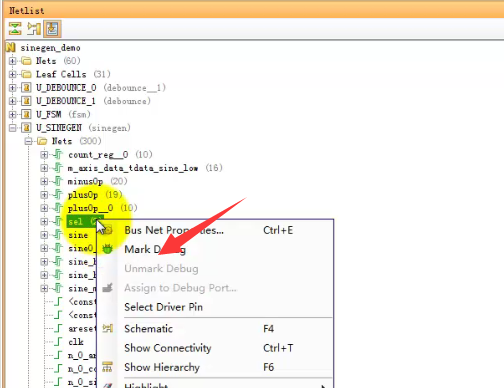

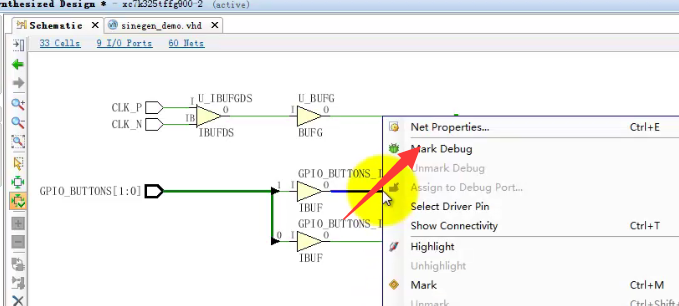

2. 在网表文件中插入

PPT1

PPT2

PPT3

PPT3

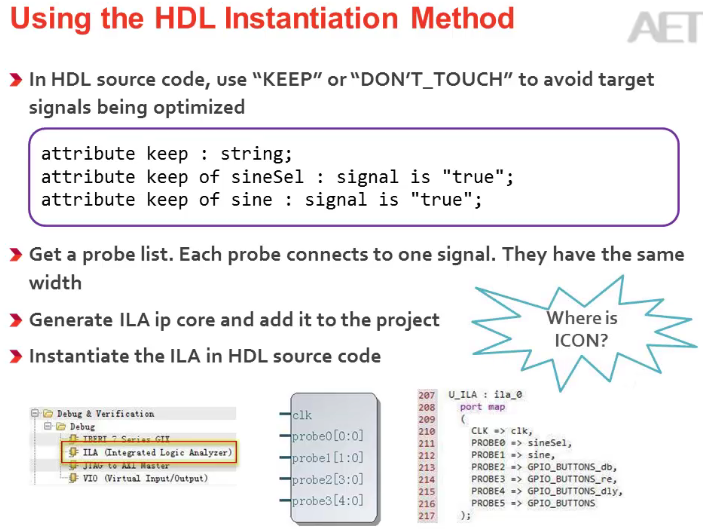

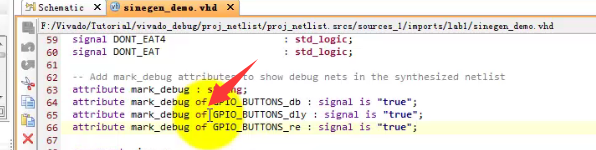

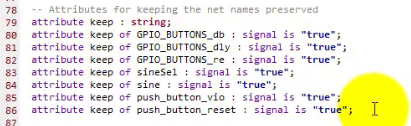

3. 通过HDL代码实例化

PPT1

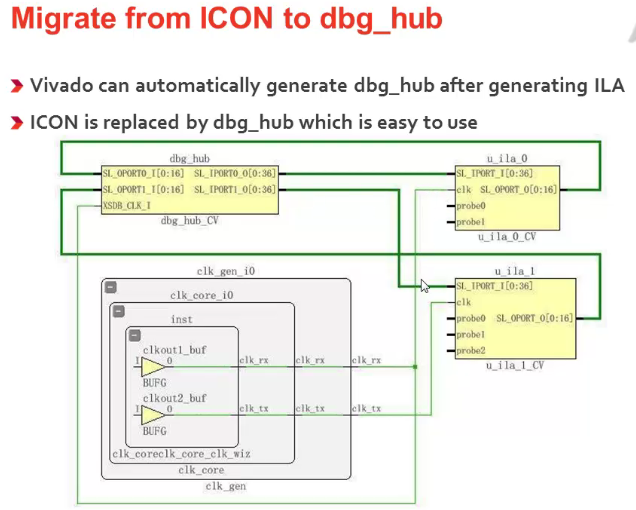

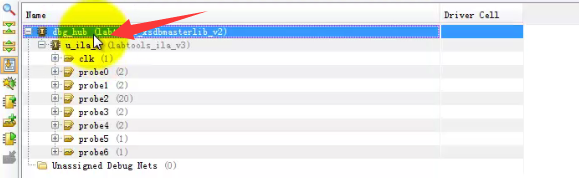

- debug_hub

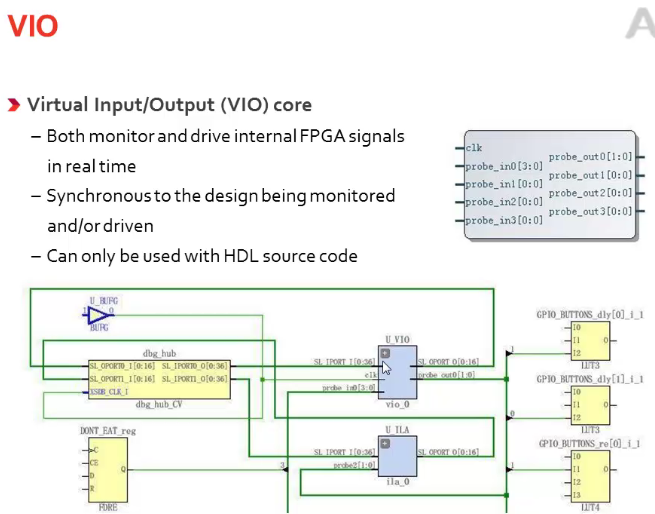

4. VIO

VIO检测内部信号的等效于示波器

输入端相当于产生驱动信号

只能通过HDL代码实例化

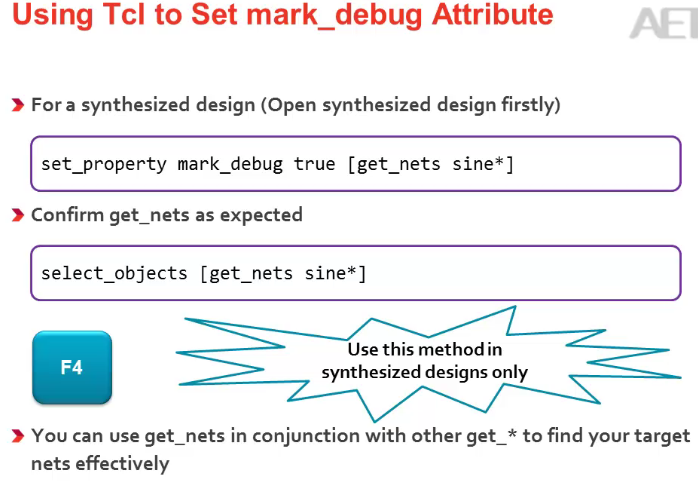

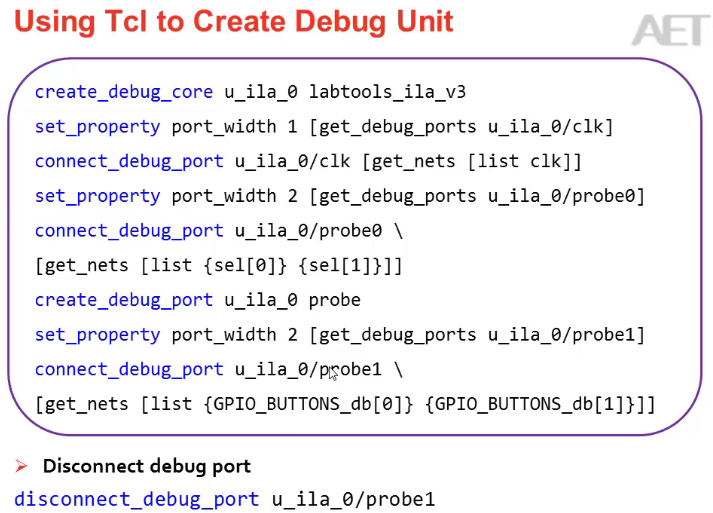

5. Tcl产生Debug core

缺省情况下产生两种信号

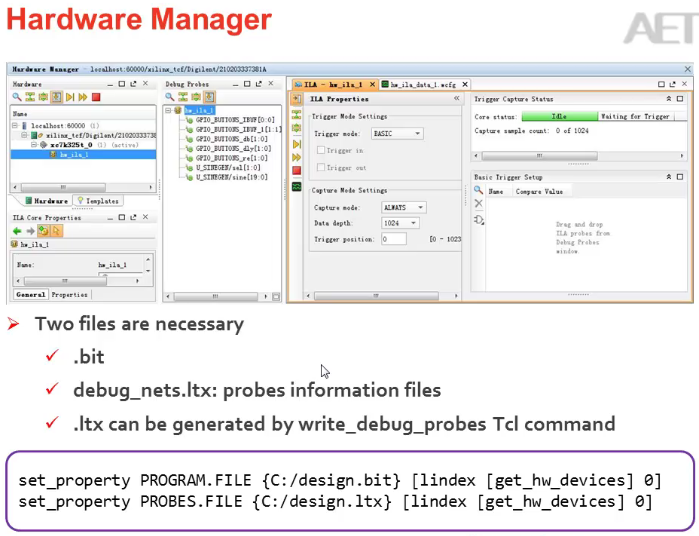

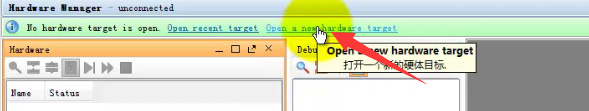

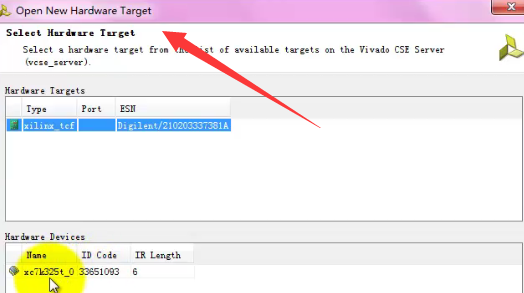

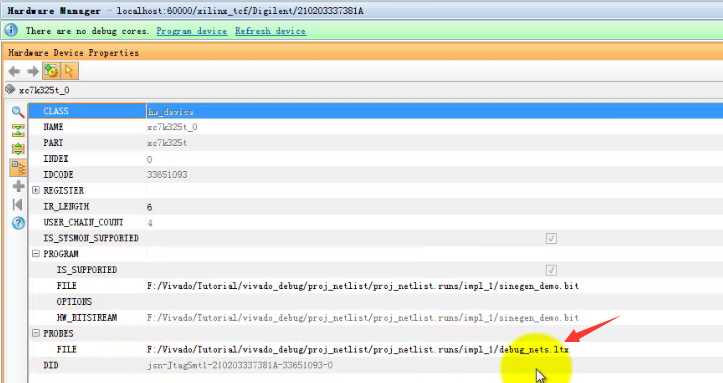

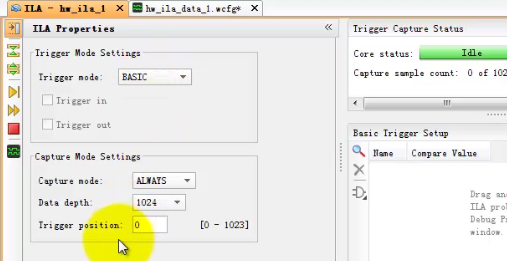

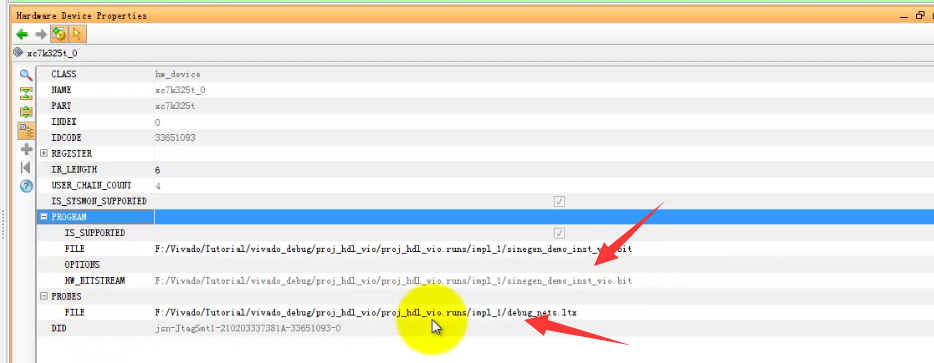

6. Hardware Manager

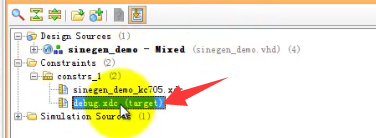

- bit

- ltx

通过这两个文件即可完成调试,在服务器上进行调试

7. Demo

- 综合之前,综合设置

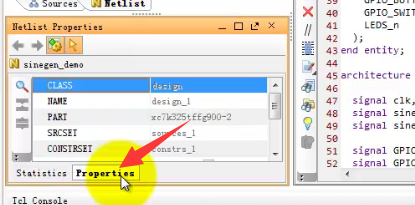

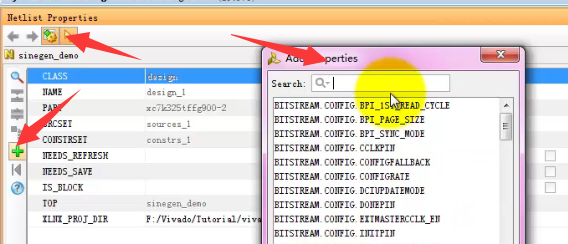

- 打开综合后的网表文件

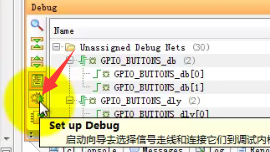

- 自动切换到debug

- 可以在netlist里面找

-

电路图

有时候重新指定时钟

保存之后生成的文件如下

实现

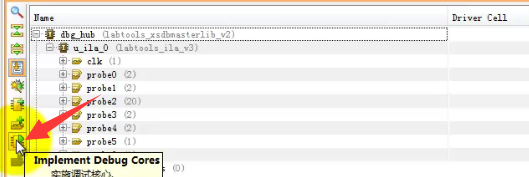

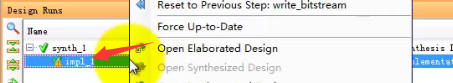

之后进行实现

- 打开实现

open_run imp1_1

确保timing收敛的情况下,后期的调试才有意义repot timing summary

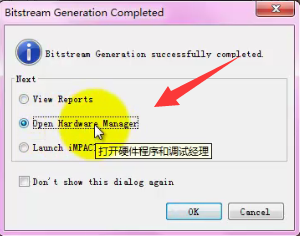

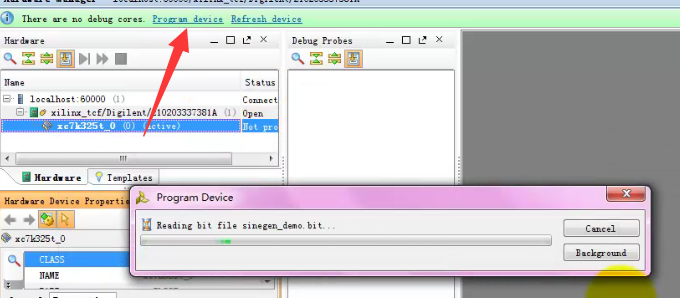

产生比特文件

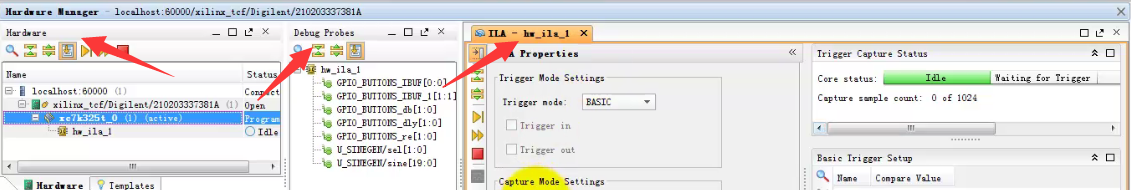

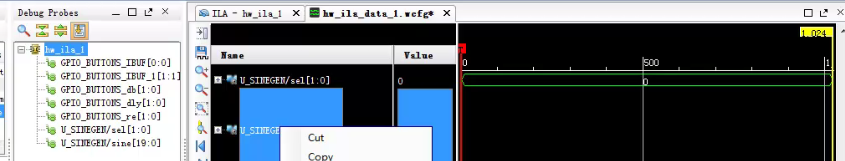

下板观察

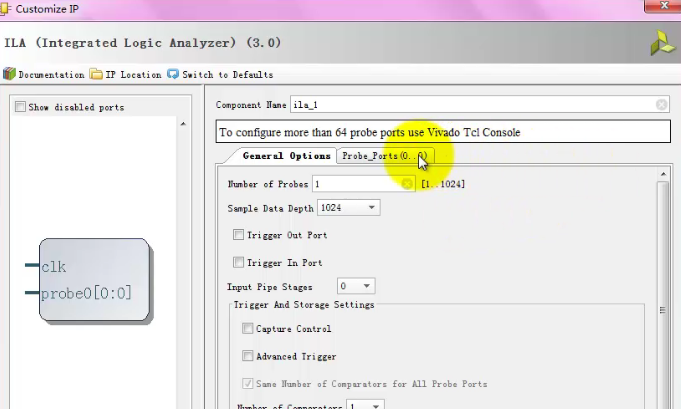

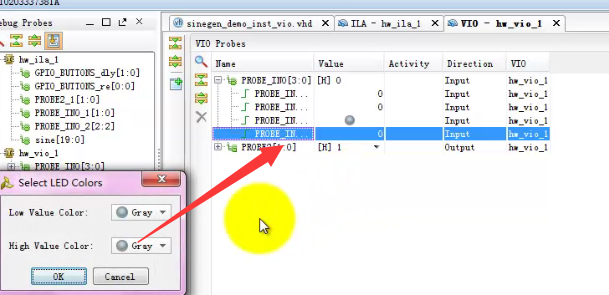

VIO

添加IP核

- 综合实现生产bit文件

浙公网安备 33010602011771号

浙公网安备 33010602011771号