第五课时:综合的基本设置和属性

1. 课程大纲

基本综合设置

PPT1

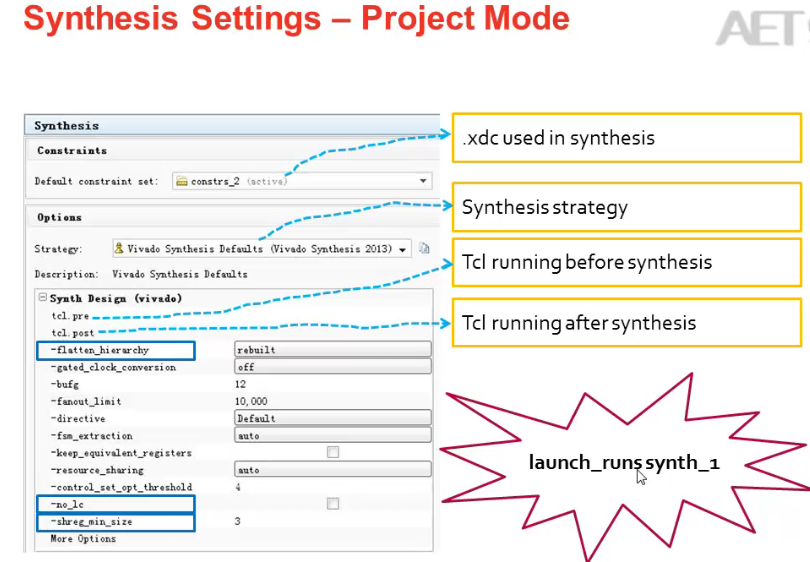

指定综合前执行的tcl命令和之后执行的tcl命令

project model输入命令开始综合

PPT2

2.综合的一些基本属性

2.1 移位寄存器的综合类型

- SRL_STYLE用于管理综合工具如何推断SRL(移位寄存器)。XilinxFPGA中,SLICEM中的LUT是可以配置为SRL的

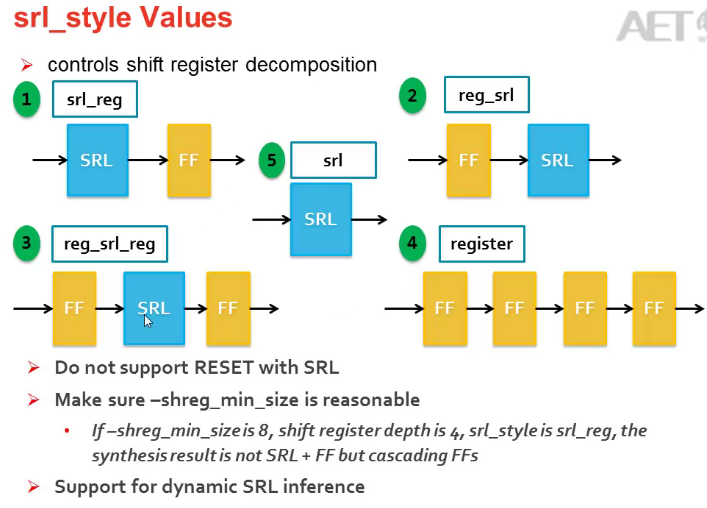

- SRL_STYLE有6个可选值,分别为register,srl,reg_srl,srl_reg,reg_srl_reg和block

###

###

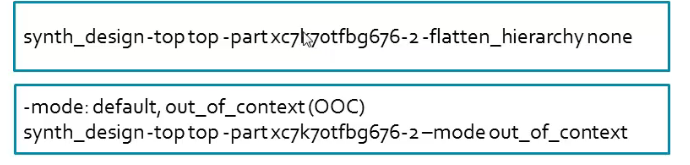

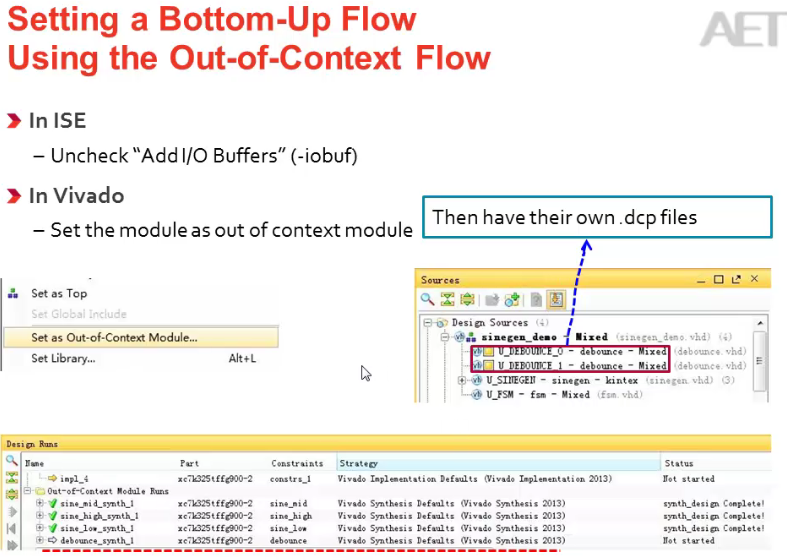

ISE中io不能插入Buffer

选择模块,点击右键,设置为OOC该模块变为黄色,生成有对应的dcp文件

2.2 自底向上的综合流程

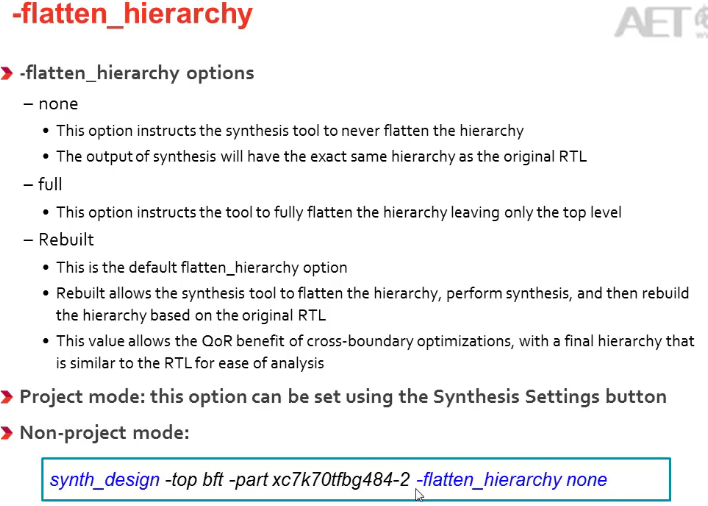

2.3 flatten_hierarchy

默认情况为rebuilt,意味着综合后的网表文件可能和原来的设计文件一样,也可能不一样

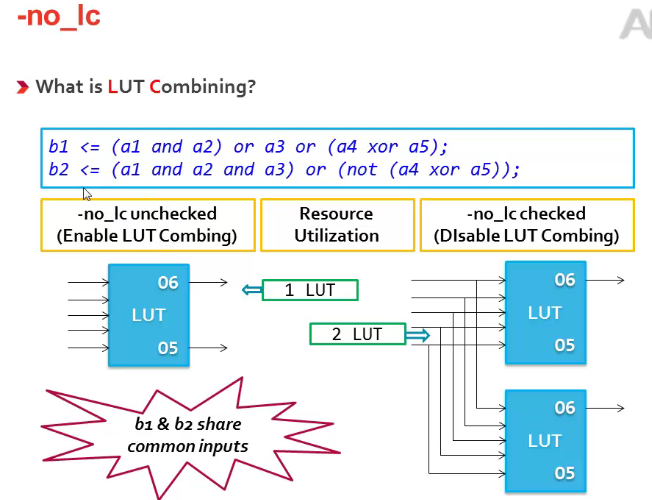

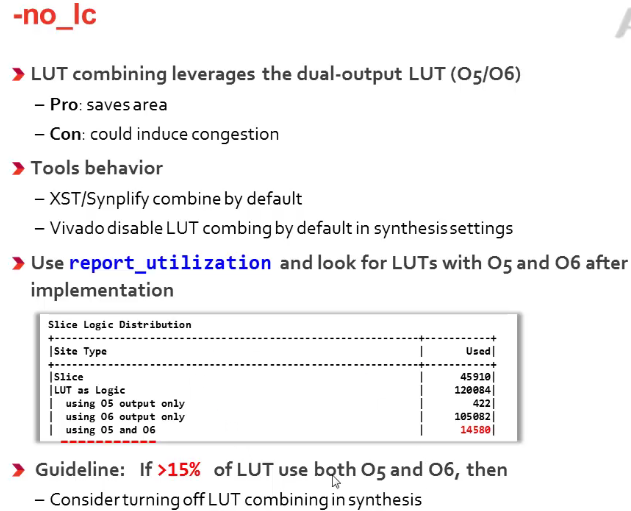

2.4 no_lc

-no_lc查找表绑定

LUT combing会减少查找表的数量

出现LUT combing:当b1 b2有同一个输入

优势在于:减少资源

缺点是:布线拥塞 Vivado下是默认不使能的,XST/Synplify默认打开

O5 O6占用大于15的时候要把no-lc关掉

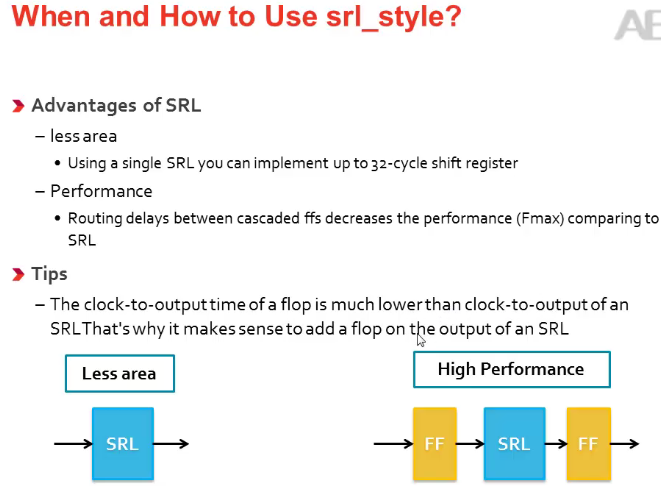

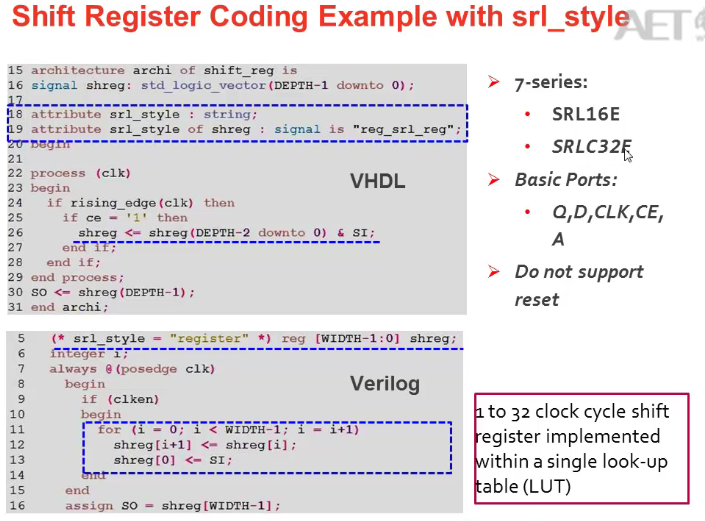

2.5 srl_style

7系列使用的是查找表实现查找表,注意的是没有复位端的

srl的取值不同综合的结果不同

第五种情况默认为一个查找表实现,注意不支持全局复位的

-shreg_min_size 大于8或者等于8,才能推断出

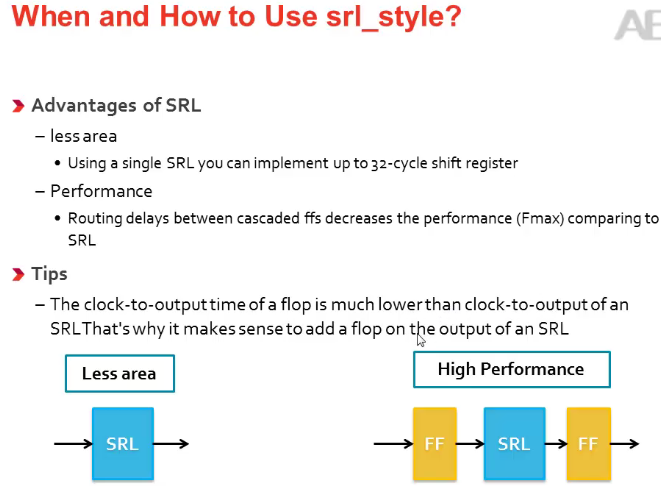

好处是:节省资源

32位移位寄存器值对应以一个6输入查找表

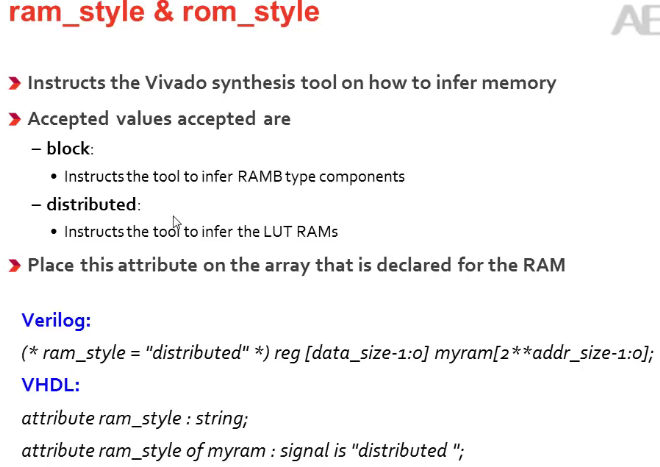

2.6 RAM_STYLE 和 ROM_STYLE

嵌入式资源还是分布式资源

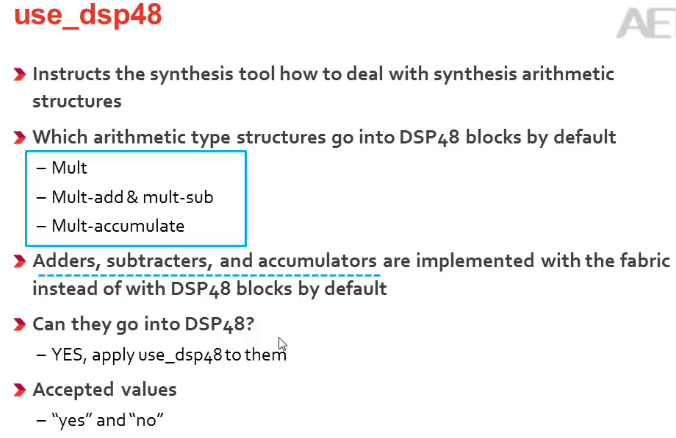

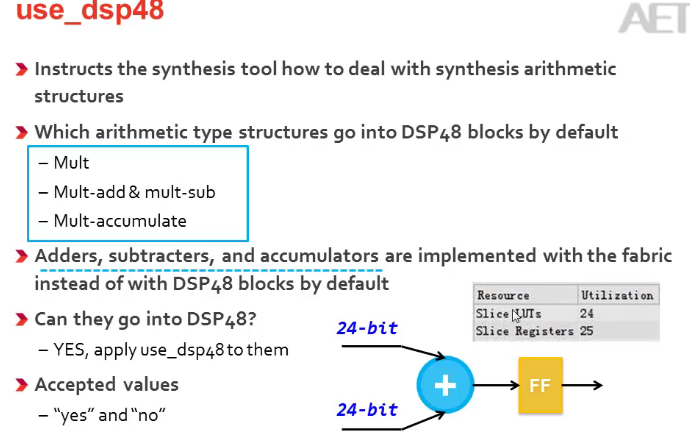

2.7 DSP 48的使用

缺省情况下:默认为DSP 48

加,减,累加都是fabric block

可以设置加减实现为dsp 48

如下所示:默认用的加法器占用的查找表比较多

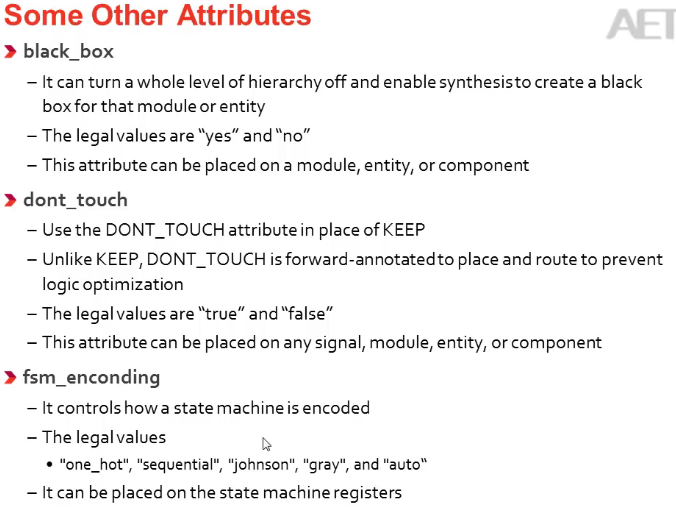

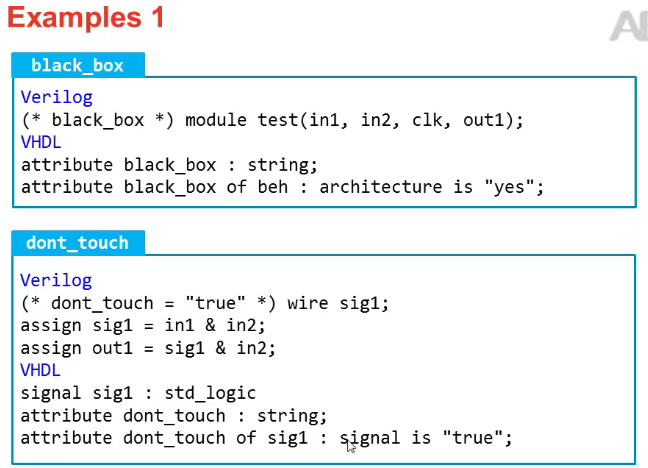

3 其他属性

-

黑盒子和dont toch

-

都是阻止,综合工具去优化,dont_toch对于布局布线都有用

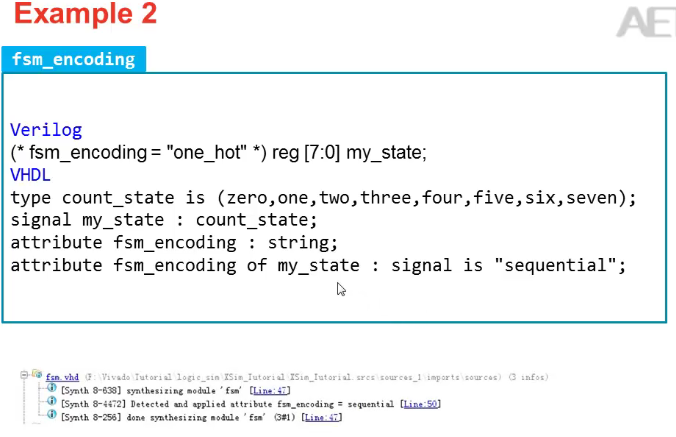

3.1 例子说明

找到状态机所在的VHD文件会告诉用的是哪种状态编码方式

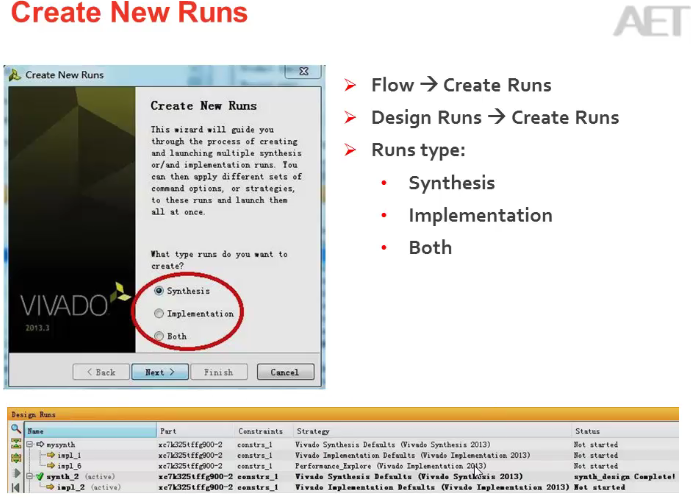

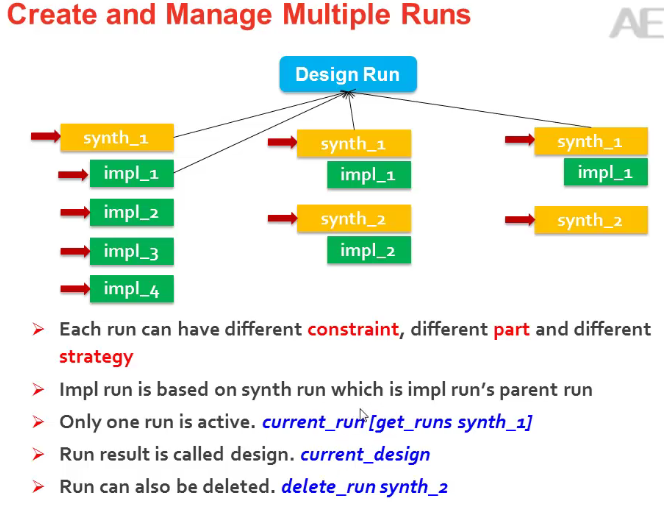

4 创建多个run

一个综合对应多个实现

一个综合对应一个实现

一个综合没有实现

每个run可以有不同的约束文件,不同的芯片,不同的综合策略

每个实现有parent run

激活run

查看当前的design current_design

删除run

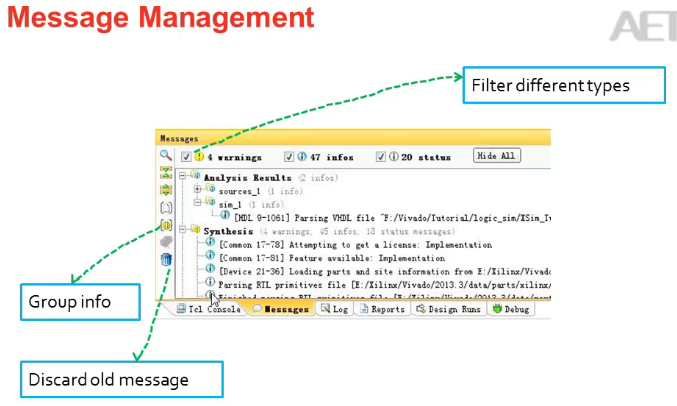

5 信息的管理

- 给信息分组

6 总结

支持自顶向上,也支持自底向上

浙公网安备 33010602011771号

浙公网安备 33010602011771号