AHB-SRAMC

- SRAM控制器的设计需求:

- 支持低功耗;(支持片选控制,使未选择的SRAM处于standby状态)

- 支持单周期读写;

- 能够根据AHB总线的读写宽度进行相应的SRAM位宽选择;

- 能够支持DFT/BIST测试。

- SRAM控制器的功能列表:

- 32位的AHB slave interface;

- 支持8位、16位和32位的SRAM数据读写操作;

- 支持SRAM的单周期读写;

- 支持低功耗工作(8位/16位操作):在多块SRAM组成的存储器中,根据不同地址,系统选择一块或者多块SRAM,未被选中的SRAM处在low-power standby模式;

- 支持DFT/BIST功能

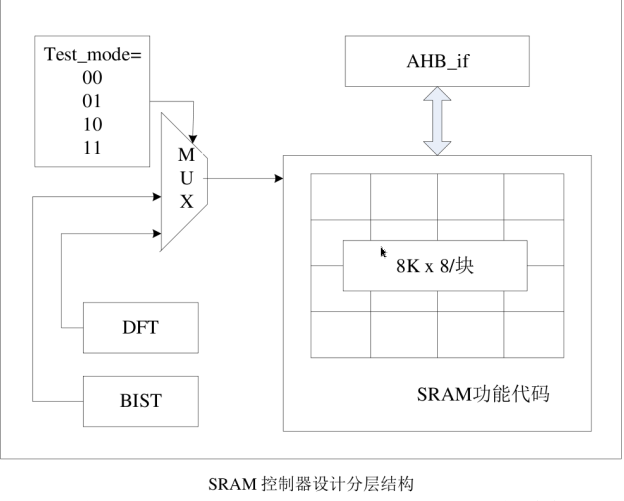

- 总的设计分层:

![]()

-

-

AHB-IF中包含SRAM的片选、读写宽度的选择,以实现低功耗和SRAM位宽的选择。

- MUX用来对测试模式进行选择。

-

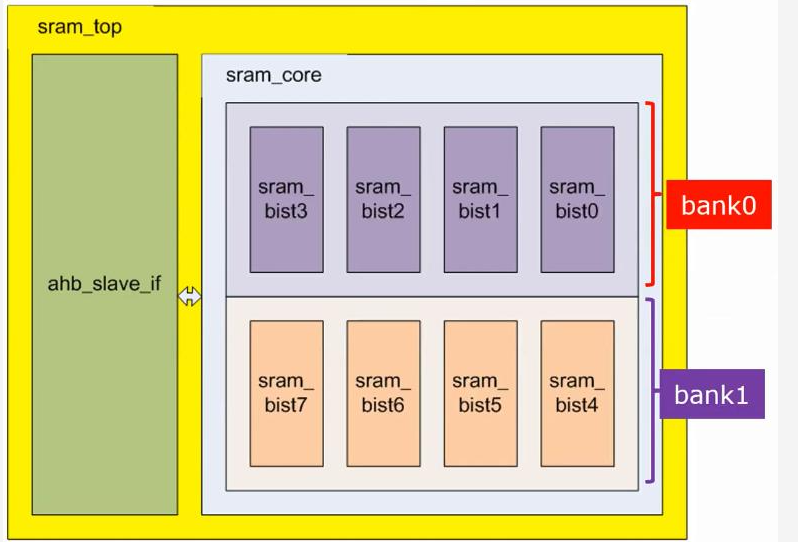

- SRAM控制器设计框图

![]()

-

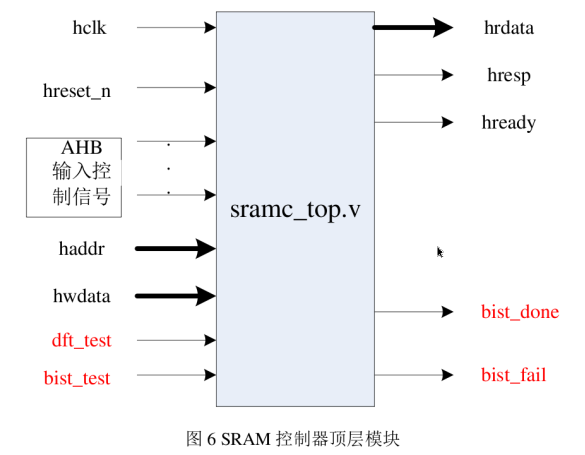

SRAM控制器的的最外层是sramc_top模块,他包含ahb_slave_if.v模块和sram_core.v两个模块,sram_core.v里面有sram_core和bist模块;

- ahb_slave_if.v:给sram控制器模块提供读写控制信号(sram_r_en、sram_w_ren)、数据信号以及片选地址(bank0_csn、bank_1csn)的;

- sram_core.v:该模块包含两个部分,一个是sram_core,用来存放数据,分为bank0和bank1,每个bank里面有4个带mbist的sram_bist;另一个是bist模块,将其与sram_core放在一起,实现sram_core的自测。

-

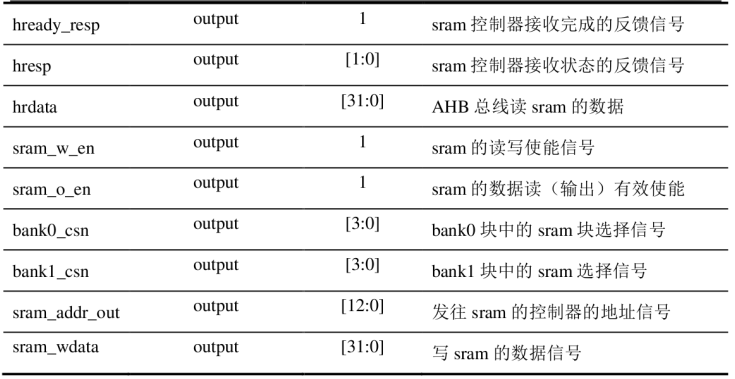

- 信号列表

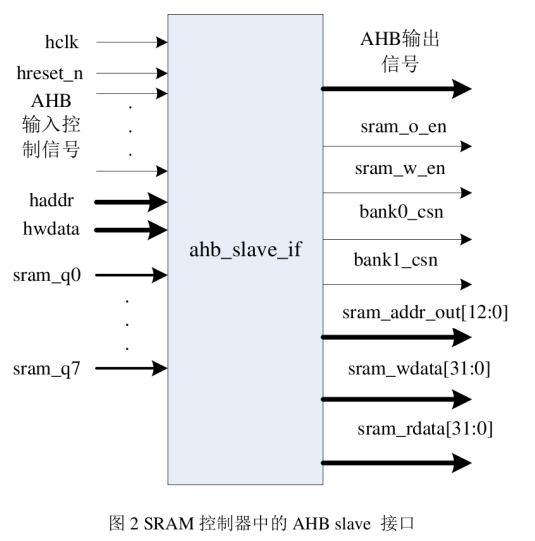

- AHB_slave_if.v信号:

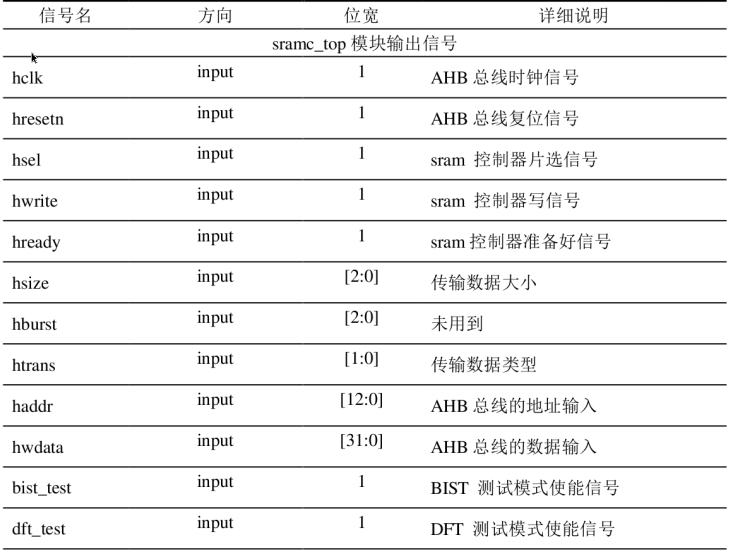

- 接口信号图

![]()

-

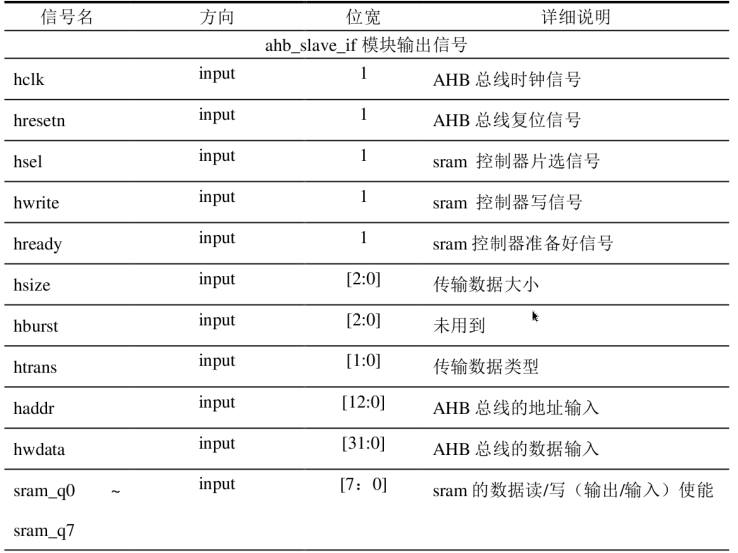

接口信号说明列表:

![]()

![]()

-

- 接口信号图

-

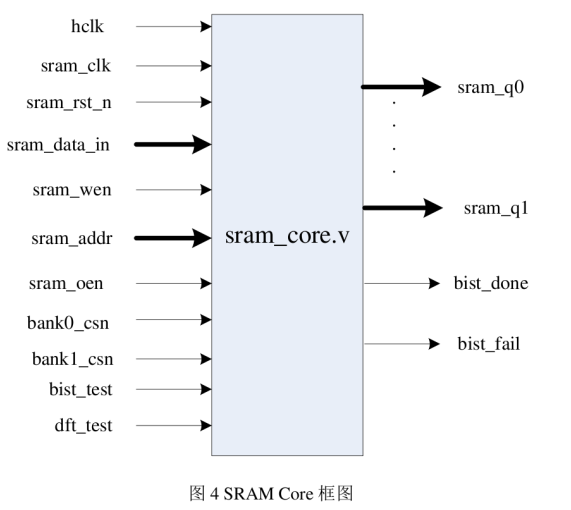

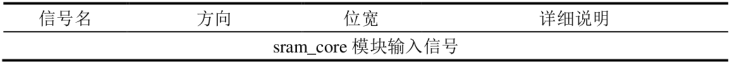

sram_core.v

- 接口信号图:4块SRAM实例化后的bank模块,每块sram核的选择由sram_csn[3:0]中的值和handr_reg[15]决定。

![]()

-

接口信号说明列表:

![]()

![]()

![]()

- 接口信号图:4块SRAM实例化后的bank模块,每块sram核的选择由sram_csn[3:0]中的值和handr_reg[15]决定。

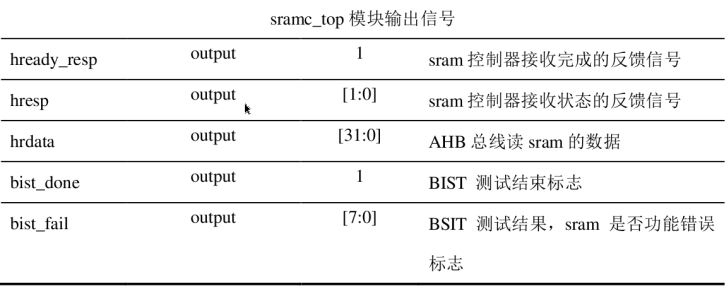

- 顶层信号:

- 接口信号图:

![]()

- 信号功能列表:

![]()

![]()

- 接口信号图:

- AHB_slave_if.v信号:

浙公网安备 33010602011771号

浙公网安备 33010602011771号