SV_17_Coverage

引言:

传统的验证质量是借助代码覆盖工具来度量的。代码覆盖率反映了HDL代码的执行程度。代码覆盖工具通常通过插件来跟踪代码执行。代码覆盖工具提供的特性集通常包括行/块覆盖、状态机覆盖、表达式覆盖、事件覆盖和翻转覆盖。

- 传统覆盖对于下面的方面有局限性:

- 验证non-implemented 特性(Overlooking non-implemented features.);

- 验证多个模块的交互性(The inability to measure the interaction between multiple modules.);

- 验证同时发生的时间和时间序列能力(The ability to measure simultaneous events or sequences of events);

- SV的功能覆盖的特性:

- 变量和表达式的覆盖,以及他们之间的交叉覆盖;

- 自动和用户自定的覆盖bins;

- 联合bins可以包含一组值、转换或交叉乘积;

- 多级过滤条件;

- 事件和序列自动触发覆盖抽样;

- 程序激活以及查询覆盖(Procedural activation and query of coverage.);

- 控制和规范覆盖范围。

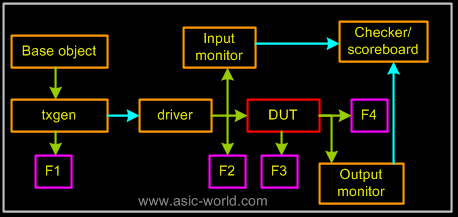

1。 Functional coverage types

- 通常当我们在测试计划文档 中记录测试用例时,我们也开始记录功能覆盖计划;

- 在验证环境中有四个地方可以对功能覆盖点进行编码;

- (F1)随机化(randomization)(是否能将随机对象发送到DUT);

- (F2)DUT输入接口的采样;

- (F3)DUT内部状态的采样(基本上这一块大部分都被SVA断言覆盖);

- (F4)DUT输出接口的采样

1 //+++++++++++++++++++++++++++++++++++++++++++++++++ 2 // DUT With Coverage 3 //+++++++++++++++++++++++++++++++++++++++++++++++++ 4 module simple_coverage(); 5 6 logic [7:0] addr; 7 logic [7:0] data; 8 logic par; 9 logic rw; 10 logic en; 11 //================================================= 12 // Coverage Group 13 //================================================= 14 covergroup memory @ (posedge en); 15 address : coverpoint addr { 16 bins low = {0,50}; 17 bins med = {51,150}; 18 bins high = {151,255}; 19 } 20 parity : coverpoint par { 21 bins even = {0}; 22 bins odd = {1}; 23 } 24 read_write : coverpoint rw { 25 bins read = {0}; 26 bins write = {1}; 27 } 28 endgroup 29 //================================================= 30 // Instance of covergroup memory 31 //================================================= 32 memory mem = new(); 33 //================================================= 34 // Task to drive values 35 //================================================= 36 task drive (input [7:0] a, input [7:0] d, input r); 37 #5 en <= 1; 38 addr <= a; 39 rw <= r; 40 data <= d; 41 par <= ^d; 42 $display ("@%2tns Address :%d data %x, rw %x, parity %x", 43 $time,a,d,r, ^d); 44 #5 en <= 0; 45 rw <= 0; 46 data <= 0; 47 par <= 0; 48 addr <= 0; 49 rw <= 0; 50 endtask 51 //================================================= 52 // Testvector generation 53 //================================================= 54 initial begin 55 en = 0; 56 repeat (10) begin 57 drive ($random,$random,$random); 58 end 59 #10 $finish; 60 end 61 62 endmodule 63 64 //compile result 65 @ 5ns Address : 36 data 81, rw 1, parity 0 66 @15ns Address : 99 data 0d, rw 1, parity 1 67 @25ns Address :101 data 12, rw 1, parity 0 68 @35ns Address : 13 data 76, rw 1, parity 1 69 @45ns Address :237 data 8c, rw 1, parity 1 70 @55ns Address :198 data c5, rw 0, parity 0 71 @65ns Address :229 data 77, rw 0, parity 0 72 @75ns Address :143 data f2, rw 0, parity 1 73 @85ns Address :232 data c5, rw 0, parity 0 74 @95ns Address :189 data 2d, rw 1, parity 0

2. Covergroup

- covergroup是一个用户定义的类型,定义一次;

- 可以在package、module、program、interface、class中定义该类型的多个实例;

- covergroup可以包含以下内容:

- 时钟事件:定义覆盖率采样的事件,如果被忽略,用户必须按程序触发覆盖率抽样,这是通过内置的sample方法完成的;

- 覆盖点:覆盖点可以是变量也可以是表达式;

- 交叉覆盖:覆盖组还可以指定两个或多个覆盖点或变量之间的交叉覆盖;

- 覆盖选项:用于控制covergroup的行为;

- 可选的形式参数:创建covergroup实例时传递的参数;

- covergroup可以指定一个或者多个选项来控制盒规范覆盖率数据的结构和收集方式;

- 覆盖率选项可以为整个覆盖率组指定也可以为覆盖率组中的特定项目指定;

- 一个covergroup可以包含一个或多个覆盖点,每个覆盖点包含一组与其抽样值或值转换相关联的bins;

1 //+++++++++++++++++++++++++++++++++++++++++++++++++ 2 // Define the interface with coverage 3 //+++++++++++++++++++++++++++++++++++++++++++++++++ 4 interface mem_if (input wire clk); 5 logic reset; 6 logic we; 7 logic ce; 8 logic [7:0] datai; 9 logic [7:0] datao; 10 logic [7:0] addr; 11 //================================================= 12 // Clocking block for testbench 13 //================================================= 14 clocking cb @ (posedge clk); 15 output reset, we, ce, datai,addr; 16 input datao; 17 endclocking 18 //================================================= 19 // Coverage Group in interface 20 //================================================= 21 covergroup memory @ (posedge ce); 22 address : coverpoint addr { 23 bins low = {0,50}; 24 bins med = {51,150}; 25 bins high = {151,255}; 26 } 27 data_in : coverpoint datai { 28 bins low = {0,50}; 29 bins med = {51,150}; 30 bins high = {151,255}; 31 } 32 data_out : coverpoint datao { 33 bins low = {0,50}; 34 bins med = {51,150}; 35 bins high = {151,255}; 36 } 37 read_write : coverpoint we { 38 bins read = {0}; 39 bins write = {1}; 40 } 41 endgroup 42 //================================================= 43 // Instance of covergroup 44 //================================================= 45 memory mem = new(); 46 47 endinterface 48 //+++++++++++++++++++++++++++++++++++++++++++++++++ 49 // DUT With interface 50 //+++++++++++++++++++++++++++++++++++++++++++++++++ 51 module simple_if (mem_if mif); 52 // Memory array 53 logic [7:0] mem [0:255]; 54 55 //================================================= 56 // Read logic 57 //================================================= 58 always @ (posedge mif.clk) 59 if (mif.reset) mif.datao <= 0; 60 else if (mif.ce && !mif.we) mif.datao <= mem[mif.addr]; 61 62 //================================================= 63 // Write Logic 64 //================================================= 65 always @ (posedge mif.clk) 66 if (mif.ce && mif.we) mem[mif.addr] <= mif.datai; 67 68 endmodule 69 70 //+++++++++++++++++++++++++++++++++++++++++++++++++ 71 // Testbench 72 //+++++++++++++++++++++++++++++++++++++++++++++++++ 73 module coverage_covergroup(); 74 75 logic clk = 0; 76 always #10 clk++; 77 //================================================= 78 // Instianciate Interface and DUT 79 //================================================= 80 mem_if miff(clk); 81 simple_if U_dut(miff); 82 //================================================= 83 // Default clocking 84 //================================================= 85 default clocking dclk @ (posedge clk); 86 87 endclocking 88 //================================================= 89 // Test Vector generation 90 //================================================= 91 initial begin 92 miff.reset <= 1; 93 miff.ce <= 1'b0; 94 miff.we <= 1'b0; 95 miff.addr <= 0; 96 miff.datai <= 0; 97 ##1 miff.reset <= 0; 98 for (int i = 0; i < 3; i ++ ) begin 99 ##1 miff.ce <= 1'b1; 100 miff.we <= 1'b1; 101 miff.addr <= i; 102 miff.datai <= $random; 103 ##3 miff.ce <= 1'b0; 104 $display ("@%0dns Write access address %x, data %x", 105 $time,miff.addr,miff.datai); 106 end 107 for (int i = 0; i < 3; i ++ ) begin 108 ##1 miff.ce <= 1'b1; 109 miff.we <= 1'b0; 110 miff.addr <= i; 111 ##3 miff.ce <= 1'b0; 112 $display ("@%0dns Read access address %x, data %x", 113 $time,miff.addr,miff.datao); 114 end 115 #10 $finish; 116 end 117 118 endmodule 119 120 //coverage report 121 122 Variables for Group coverage_covergroup.miff::memory 123 124 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 125 address 3 2 1 33.33 100 1 126 data_in 3 3 0 0.00 100 1 127 data_out 3 2 1 33.33 100 1 128 read_write 2 0 2 100.00 100 1

3. Covergroup inside a class

module 中的covergroup 与类中的covergroup的区别在于:

- class中的covergroup的实例时可选的,因为这是自动的,即covergroup是隐式的;

- 嵌入式的covergroup可以为protected和loca类属性定义覆盖模型,而无需对类数据封装进行任何更改;

- 类成员可以成为覆盖点,或者在 其他覆盖构造中使用,例如:条件保护或选项初始化;

- 一个类可以有多个covergroup

1 //+++++++++++++++++++++++++++++++++++++++++++++++++ 2 // Define the interface with coverage 3 //+++++++++++++++++++++++++++++++++++++++++++++++++ 4 interface mem_if (input wire clk); 5 logic reset; 6 logic we; 7 logic ce; 8 logic [7:0] datai; 9 logic [7:0] datao; 10 logic [7:0] addr; 11 //================================================= 12 // Clocking block for testbench 13 //================================================= 14 clocking cb @ (posedge clk); 15 inout reset, we, ce, datai,addr; 16 input datao; 17 endclocking 18 //================================================= 19 // Modport for testbench 20 //================================================= 21 modport tb (clocking cb, input clk); 22 23 endinterface 24 //+++++++++++++++++++++++++++++++++++++++++++++++++ 25 // DUT With interface 26 //+++++++++++++++++++++++++++++++++++++++++++++++++ 27 module simple_if (mem_if mif); 28 // Memory array 29 logic [7:0] mem [0:255]; 30 31 //================================================= 32 // Read logic 33 //================================================= 34 always @ (posedge mif.clk) 35 if (mif.reset) mif.datao <= 0; 36 else if (mif.ce && !mif.we) mif.datao <= mem[mif.addr]; 37 38 //================================================= 39 // Write Logic 40 //================================================= 41 always @ (posedge mif.clk) 42 if (mif.ce && mif.we) mem[mif.addr] <= mif.datai; 43 44 endmodule 45 46 //+++++++++++++++++++++++++++++++++++++++++++++++++ 47 // Testbench 48 //+++++++++++++++++++++++++++++++++++++++++++++++++ 49 module coverage_class(); 50 51 logic clk = 0; 52 always #10 clk++; 53 //================================================= 54 // Instianciate Interface and DUT 55 //================================================= 56 mem_if miff(clk); 57 simple_if U_dut(miff); 58 //================================================= 59 // Default clocking 60 //================================================= 61 default clocking dclk @ (posedge clk); 62 63 endclocking 64 65 //================================================= 66 // Test Vector generation 67 //================================================= 68 class mem_driver; 69 virtual mem_if.tb cif; 70 71 //================================================= 72 // Coverage Group in class 73 //================================================= 74 covergroup memory @ (negedge cif.cb.ce); 75 address : coverpoint cif.cb.addr { 76 bins low = {0,50}; 77 bins med = {51,150}; 78 bins high = {151,255}; 79 } 80 endgroup 81 82 covergroup datac @ (negedge cif.cb.ce); 83 data_in : coverpoint cif.cb.datai { 84 bins low = {0,50}; 85 bins med = {51,150}; 86 bins high = {151,255}; 87 } 88 data_out : coverpoint cif.cb.datao { 89 bins low = {0,50}; 90 bins med = {51,150}; 91 bins high = {151,255}; 92 } 93 read_write : coverpoint cif.cb.we { 94 bins read = {0}; 95 bins write = {1}; 96 } 97 endgroup 98 99 function new (virtual mem_if.tb cif); 100 this.cif = cif; 101 this.datac = new(); 102 this.memory = new(); 103 endfunction 104 105 task automatic drive (); 106 cif.cb.reset <= 1; 107 cif.cb.ce <= 1'b0; 108 cif.cb.we <= 1'b0; 109 cif.cb.addr <= 0; 110 cif.cb.datai <= 0; 111 @ (cif.cb) cif.cb.reset <= 0; 112 for (int i = 0; i < 3; i ++ ) begin 113 ##1 cif.cb.ce <= 1'b1; 114 cif.cb.we <= 1'b1; 115 cif.cb.addr <= i; 116 cif.cb.datai <= $random; 117 repeat (3) @ (cif.cb) cif.cb.ce <= 1'b0; 118 $display ("@%0dns Write access address %0x, data %x", 119 $time,i,cif.cb.datai); 120 end 121 for (int i = 0; i < 3; i ++ ) begin 122 @ (cif.cb) cif.cb.ce <= 1'b1; 123 cif.cb.we <= 1'b0; 124 cif.cb.addr <= i; 125 repeat (4) @ (cif.cb) cif.cb.ce <= 1'b0; 126 $display ("@%0dns Read access address %0x, data %x", 127 $time,i,cif.cb.datao); 128 end 129 endtask 130 131 endclass 132 133 mem_driver driver = new(miff); 134 135 initial begin 136 driver.drive(); 137 #10 $finish; 138 end 139 140 endmodule 141 142 //simulation 143 @90ns Write access address 0, data 24 144 @170ns Write access address 1, data 81 145 @250ns Write access address 2, data 09 146 @350ns Read access address 0, data 24 147 @450ns Read access address 1, data 81 148 @550ns Read access address 2, data 09 149 150 //cover report 151 152 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 153 address 3 2 1 33.33 100 1 154 155 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 156 data_in 3 2 1 33.33 100 1 157 data_out 3 3 0 0.00 100 1 158 read_write 2 0 2 100.00 100 1

4. Coverage points

- 一个covergroup可以包含 多个coverpoint,

- 每个coverpoint可以是一个变量或者表达式;每个coverpoint包含一组与其相关的bins;

- 每个bins可以由用户显式定义,也可以由系统自动创建;

- coverpoint创建了一个分层的域,可以被选择性的被签标记,如果标签被指定,那么相应的覆盖点也就被指定;利用这个标签可以访问覆盖点或者将对应的覆盖点包含 到另一个覆盖点中实现交叉覆盖;

- 如果省略标签,而且 coverpoint与单个变量相关联,则变量名就成为coverpoint的名称,否则的话只能任由系统在生成覆盖率报告的时候自定义名字,该名字也无法在语言中使用。

- coverpoint可以用 iff 禁用覆盖集合;

- 自动创建的bins可以用auto_bin_max选项来控制;

- 用bins[*]为创建一定数量的bins,open_range_list指定与bins相关联的值集;

- bins在指定容量的bins中是平均分布的;

- bin定义的末尾可以 加入iff(条件表达式),如果表达式在采样点 是 false,则容器的计数不会增加;

1 //+++++++++++++++++++++++++++++++++++++++++++++++++ 2 // Define the interface with coverage 3 //+++++++++++++++++++++++++++++++++++++++++++++++++ 4 interface mem_if (input wire clk); 5 logic reset; 6 logic we; 7 logic ce; 8 logic [7:0] datai; 9 logic [7:0] datao; 10 logic [7:0] addr; 11 //================================================= 12 // Clocking block for testbench 13 //================================================= 14 clocking cb @ (posedge clk); 15 output reset, we, ce, datai,addr; 16 input datao; 17 endclocking 18 //================================================= 19 // Coverage Group in interface 20 //================================================= 21 covergroup memory @ (posedge ce); 22 address : coverpoint addr { 23 bins low = {0,50}; 24 bins med = {51,150}; 25 bins high = {151,255}; 26 } 27 data_in : coverpoint datai { 28 bins low = {0,50}; 29 bins med = {51,150}; 30 bins high = {151,255}; 31 } 32 data_out : coverpoint datao { 33 bins low = {0,50}; 34 bins med = {51,150}; 35 bins high = {151,255}; 36 } 37 read_write : coverpoint we { 38 bins read = {0}; 39 bins write = {1}; 40 } 41 endgroup 42 //================================================= 43 // Instance of covergroup 44 //================================================= 45 memory mem = new(); 46 47 endinterface 48 //+++++++++++++++++++++++++++++++++++++++++++++++++ 49 // DUT With interface 50 //+++++++++++++++++++++++++++++++++++++++++++++++++ 51 module simple_if (mem_if mif); 52 // Memory array 53 logic [7:0] mem [0:255]; 54 55 //================================================= 56 // Read logic 57 //================================================= 58 always @ (posedge mif.clk) 59 if (mif.reset) mif.datao <= 0; 60 else if (mif.ce && !mif.we) mif.datao <= mem[mif.addr]; 61 62 //================================================= 63 // Write Logic 64 //================================================= 65 always @ (posedge mif.clk) 66 if (mif.ce && mif.we) mem[mif.addr] <= mif.datai; 67 68 endmodule 69 70 //+++++++++++++++++++++++++++++++++++++++++++++++++ 71 // Testbench 72 //+++++++++++++++++++++++++++++++++++++++++++++++++ 73 module coverage_covergroup(); 74 75 logic clk = 0; 76 always #10 clk++; 77 //================================================= 78 // Instianciate Interface and DUT 79 //================================================= 80 mem_if miff(clk); 81 simple_if U_dut(miff); 82 //================================================= 83 // Default clocking 84 //================================================= 85 default clocking dclk @ (posedge clk); 86 87 endclocking 88 //================================================= 89 // Test Vector generation 90 //================================================= 91 initial begin 92 miff.reset <= 1; 93 miff.ce <= 1'b0; 94 miff.we <= 1'b0; 95 miff.addr <= 0; 96 miff.datai <= 0; 97 ##1 miff.reset <= 0; 98 for (int i = 0; i < 3; i ++ ) begin 99 ##1 miff.ce <= 1'b1; 100 miff.we <= 1'b1; 101 miff.addr <= i; 102 miff.datai <= $random; 103 ##3 miff.ce <= 1'b0; 104 $display ("@%0dns Write access address %x, data %x", 105 $time,miff.addr,miff.datai); 106 end 107 for (int i = 0; i < 3; i ++ ) begin 108 ##1 miff.ce <= 1'b1; 109 miff.we <= 1'b0; 110 miff.addr <= i; 111 ##3 miff.ce <= 1'b0; 112 $display ("@%0dns Read access address %x, data %x", 113 $time,miff.addr,miff.datao); 114 end 115 #10 $finish; 116 end 117 118 endmodule 119 120 //simulation 121 @90ns Write access address 00, data 24 122 @170ns Write access address 01, data 81 123 @250ns Write access address 02, data 09 124 @330ns Read access address 00, data 24 125 @410ns Read access address 01, data 81 126 @490ns Read access address 02, data 09

4.1 Generic coverage group

- 通常情况下,covergroup是根据已知的变量进行编码的,如地址、数据或响应;

- 有时,我们不希望covergroup是通用的,这样同一个covergroup就可以实例化多次,并且每一个实例都在他自己的变量集上起作用;

- 通用covergroup是通过传递变量特征作为参数来创建的,就像task和function一样;

1 //+++++++++++++++++++++++++++++++++++++++++++++++++ 2 // Define the interface with coverage 3 //+++++++++++++++++++++++++++++++++++++++++++++++++ 4 interface mem_if (input wire clk); 5 logic reset; 6 logic we; 7 logic ce; 8 logic [7:0] datai; 9 logic [7:0] datao; 10 logic [7:0] addr; 11 //================================================= 12 // Clocking block for testbench 13 //================================================= 14 clocking cb @ (posedge clk); 15 output reset, we, ce, datai,addr; 16 input datao; 17 endclocking 18 //================================================= 19 // Coverage Group in interface 20 //================================================= 21 covergroup address_cov (ref logic [7:0] address, 22 input int low, int high) @ (posedge ce); 23 ADDRESS : coverpoint address { 24 bins low = {0,low}; 25 bins med = {low,high}; 26 } 27 endgroup 28 //================================================= 29 // Instance of covergroup 30 //================================================= 31 address_cov acov_low = new(addr,0,10); 32 address_cov acov_med = new(addr,11,20); 33 address_cov acov_high = new(addr,21,30); 34 35 endinterface 36 //+++++++++++++++++++++++++++++++++++++++++++++++++ 37 // DUT With interface 38 //+++++++++++++++++++++++++++++++++++++++++++++++++ 39 module simple_if (mem_if mif); 40 // Memory array 41 logic [7:0] mem [0:255]; 42 43 //================================================= 44 // Read logic 45 //================================================= 46 always @ (posedge mif.clk) 47 if (mif.reset) mif.datao <= 0; 48 else if (mif.ce && !mif.we) mif.datao <= mem[mif.addr]; 49 50 //================================================= 51 // Write Logic 52 //================================================= 53 always @ (posedge mif.clk) 54 if (mif.ce && mif.we) mem[mif.addr] <= mif.datai; 55 56 endmodule 57 58 //+++++++++++++++++++++++++++++++++++++++++++++++++ 59 // Testbench 60 //+++++++++++++++++++++++++++++++++++++++++++++++++ 61 module coverage_covergroup(); 62 63 logic clk = 0; 64 always #10 clk++; 65 //================================================= 66 // Instianciate Interface and DUT 67 //================================================= 68 mem_if miff(clk); 69 simple_if U_dut(miff); 70 //================================================= 71 // Default clocking 72 //================================================= 73 default clocking dclk @ (posedge clk); 74 75 endclocking 76 //================================================= 77 // Test Vector generation 78 //================================================= 79 initial begin 80 miff.reset <= 1; 81 miff.ce <= 1'b0; 82 miff.we <= 1'b0; 83 miff.addr <= 0; 84 miff.datai <= 0; 85 ##1 miff.reset <= 0; 86 for (int i = 0; i < 3; i ++ ) begin 87 ##1 miff.ce <= 1'b1; 88 miff.we <= 1'b1; 89 miff.addr <= i; 90 miff.datai <= $random; 91 ##3 miff.ce <= 1'b0; 92 $display ("@%0dns Write access address %x, data %x", 93 $time,miff.addr,miff.datai); 94 end 95 for (int i = 0; i < 3; i ++ ) begin 96 ##1 miff.ce <= 1'b1; 97 miff.we <= 1'b0; 98 miff.addr <= i; 99 ##3 miff.ce <= 1'b0; 100 $display ("@%0dns Read access address %x, data %x", 101 $time,miff.addr,miff.datao); 102 end 103 #10 $finish; 104 end 105 106 endmodule 107 108 //simulaion 109 110 @90ns Write access address 00, data 24 111 @170ns Write access address 01, data 81 112 @250ns Write access address 02, data 09 113 @330ns Read access address 00, data 24 114 @410ns Read access address 01, data 81 115 @490ns Read access address 02, data 09 116 117 //report 118 =========================================================== 119 Group : coverage_covergroup.miff::address_cov 120 =========================================================== 121 SCORE WEIGHT GOAL 122 100.00 1 100 123 ----------------------------------------------------------- 124 Summary for Group coverage_covergroup.miff::address_cov 125 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 126 Variables 2 0 2 100.00 127 128 Variables for Group coverage_covergroup.miff::address_cov 129 130 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 131 ADDRESS 2 0 2 100.00 100 1 132 ----------------------------------------------------------- 133 Summary for Variable ADDRESS 134 135 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 136 User Defined Bins 2 0 2 100.00 137 138 User Defined Bins for ADDRESS 139 Bins 140 141 NAME COUNT AT LEAST 142 med 2 1 143 low 6 1

4.2 Implicit bins creation

- 在任何covergroup中,都需要定义bins,在没有定义bins时,模拟器会自动创建隐式bins,

1 module test(); 2 3 logic [7:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 // Set this option to limit number of auto bins created 9 option.auto_bin_max = 10; 10 // See no bins are declared here, Not a good idea 11 } 12 endgroup 13 14 address_cov my_cov = new(); 15 16 initial begin 17 ce <= 0; 18 addr <= 0; 19 $monitor("ce %b addr 8'h%x",ce,addr); 20 repeat (10) begin 21 addr = $random(); 22 ce <= 1; 23 #10; 24 ce <= 0; 25 #10; 26 end 27 end 28 29 endmodule 30 31 //simulation 32 33 ce 1 addr 8'h00 34 ce 0 addr 8'h00 35 ce 1 addr 8'h81 36 ce 0 addr 8'h81 37 ce 1 addr 8'h09 38 ce 0 addr 8'h09 39 ce 1 addr 8'h63 40 ce 0 addr 8'h63 41 ce 1 addr 8'h0d 42 ce 0 addr 8'h0d 43 ce 1 addr 8'h8d 44 ce 0 addr 8'h8d 45 ce 1 addr 8'h65 46 ce 0 addr 8'h65 47 ce 1 addr 8'h12 48 ce 0 addr 8'h12 49 ce 1 addr 8'h01 50 ce 0 addr 8'h01 51 ce 1 addr 8'h0d 52 ce 0 addr 8'h0d 53 54 //report 55 Group : test::address_cov 56 =========================================================== 57 Group : test::address_cov 58 =========================================================== 59 SCORE WEIGHT GOAL 60 40.00 1 100 61 ----------------------------------------------------------- 62 Summary for Group test::address_cov 63 64 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 65 Variables 10 6 4 40.00 66 67 Variables for Group test::address_cov 68 69 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 70 ADDRESS 10 6 4 40.00 100 1 71 ----------------------------------------------------------- 72 Summary for Variable ADDRESS 73 74 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 75 Automatically Generated Bins 10 6 4 40.00 76 77 Automatically Generated Bins for ADDRESS 78 79 Uncovered bins 80 81 NAME COUNT AT LEAST NUMBER 82 [auto[25:49] - auto[50:74]] -- -- 2 83 [auto[150:174] - auto[225:255]] -- -- 4 84 85 Covered bins 86 NAME COUNT AT LEAST 87 auto[0:24] 6 1 88 auto[75:99] 1 1 89 auto[100:124] 1 1 90 auto[125:149] 2 1

4.3 Expelicity bins creation

显式定义bins是一个不错的选择;

1 module test(); 2 3 logic [7:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 // Bins are explicity declared, This is prefered way 9 bins low = {0,10}; 10 bins med = {11,20}; 11 bins value_255 = {255}; 12 } 13 endgroup 14 15 address_cov my_cov = new(); 16 17 initial begin 18 ce <= 0; 19 addr <= 0; 20 $monitor("ce %b addr 8'h%x",ce,addr); 21 repeat (10) begin 22 addr = $random(); 23 ce <= 1; 24 #10; 25 ce <= 0; 26 #10; 27 end 28 end 29 30 endmodule 31 32 //simulation 33 34 ce 1 addr 8'h00 35 ce 0 addr 8'h00 36 ce 1 addr 8'h81 37 ce 0 addr 8'h81 38 ce 1 addr 8'h09 39 ce 0 addr 8'h09 40 ce 1 addr 8'h63 41 ce 0 addr 8'h63 42 ce 1 addr 8'h0d 43 ce 0 addr 8'h0d 44 ce 1 addr 8'h8d 45 ce 0 addr 8'h8d 46 ce 1 addr 8'h65 47 ce 0 addr 8'h65 48 ce 1 addr 8'h12 49 ce 0 addr 8'h12 50 ce 1 addr 8'h01 51 ce 0 addr 8'h01 52 ce 1 addr 8'h0d 53 ce 0 addr 8'h0d 54 55 //report 56 57 =========================================================== 58 Group : test::address_cov 59 =========================================================== 60 SCORE WEIGHT GOAL 61 33.33 1 100 62 ----------------------------------------------------------- 63 Summary for Group test::address_cov 64 65 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 66 Variables 3 2 1 33.33 67 68 Variables for Group test::address_cov 69 70 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 71 ADDRESS 3 2 1 33.33 100 1 72 ----------------------------------------------------------- 73 Summary for Variable ADDRESS 74 75 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 76 User Defined Bins 3 2 1 33.33 77 78 User Defined Bins for ADDRESS 79 80 Uncovered bins 81 82 NAME COUNT AT LEAST NUMBER 83 value_255 0 1 1 84 med 0 1 1 85 86 Covered bins 87 88 NAME COUNT AT LEAST 89 low 1 1

4.4 Array of bins creation

可以让模拟器隐式创建bins数组,用户显式创建数组的值;

1 module test(); 2 3 logic [7:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 // This should create 11 bins 9 bins low[] = {[0:10]}; 10 // This should create 10 bins 11 bins med[] = {[11:20]}; 12 } 13 endgroup 14 15 address_cov my_cov = new(); 16 17 initial begin 18 ce <= 0; 19 addr <= 0; 20 $monitor("ce %b addr 8'h%x",ce,addr); 21 repeat (10) begin 22 addr = $random(); 23 ce <= 1; 24 #10; 25 ce <= 0; 26 #10; 27 end 28 end 29 30 endmodule 31 32 //simulation 33 34 ce 1 addr 8'h00 35 ce 0 addr 8'h00 36 ce 1 addr 8'h81 37 ce 0 addr 8'h81 38 ce 1 addr 8'h09 39 ce 0 addr 8'h09 40 ce 1 addr 8'h63 41 ce 0 addr 8'h63 42 ce 1 addr 8'h0d 43 ce 0 addr 8'h0d 44 ce 1 addr 8'h8d 45 ce 0 addr 8'h8d 46 ce 1 addr 8'h65 47 ce 0 addr 8'h65 48 ce 1 addr 8'h12 49 ce 0 addr 8'h12 50 ce 1 addr 8'h01 51 ce 0 addr 8'h01 52 ce 1 addr 8'h0d 53 ce 0 addr 8'h0d 54 55 //report 56 57 =========================================================== 58 Group : test::address_cov 59 =========================================================== 60 SCORE WEIGHT GOAL 61 23.81 1 100 62 ----------------------------------------------------------- 63 Summary for Group test::address_cov 64 65 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 66 Variables 21 16 5 23.81 67 68 Variables for Group test::address_cov 69 70 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 71 ADDRESS 21 16 5 23.81 100 1 72 ----------------------------------------------------------- 73 Summary for Variable ADDRESS 74 75 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 76 User Defined Bins 21 16 5 23.81 77 78 User Defined Bins for ADDRESS 79 80 Uncovered bins 81 82 NAME COUNT AT LEAST NUMBER 83 med_0b 0 1 1 84 med_0c 0 1 1 85 med_0e 0 1 1 86 med_0f 0 1 1 87 med_10 0 1 1 88 med_11 0 1 1 89 med_13 0 1 1 90 med_14 0 1 1 91 low_02 0 1 1 92 low_03 0 1 1 93 low_04 0 1 1 94 low_05 0 1 1 95 low_06 0 1 1 96 low_07 0 1 1 97 low_08 0 1 1 98 low_0a 0 1 1 99 100 Covered bins 101 102 NAME COUNT AT LEAST 103 med_0d 2 1 104 med_12 1 1 105 low_00 1 1 106 low_01 1 1 107 low_09 1 1

4.5 Deault bins creation

- default bins 捕获隐式bin定义中没有覆盖的所有值,在报告覆盖率时,在default中的不会考虑在覆盖率中;

1 module test(); 2 3 logic [7:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 bins low = {0,10}; 9 // All other values are not counted in coverage calculation 10 bins lazy = default; 11 } 12 endgroup 13 14 address_cov my_cov = new(); 15 16 initial begin 17 ce <= 0; 18 addr <= 0; 19 $monitor("ce %b addr 8'h%x",ce,addr); 20 repeat (10) begin 21 addr = $random(); 22 ce <= 1; 23 #10; 24 ce <= 0; 25 #10; 26 end 27 end 28 29 endmodule 30 31 //simulation 32 33 ce 1 addr 8'h00 34 ce 0 addr 8'h00 35 ce 1 addr 8'h81 36 ce 0 addr 8'h81 37 ce 1 addr 8'h09 38 ce 0 addr 8'h09 39 ce 1 addr 8'h63 40 ce 0 addr 8'h63 41 ce 1 addr 8'h0d 42 ce 0 addr 8'h0d 43 ce 1 addr 8'h8d 44 ce 0 addr 8'h8d 45 ce 1 addr 8'h65 46 ce 0 addr 8'h65 47 ce 1 addr 8'h12 48 ce 0 addr 8'h12 49 ce 1 addr 8'h01 50 ce 0 addr 8'h01 51 ce 1 addr 8'h0d 52 ce 0 addr 8'h0d 53 54 //report 55 =========================================================== 56 Group : test::address_cov 57 =========================================================== 58 SCORE WEIGHT GOAL 59 100.00 1 100 60 ----------------------------------------------------------- 61 Summary for Group test::address_cov 62 63 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 64 Variables 1 0 1 100.00 65 66 Variables for Group test::address_cov 67 68 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 69 ADDRESS 1 0 1 100.00 100 1 70 ----------------------------------------------------------- 71 Summary for Variable ADDRESS 72 73 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 74 User Defined Bins 1 0 1 100.00 75 76 User Defined Bins for ADDRESS 77 78 Excluded/Illegal bins 79 80 NAME COUNT 81 lazy 9 Excluded 82 83 Covered bins 84 85 NAME COUNT AT LEAST 86 low 1 1

4.6 Transition bins creation

- 转换覆盖率用来检测是否发生了所需的转换,也用于检查是否发生了合法/非法的 转换;

- 在任何覆盖计划中transition coverage是一个很重要的测试内容;

- 一些 transition coverage 的典型的例子:

- 读跟随写到同一个内存地址;

- CPU的零标志测试后跳转到指令执行;

- 高优先级帧和低优先值帧;

- cache控制器的先miss后hit

4.6.1 Transition bins creation:sequence

一个值到另一个值的转换:

WRITE => READ;

WRITE => READ => WRITE;

1 module test(); 2 3 logic [7:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 // simple transition bin 9 bins adr_0_to_1 = (0=>1); 10 bins adr_1_to_0 = (1=>0); 11 bins adr_1_to_2 = (1=>2); 12 bins adr_2_to_1 = (1=>0); 13 bins adr_0_1_2_3 = (0=>1=>2=>3); 14 bins adr_1_4_7 = (1=>4=>7); 15 } 16 endgroup 17 18 address_cov my_cov = new(); 19 20 initial begin 21 ce <= 0; 22 addr <= 0; 23 $monitor("ce %b addr 8'h%x",ce,addr); 24 repeat (10) begin 25 ce <= 1; 26 #10; 27 ce <= 0; 28 addr ++; 29 #10; 30 end 31 end 32 33 endmodule 34 35 //simulation 36 37 ce 1 addr 8'h00 38 ce 0 addr 8'h01 39 ce 1 addr 8'h01 40 ce 0 addr 8'h02 41 ce 1 addr 8'h02 42 ce 0 addr 8'h03 43 ce 1 addr 8'h03 44 ce 0 addr 8'h04 45 ce 1 addr 8'h04 46 ce 0 addr 8'h05 47 ce 1 addr 8'h05 48 ce 0 addr 8'h06 49 ce 1 addr 8'h06 50 ce 0 addr 8'h07 51 ce 1 addr 8'h07 52 ce 0 addr 8'h08 53 ce 1 addr 8'h08 54 ce 0 addr 8'h09 55 ce 1 addr 8'h09 56 ce 0 addr 8'h0a 57 58 //report 59 =========================================================== 60 Group : test::address_cov 61 =========================================================== 62 SCORE WEIGHT GOAL 63 50.00 1 100 64 ----------------------------------------------------------- 65 Summary for Group test::address_cov 66 67 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 68 Variables 6 3 3 50.00 69 70 Variables for Group test::address_cov 71 72 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 73 ADDRESS 6 3 3 50.00 100 1 74 ----------------------------------------------------------- 75 Summary for Variable ADDRESS 76 77 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 78 User Defined Bins 6 3 3 50.00 79 80 User Defined Bins for ADDRESS 81 82 Uncovered bins 83 84 NAME COUNT AT LEAST NUMBER 85 adr_1_4_7 0 1 1 86 adr_2_to_1 0 1 1 87 adr_1_to_0 0 1 1 88 89 Covered bins 90 91 NAME COUNT AT LEAST 92 adr_0_1_2_3 1 1 93 adr_1_to_2 1 1 94 adr_0_to_1 1 1

4.6.2 Transition bins creation ; default sequence

在default中的coverpoint不会考虑在覆盖率中;

1 module test(); 2 3 logic [7:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 // simple transition bin 9 bins adr_0_to_1 = (0=>1); 10 bins adr_1_to_0 = (1=>0); 11 bins adr_1_to_2 = (1=>2); 12 bins adr_2_to_1 = (1=>0); 13 bins allother = default sequence; 14 } 15 endgroup 16 17 address_cov my_cov = new(); 18 19 initial begin 20 ce <= 0; 21 addr <= 0; 22 $monitor("ce %b addr 8'h%x",ce,addr); 23 repeat (10) begin 24 ce <= 1; 25 #10; 26 ce <= 0; 27 addr ++; 28 #10; 29 end 30 end 31 32 endmodule 33 34 //simulation 35 36 ce 1 addr 8'h00 37 ce 0 addr 8'h01 38 ce 1 addr 8'h01 39 ce 0 addr 8'h02 40 ce 1 addr 8'h02 41 ce 0 addr 8'h03 42 ce 1 addr 8'h03 43 ce 0 addr 8'h04 44 ce 1 addr 8'h04 45 ce 0 addr 8'h05 46 ce 1 addr 8'h05 47 ce 0 addr 8'h06 48 ce 1 addr 8'h06 49 ce 0 addr 8'h07 50 ce 1 addr 8'h07 51 ce 0 addr 8'h08 52 ce 1 addr 8'h08 53 ce 0 addr 8'h09 54 ce 1 addr 8'h09 55 ce 0 addr 8'h0a 56 57 //report 58 =========================================================== 59 Group : test::address_cov 60 =========================================================== 61 SCORE WEIGHT GOAL 62 50.00 1 100 63 ----------------------------------------------------------- 64 Summary for Group test::address_cov 65 66 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 67 Variables 4 2 2 50.00 68 69 Variables for Group test::address_cov 70 71 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 72 ADDRESS 4 2 2 50.00 100 1 73 ----------------------------------------------------------- 74 Summary for Variable ADDRESS 75 76 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 77 User Defined Bins 4 2 2 50.00 78 79 User Defined Bins for ADDRESS 80 81 Uncovered bins 82 83 NAME COUNT AT LEAST NUMBER 84 adr_2_to_1 0 1 1 85 adr_1_to_0 0 1 1 86 87 Covered bins 88 89 NAME COUNT AT LEAST 90 adr_1_to_2 1 1 91 adr_0_to_1 1 1

4.6.3 Transition bins creation:set of transition

set of transition : 过渡集,是一种转换行为的数组;

1 module test(); 2 3 logic [2:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 // simple transition bin 9 bins adr_low[] = (0,1=>2,3); 10 bins adr_med[] = (1,2=>3,4); 11 bins adr_high[] = (3,4=>5,6); 12 } 13 endgroup 14 15 address_cov my_cov = new(); 16 17 initial begin 18 ce <= 0; 19 addr <= 0; 20 $monitor("ce %b addr 8'h%x",ce,addr); 21 repeat (10) begin 22 ce <= 1; 23 addr <= $random; 24 #10; 25 ce <= 0; 26 #10; 27 end 28 end 29 30 endmodule 31 32 //simulation 33 34 ce 1 addr 8'h4 35 ce 0 addr 8'h4 36 ce 1 addr 8'h1 37 ce 0 addr 8'h1 38 ce 1 addr 8'h1 39 ce 0 addr 8'h1 40 ce 1 addr 8'h3 41 ce 0 addr 8'h3 42 ce 1 addr 8'h5 43 ce 0 addr 8'h5 44 ce 1 addr 8'h5 45 ce 0 addr 8'h5 46 ce 1 addr 8'h5 47 ce 0 addr 8'h5 48 ce 1 addr 8'h2 49 ce 0 addr 8'h2 50 ce 1 addr 8'h1 51 ce 0 addr 8'h1 52 ce 1 addr 8'h5 53 ce 0 addr 8'h5 54 55 //report 56 =========================================================== 57 Group : test::address_cov 58 =========================================================== 59 SCORE WEIGHT GOAL 60 25.00 1 100 61 ----------------------------------------------------------- 62 Summary for Group test::address_cov 63 64 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 65 Variables 12 9 3 25.00 66 67 Variables for Group test::address_cov 68 69 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 70 ADDRESS 12 9 3 25.00 100 1 71 ----------------------------------------------------------- 72 Summary for Variable ADDRESS 73 74 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 75 User Defined Bins 12 9 3 25.00 76 77 User Defined Bins for ADDRESS 78 79 Uncovered bins 80 81 NAME COUNT AT LEAST NUMBER 82 adr_high:3->6 0 1 1 83 adr_high:4->5 0 1 1 84 adr_high:4->6 0 1 1 85 adr_med:1->4 0 1 1 86 adr_med:2->3 0 1 1 87 adr_med:2->4 0 1 1 88 adr_low:0->2 0 1 1 89 adr_low:0->3 0 1 1 90 adr_low:1->2 0 1 1 91 92 Covered bins 93 94 NAME COUNT AT LEAST 95 adr_high:3->5 1 1 96 adr_med:1->3 1 1 97 adr_low:1->3 1 1

4.6.4 Transition bins creation:consecutive repetion

- 检查相同的值重复次数,次数少可以通过下面的方法手动输入:

WRITE =>WRITE =>WRITE =>WRITE =>;

- 较长序列可以通过下面方式实现:

10[*WRITE]

1 module test(); 2 3 logic [2:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 bins adr_0_2times = (0[*2]); 9 bins adr_1_3times = (1[*3]); 10 bins adr_2_4times = (2[*4]); 11 } 12 endgroup 13 14 address_cov my_cov = new(); 15 16 initial begin 17 ce <= 0; 18 addr <= 2; 19 $monitor("ce %b addr 8'h%x",ce,addr); 20 repeat (10) begin 21 ce <= 1; 22 #10; 23 ce <= 0; 24 #10; 25 end 26 end 27 28 endmodule 29 30 //simulation 31 32 ce 1 addr 8'h2 33 ce 0 addr 8'h2 34 ce 1 addr 8'h2 35 ce 0 addr 8'h2 36 ce 1 addr 8'h2 37 ce 0 addr 8'h2 38 ce 1 addr 8'h2 39 ce 0 addr 8'h2 40 ce 1 addr 8'h2 41 ce 0 addr 8'h2 42 ce 1 addr 8'h2 43 ce 0 addr 8'h2 44 ce 1 addr 8'h2 45 ce 0 addr 8'h2 46 ce 1 addr 8'h2 47 ce 0 addr 8'h2 48 ce 1 addr 8'h2 49 ce 0 addr 8'h2 50 ce 1 addr 8'h2 51 ce 0 addr 8'h2 52 53 //report 54 =========================================================== 55 Group : test::address_cov 56 =========================================================== 57 SCORE WEIGHT GOAL 58 33.33 1 100 59 ----------------------------------------------------------- 60 Summary for Group test::address_cov 61 62 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 63 Variables 3 2 1 33.33 64 65 Variables for Group test::address_cov 66 67 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 68 ADDRESS 3 2 1 33.33 100 1 69 ----------------------------------------------------------- 70 Summary for Variable ADDRESS 71 72 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 73 User Defined Bins 3 2 1 33.33 74 75 User Defined Bins for ADDRESS 76 77 Uncovered bins 78 79 NAME COUNT AT LEAST NUMBER 80 adr_1_3times 0 1 1 81 adr_0_2times 0 1 1 82 83 Covered bins 84 85 NAME COUNT AT LEAST 86 adr_2_4times 7 1

4.6.5 Transition bins creation:range of repetition

覆盖一定范围中的重复:

(WRITE[*2:5]);

1 module test(); 2 3 logic [2:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 bins adr0[] = (0[*1:4]); 9 bins adr1[] = (1[*1:2]); 10 } 11 endgroup 12 13 address_cov my_cov = new(); 14 15 initial begin 16 ce <= 0; 17 $monitor("ce %b addr 8'h%x",ce,addr); 18 repeat (10) begin 19 ce <= 1; 20 addr <= $urandom_range(0,1); 21 #10; 22 ce <= 0; 23 #10; 24 end 25 end 26 27 endmodule 28 29 //simulation 30 31 ce 1 addr 8'h0 32 ce 0 addr 8'h0 33 ce 1 addr 8'h0 34 ce 0 addr 8'h0 35 ce 1 addr 8'h1 36 ce 0 addr 8'h1 37 ce 1 addr 8'h0 38 ce 0 addr 8'h0 39 ce 1 addr 8'h1 40 ce 0 addr 8'h1 41 ce 1 addr 8'h1 42 ce 0 addr 8'h1 43 ce 1 addr 8'h0 44 ce 0 addr 8'h0 45 ce 1 addr 8'h1 46 ce 0 addr 8'h1 47 ce 1 addr 8'h0 48 ce 0 addr 8'h0 49 ce 1 addr 8'h1 50 ce 0 addr 8'h1 51 52 //report 53 ===================================================================== 54 Group : test::address_cov 55 ===================================================================== 56 SCORE WEIGHT GOAL 57 100.00 1 100 58 --------------------------------------------------------------------- 59 Summary for Group test::address_cov 60 61 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 62 Variables 2 0 2 100.00 63 64 Variables for Group test::address_cov 65 66 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 67 ADDRESS 2 0 2 100.00 100 1 68 --------------------------------------------------------------------- 69 Summary for Variable ADDRESS 70 71 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 72 User Defined Bins 2 0 2 100.00 73 74 User Defined Bins for ADDRESS 75 76 Bins 77 78 NAME COUNT AT LEAST 79 adr1:1[*[1:2]] 5 1 80 adr0:0[*[1:4]] 5 1

4.6.6 Transition bins creation ;repetition with nonconseutive

非连续的重复; 2[->WRITE];

重复操作符可以混合使用;

1 module test(); 2 3 logic [2:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 bins adr = (0=>2[->2]=>1); 9 } 10 endgroup 11 12 address_cov my_cov = new(); 13 14 initial begin 15 ce <= 0; 16 $monitor("ce %b addr 8'h%x",ce,addr); 17 repeat (10) begin 18 ce <= 1; 19 addr <= $urandom_range(0,2); 20 #10; 21 ce <= 0; 22 #10; 23 end 24 end 25 26 endmodule 27 28 //simulation 29 30 ce 1 addr 8'h2 31 ce 0 addr 8'h2 32 ce 1 addr 8'h2 33 ce 0 addr 8'h2 34 ce 1 addr 8'h1 35 ce 0 addr 8'h1 36 ce 1 addr 8'h0 37 ce 0 addr 8'h0 38 ce 1 addr 8'h1 39 ce 0 addr 8'h1 40 ce 1 addr 8'h2 41 ce 0 addr 8'h2 42 ce 1 addr 8'h1 43 ce 0 addr 8'h1 44 ce 1 addr 8'h0 45 ce 0 addr 8'h0 46 ce 1 addr 8'h0 47 ce 0 addr 8'h0 48 ce 1 addr 8'h2 49 ce 0 addr 8'h2 50 51 //report 52 53 =========================================================== 54 Group : test::address_cov 55 =========================================================== 56 SCORE WEIGHT GOAL 57 0.00 1 100 58 ----------------------------------------------------------- 59 Summary for Group test::address_cov 60 61 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 62 Variables 1 1 0 0.00 63 64 Variables for Group test::address_cov 65 66 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 67 ADDRESS 1 1 0 0.00 100 1 68 ------------------------------------------------------------------------------- 69 Summary for Variable ADDRESS 70 71 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 72 User Defined Bins 1 1 0 0.00 73 74 User Defined Bins for ADDRESS 75 76 Uncovered bins 77 78 NAME COUNT AT LEAST NUMBER 79 adr 0 1 1

4.6.7 Wildcard bin creation

- 通配符定义下只有x,z或者?作为1或者0的通配处理;

-

1 wildcard bins abc = {2'b1?};

这代表abc可以匹配 2'b10 或者 2'b11;

1 module test(); 2 3 logic [2:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 // Normal transition bibs 9 wildcard bins adr0 = {3'b11?}; 10 // We can use wildcard in transition bins also 11 wildcard bins adr1 = (3'b1x0 => 3'bx00); 12 wildcard bins adr2 = (3'b1?0 => 3'b?00); 13 } 14 endgroup 15 16 address_cov my_cov = new(); 17 18 initial begin 19 ce <= 0; 20 $monitor("ce %b addr 8'h%x",ce,addr); 21 repeat (10) begin 22 ce <= 1; 23 addr <= $urandom_range(0,2); 24 #10; 25 ce <= 0; 26 #10; 27 end 28 end 29 30 endmodule 31 //simualation 32 33 ce 1 addr 8'h2 34 ce 0 addr 8'h2 35 ce 1 addr 8'h2 36 ce 0 addr 8'h2 37 ce 1 addr 8'h1 38 ce 0 addr 8'h1 39 ce 1 addr 8'h0 40 ce 0 addr 8'h0 41 ce 1 addr 8'h1 42 ce 0 addr 8'h1 43 ce 1 addr 8'h2 44 ce 0 addr 8'h2 45 ce 1 addr 8'h1 46 ce 0 addr 8'h1 47 ce 1 addr 8'h0 48 ce 0 addr 8'h0 49 ce 1 addr 8'h0 50 ce 0 addr 8'h0 51 ce 1 addr 8'h2 52 ce 0 addr 8'h2 53 54 //report 55 56 =========================================================== 57 Group : test::address_cov 58 =========================================================== 59 SCORE WEIGHT GOAL 60 0.00 1 100 61 ----------------------------------------------------------- 62 Summary for Group test::address_cov 63 64 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 65 Variables 3 3 0 0.00 66 67 Variables for Group test::address_cov 68 69 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 70 ADDRESS 3 3 0 0.00 100 1 71 ----------------------------------------------------------- 72 Summary for Variable ADDRESS 73 74 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 75 User Defined Bins 3 3 0 0.00 76 77 User Defined Bins for ADDRESS 78 79 Uncovered bins 80 81 NAME COUNT AT LEAST NUMBER 82 adr0 0 1 1 83 adr2 0 1 1 84 adr1 0 1 1

4.6.8 Ignore bin

- 与coverpoint相关的一组值换转换可以通过将其指定为ignore_bins显式地排除在覆盖率收集之外;

- ignore_bins 语法用于动态禁用覆盖率bin,也可用于建模VERA的覆盖率形状语法。

1 module test(); 2 3 logic [2:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 ignore_bins ignore_tran = (0=>2=>1); 9 ignore_bins ignore_vals = {0,1,2,3}; 10 } 11 endgroup 12 13 address_cov my_cov = new(); 14 15 initial begin 16 ce <= 0; 17 $monitor("ce %b addr 8'h%x",ce,addr); 18 repeat (10) begin 19 ce <= 1; 20 addr <= $urandom_range(0,7); 21 #10; 22 ce <= 0; 23 #10; 24 end 25 end 26 27 endmodule 28 29 //simulation 30 ce 1 addr 8'h6 31 ce 0 addr 8'h6 32 ce 1 addr 8'h4 33 ce 0 addr 8'h4 34 ce 1 addr 8'h5 35 ce 0 addr 8'h5 36 ce 1 addr 8'h2 37 ce 0 addr 8'h2 38 ce 1 addr 8'h3 39 ce 0 addr 8'h3 40 ce 1 addr 8'h7 41 ce 0 addr 8'h7 42 ce 1 addr 8'h0 43 ce 0 addr 8'h0 44 ce 1 addr 8'h7 45 ce 0 addr 8'h7 46 ce 1 addr 8'h6 47 ce 0 addr 8'h6 48 ce 1 addr 8'h3 49 ce 0 addr 8'h3 50 51 //report 52 =========================================================== 53 Group : test::address_cov 54 =========================================================== 55 SCORE WEIGHT GOAL 56 100.00 1 100 57 ----------------------------------------------------------- 58 Summary for Group test::address_cov 59 60 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 61 Variables 4 -3 7 100.00 62 63 Variables for Group test::address_cov 64 65 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 66 ADDRESS 4 -3 7 100.00 100 1 67 ----------------------------------------------------------- 68 Summary for Variable ADDRESS 69 70 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 71 Automatically Generated Bins 4 -3 7 100.00 72 73 Automatically Generated Bins for ADDRESS 74 75 Excluded/Illegal bins 76 77 NAME COUNT 78 ignore_tran 0 Excluded 79 ignore_vals 0 Excluded 80 [auto[0] - auto[3]] -- Excluded (4 bins) 81 82 Covered bins 83 84 NAME COUNT AT LEAST 85 auto[0] 1 1 86 auto[2] 1 1 87 auto[3] 2 1 88 auto[4] 1 1 89 auto[5] 1 1 90 auto[6] 2 1 91 auto[7] 2 1

4.6.9 Illegal bin creation

- 与覆盖点相关的一组值或者转换可以通过指定为illegal_bins来标记为非法;

- 击中一个非法的bins会导致模拟器终止模拟,结束模拟行为;

- 通常情况下,illegal bin的语法会在DUT内部变量的覆盖点或者DUT输出端口上使用。在testbench激励上使用illegal语法可以防止错误输入;

1 module test(); 2 3 logic [2:0] addr; 4 reg ce; 5 6 covergroup address_cov () @ (posedge ce); 7 ADDRESS : coverpoint addr { 8 ignore_bins ignore_tran = (0=>2=>1); 9 ignore_bins ignore_vals = {0,1,2,3}; 10 illegal_bins ignore = {5}; 11 } 12 endgroup 13 14 address_cov my_cov = new(); 15 16 initial begin 17 ce <= 0; 18 $monitor("ce %b addr 8'h%x",ce,addr); 19 repeat (10) begin 20 ce <= 1; 21 addr <= $urandom_range(0,7); 22 #10; 23 ce <= 0; 24 #10; 25 end 26 end 27 28 endmodule 29 30 //simulation 31 32 ce 1 addr 8'h6 33 ce 0 addr 8'h6 34 ce 1 addr 8'h4 35 ce 0 addr 8'h4 36 37 Error-[FCIBH] Illegal bin hit 38 /code/systemverilog/illegal_bin.sv, 7 39 test, "address_cov" 40 VERIFICATION ERROR (FUNCTIONAL COVERAGE) : Illegal state bin ignore of 41 coverpoint ADDRESS in covergroup address_cov got hit with value 0x5 42 Covergroup Instance: my_cov 43 Design hierarchy: test 44 45 //report 46 =========================================================== 47 Group : test::address_cov 48 =========================================================== 49 SCORE WEIGHT GOAL 50 66.67 1 100 51 ----------------------------------------------------------- 52 Summary for Group test::address_cov 53 54 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 55 Variables 3 1 2 66.67 56 57 Variables for Group test::address_cov 58 59 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 60 ADDRESS 3 1 2 66.67 100 1 61 ----------------------------------------------------------- 62 Summary for Variable ADDRESS 63 64 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 65 Automatically Generated Bins 3 1 2 66.67 66 67 Automatically Generated Bins for ADDRESS 68 69 Uncovered bins 70 71 NAME COUNT AT LEAST NUMBER 72 [auto[7]] 0 1 1 73 74 Excluded/Illegal bins 75 76 NAME COUNT 77 ignore_tran 0 Excluded 78 ignore_vals 0 Excluded 79 ignore 1 Excluded 80 [auto[0] - auto[3]] -- Excluded (4 bins) 81 [auto[5]] 0 Illegal 82 83 Covered bins 84 85 NAME COUNT AT LEAST 86 auto[4] 1 1 87 auto[6] 1 1

5. Cross coverage

- coverage可以指定两个或多个覆盖以及变量之间的交叉覆盖;

- 交叉覆盖使用cross构造来指定;

- 在 验证复杂系统时,验证功能点的组合是很重要的;

5.1 Auto cross coverage points

典型的交叉覆盖定义为自动的bins;

1 module test(); 2 3 logic [2:0] addr; 4 logic [1:0] cmd; 5 reg ce; 6 7 covergroup address_cov () @ (posedge ce); 8 ADDRESS : coverpoint addr { 9 bins addr0 = {0}; 10 bins addr1 = {1}; 11 bins addr2 = {2}; 12 bins addr3 = {3}; 13 } 14 CMD : coverpoint cmd { 15 bins READ = {0}; 16 bins WRITE = {1}; 17 bins IDLE = {2}; 18 } 19 CRS_ADDR_CMD : cross ADDRESS, CMD; 20 endgroup 21 22 address_cov my_cov = new(); 23 24 initial begin 25 ce <= 0; 26 $monitor("ce %b addr 8'h%x cmd %x",ce,addr,cmd); 27 repeat (10) begin 28 ce <= 1; 29 addr <= $urandom_range(0,5); 30 cmd <= $urandom_range(0,2); 31 #10; 32 ce <= 0; 33 #10; 34 end 35 end 36 37 endmodule 38 39 //simulation 40 41 ce 1 addr 8'h2 cmd 2 42 ce 0 addr 8'h2 cmd 2 43 ce 1 addr 8'h1 cmd 0 44 ce 0 addr 8'h1 cmd 0 45 ce 1 addr 8'h1 cmd 2 46 ce 0 addr 8'h1 cmd 2 47 ce 1 addr 8'h4 cmd 0 48 ce 0 addr 8'h4 cmd 0 49 ce 1 addr 8'h0 cmd 2 50 ce 0 addr 8'h0 cmd 2 51 ce 1 addr 8'h5 cmd 2 52 ce 0 addr 8'h5 cmd 2 53 ce 1 addr 8'h2 cmd 2 54 ce 0 addr 8'h2 cmd 2 55 ce 1 addr 8'h5 cmd 0 56 ce 0 addr 8'h5 cmd 0 57 ce 1 addr 8'h2 cmd 2 58 ce 0 addr 8'h2 cmd 2 59 ce 1 addr 8'h4 cmd 2 60 ce 0 addr 8'h4 cmd 2 61 62 //report 63 64 =========================================================== 65 Group : test::address_cov 66 =========================================================== 67 SCORE WEIGHT GOAL 68 58.33 1 100 69 ----------------------------------------------------------- 70 Summary for Group test::address_cov 71 72 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 73 Variables 7 2 5 70.83 74 Crosses 12 8 4 33.33 75 76 Variables for Group test::address_cov 77 78 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 79 ADDRESS 4 1 3 75.00 100 1 80 CMD 3 1 2 66.67 100 1 81 82 Crosses for Group test::address_cov 83 84 CROSS EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 85 CRS_ADDR_CMD 12 8 4 33.33 100 1 86 ----------------------------------------------------------- 87 Summary for Variable ADDRESS 88 89 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 90 User Defined Bins 4 1 3 75.00 91 92 User Defined Bins for ADDRESS 93 94 Uncovered bins 95 96 NAME COUNT AT LEAST NUMBER 97 addr3 0 1 1 98 99 Covered bins 100 101 NAME COUNT AT LEAST 102 addr2 3 1 103 addr1 2 1 104 addr0 1 1 105 ----------------------------------------------------------- 106 Summary for Variable CMD 107 108 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 109 User Defined Bins 3 1 2 66.67 110 111 User Defined Bins for CMD 112 113 Uncovered bins 114 115 NAME COUNT AT LEAST NUMBER 116 WRITE 0 1 1 117 118 Covered bins 119 120 NAME COUNT AT LEAST 121 IDLE 7 1 122 READ 3 1 123 ----------------------------------------------------------- 124 Summary for Cross CRS_ADDR_CMD 125 126 Samples crossed: ADDRESS CMD 127 CATEGORY EXPECTED UNCOVERED COVERED PERCENT MISSING 128 Automatically Generated Cross Bins 12 8 4 33.33 8 129 130 Automatically Generated Cross Bins for CRS_ADDR_CMD 131 132 Element holes 133 134 ADDRESS CMD COUNT AT LEAST NUMBER 135 [addr3] * -- -- 3 136 137 Uncovered bins 138 139 ADDRESS CMD COUNT AT LEAST NUMBER 140 [addr2] [WRITE , READ] -- -- 2 141 [addr1] [WRITE] 0 1 1 142 [addr0] [WRITE , READ] -- -- 2 143 144 Covered bins 145 146 ADDRESS CMD COUNT AT LEAST 147 addr1 IDLE 1 1 148 addr1 READ 1 1 149 addr2 IDLE 3 1 150 addr0 IDLE 1 1

5.2 User defined cross coverage points

- 通常创建自动交叉bin会导致许多覆盖漏洞,并可能导致许多奇特的忽略bin语法;

- 所有有时会使用用户自定义的语法;

- 用户定义的用于交叉覆盖的bin使用binsof和intersect定义。

1 module test(); 2 3 logic [2:0] addr; 4 logic [1:0] cmd; 5 reg ce; 6 7 covergroup address_cov () @ (posedge ce); 8 ADDRESS : coverpoint addr { 9 bins addr0 = {0}; 10 bins addr1 = {1}; 11 } 12 CMD : coverpoint cmd { 13 bins READ = {0}; 14 bins WRITE = {1}; 15 bins IDLE = {2}; 16 } 17 CRS_USER_ADDR_CMD : cross ADDRESS, CMD { 18 bins USER_ADDR0_READ = binsof(CMD) intersect {0}; 19 } 20 CRS_AUTO_ADDR_CMD : cross ADDRESS, CMD { 21 ignore_bins AUTO_ADDR_READ = binsof(CMD) intersect {0}; 22 ignore_bins AUTO_ADDR_WRITE = binsof(CMD) intersect {1} && binsof(ADDRESS) intersect{0}; 23 } 24 25 endgroup 26 27 address_cov my_cov = new(); 28 29 initial begin 30 ce <= 0; 31 $monitor("ce %b addr 8'h%x cmd %x",ce,addr,cmd); 32 repeat (10) begin 33 ce <= 1; 34 addr <= $urandom_range(0,5); 35 cmd <= $urandom_range(0,2); 36 #10; 37 ce <= 0; 38 #10; 39 end 40 end 41 42 endmodule 43 44 //simulation 45 ce 1 addr 8'h2 cmd 2 46 ce 0 addr 8'h2 cmd 2 47 ce 1 addr 8'h1 cmd 0 48 ce 0 addr 8'h1 cmd 0 49 ce 1 addr 8'h1 cmd 2 50 ce 0 addr 8'h1 cmd 2 51 ce 1 addr 8'h4 cmd 0 52 ce 0 addr 8'h4 cmd 0 53 ce 1 addr 8'h0 cmd 2 54 ce 0 addr 8'h0 cmd 2 55 ce 1 addr 8'h5 cmd 2 56 ce 0 addr 8'h5 cmd 2 57 ce 1 addr 8'h2 cmd 2 58 ce 0 addr 8'h2 cmd 2 59 ce 1 addr 8'h5 cmd 0 60 ce 0 addr 8'h5 cmd 0 61 ce 1 addr 8'h2 cmd 2 62 ce 0 addr 8'h2 cmd 2 63 ce 1 addr 8'h4 cmd 2 64 ce 0 addr 8'h4 cmd 2 65 66 //report 67 =============================================================================== 68 Group : test::address_cov 69 =============================================================================== 70 SCORE WEIGHT GOAL 71 73.33 1 100 72 ------------------------------------------------------------------------------- 73 Summary for Group test::address_cov 74 75 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 76 Variables 5 1 4 83.33 77 Crosses 8 3 5 63.33 78 79 Variables for Group test::address_cov 80 81 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 82 ADDRESS 2 0 2 100.00 100 1 83 CMD 3 1 2 66.67 100 1 84 85 Crosses for Group test::address_cov 86 87 CROSS EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 88 CRS_USER_ADDR_CMD 5 2 3 60.00 100 1 89 CRS_AUTO_ADDR_CMD 3 1 2 66.67 100 1 90 ------------------------------------------------------------------------------- 91 Summary for Variable ADDRESS 92 93 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 94 User Defined Bins 2 0 2 100.00 95 96 User Defined Bins for ADDRESS 97 98 Bins 99 100 NAME COUNT AT LEAST 101 addr1 2 1 102 addr0 1 1 103 ------------------------------------------------------------------------------- 104 Summary for Variable CMD 105 106 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 107 User Defined Bins 3 1 2 66.67 108 109 User Defined Bins for CMD 110 111 Uncovered bins 112 113 NAME COUNT AT LEAST NUMBER 114 WRITE 0 1 1 115 116 Covered bins 117 118 NAME COUNT AT LEAST 119 IDLE 7 1 120 READ 3 1 121 ------------------------------------------------------------------------------- 122 Summary for Cross CRS_USER_ADDR_CMD 123 124 Samples crossed: ADDRESS CMD 125 CATEGORY EXPECTED UNCOVERED COVERED PERCENT MISSING 126 TOTAL 5 2 3 60.00 2 127 Automatically Generated Cross Bins 4 2 2 50.00 2 128 User Defined Cross Bins 1 0 1 100.00 129 130 Automatically Generated Cross Bins for CRS_USER_ADDR_CMD 131 132 Element holes 133 ADDRESS CMD COUNT AT LEAST NUMBER 134 * [WRITE] -- -- 2 135 136 Covered bins 137 138 ADDRESS CMD COUNT AT LEAST 139 addr1 IDLE 1 1 140 addr0 IDLE 1 1 141 142 User Defined Cross Bins for CRS_USER_ADDR_CMD 143 144 Bins 145 146 NAME COUNT AT LEAST 147 USER_ADDR0_READ 1 1 148 ------------------------------------------------------------------------------- 149 Summary for Cross CRS_AUTO_ADDR_CMD 150 151 Samples crossed: ADDRESS CMD 152 CATEGORY EXPECTED UNCOVERED COVERED PERCENT MISSING 153 TOTAL 3 1 2 66.67 1 154 Automatically Generated Cross Bins 3 1 2 66.67 1 155 User Defined Cross Bins 0 0 0 156 157 Automatically Generated Cross Bins for CRS_AUTO_ADDR_CMD 158 159 Uncovered bins 160 161 ADDRESS CMD COUNT AT LEAST NUMBER 162 [addr1] [WRITE] 0 1 1 163 164 Covered bins 165 166 ADDRESS CMD COUNT AT LEAST 167 addr1 IDLE 1 1 168 addr0 IDLE 1 1 169 170 User Defined Cross Bins for CRS_AUTO_ADDR_CMD 171 172 Excluded/Illegal bins 173 174 NAME COUNT 175 AUTO_ADDR_READ 0 Excluded 176 AUTO_ADDR_WRITE 0 Excluded

6. Coverage options

- 与VERA一样,SV提供 了一些方法控制covergroup、coverpoint 以及cross的行为;

|

Options Name |

Default |

Description |

|

weight=number |

1 |

权重分配 |

|

goal=number |

90 |

指定覆盖率目标 |

|

name=string |

unique name |

指定covergroup实例的名称 |

|

comment=string |

注释指定 |

|

|

at_least=number |

1 |

bin的最小击中次数 |

|

detect_overlap=boolean |

0 |

检测bins的重叠; 当为true时,如果coverpoint的两个 bins的范围列表或者转换 列表有重叠就会发出警告; |

|

auto_bin_max=number |

64 |

在没有显示指定bins的时候,设定允许自动创建最大bins的数量; |

|

cross_num_print_missing = number |

0 |

必须保存到覆盖率数据并在覆盖率报告中打印的未覆盖cross bins; |

|

per_instance=boolean |

0 |

当为true时,会跟踪每个covergroup实例的覆盖率。 |

- 下面的选项可以提高覆盖率的收敛:

- weight = nember

- goal = nember

- al_least = nember

- per_instance = boolean

1 module test(); 2 3 logic [2:0] addr; 4 wire [2:0] addr2; 5 reg ce; 6 7 assign addr2 = addr + 1; 8 9 covergroup address_cov () @ (posedge ce); 10 option.name = "address_cov"; 11 option.comment = "This is cool"; 12 option.per_instance = 1; 13 option.goal = 100; 14 option.weight = 50; 15 ADDRESS : coverpoint addr { 16 option.auto_bin_max = 100; 17 } 18 ADDRESS2 : coverpoint addr2 { 19 option.auto_bin_max = 10; 20 } 21 endgroup 22 23 address_cov my_cov = new(); 24 25 initial begin 26 my_cov.ADDRESS.option.at_least = 1; 27 my_cov.ADDRESS2.option.at_least = 2; 28 ce <= 0; 29 $monitor("ce %b addr 8'h%x addr2 8'h%x",ce,addr,addr2); 30 repeat (10) begin 31 ce <= 1; 32 addr <= $urandom_range(0,7); 33 #10; 34 ce <= 0; 35 #10; 36 end 37 end 38 39 endmodule 40 41 //simulation 42 43 ce 1 addr 8'h6 addr2 8'h7 44 ce 0 addr 8'h6 addr2 8'h7 45 ce 1 addr 8'h4 addr2 8'h5 46 ce 0 addr 8'h4 addr2 8'h5 47 ce 1 addr 8'h5 addr2 8'h6 48 ce 0 addr 8'h5 addr2 8'h6 49 ce 1 addr 8'h2 addr2 8'h3 50 ce 0 addr 8'h2 addr2 8'h3 51 ce 1 addr 8'h3 addr2 8'h4 52 ce 0 addr 8'h3 addr2 8'h4 53 ce 1 addr 8'h7 addr2 8'h0 54 ce 0 addr 8'h7 addr2 8'h0 55 ce 1 addr 8'h0 addr2 8'h1 56 ce 0 addr 8'h0 addr2 8'h1 57 ce 1 addr 8'h7 addr2 8'h0 58 ce 0 addr 8'h7 addr2 8'h0 59 ce 1 addr 8'h6 addr2 8'h7 60 ce 0 addr 8'h6 addr2 8'h7 61 ce 1 addr 8'h3 addr2 8'h4 62 ce 0 addr 8'h3 addr2 8'h4 63 64 //report 65 =========================================================== 66 Group : test::address_cov 67 =========================================================== 68 SCORE INSTANCES WEIGHT GOAL 69 87.50 62.50 1 100 70 71 1 Instances: 72 73 SCORE WEIGHT GOAL NAME 74 62.50 50 100 address_cov 75 ----------------------------------------------------------- 76 Summary for Group test::address_cov 77 78 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 79 Variables 16 2 14 87.50 80 81 Variables for Group test::address_cov 82 83 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 84 ADDRESS 8 1 7 87.50 100 1 85 ADDRESS2 8 1 7 87.50 100 1 86 ----------------------------------------------------------- 87 Summary for Variable ADDRESS 88 89 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 90 Automatically Generated Bins 8 1 7 87.50 91 92 Automatically Generated Bins for ADDRESS 93 94 Uncovered bins 95 96 NAME COUNT AT LEAST NUMBER 97 [auto[1]] 0 1 1 98 99 Covered bins 100 101 NAME COUNT AT LEAST 102 auto[0] 1 1 103 auto[2] 1 1 104 auto[3] 2 1 105 auto[4] 1 1 106 auto[5] 1 1 107 auto[6] 2 1 108 auto[7] 2 1 109 ----------------------------------------------------------- 110 Summary for Variable ADDRESS2 111 112 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 113 Automatically Generated Bins 8 1 7 87.50 114 115 Automatically Generated Bins for ADDRESS2 116 117 Uncovered bins 118 119 NAME COUNT AT LEAST NUMBER 120 [auto[2]] 0 1 1 121 122 Covered bins 123 124 NAME COUNT AT LEAST 125 auto[0] 2 1 126 auto[1] 1 1 127 auto[3] 1 1 128 auto[4] 2 1 129 auto[5] 1 1 130 auto[6] 1 1 131 auto[7] 2 1 132 =========================================================== 133 Group Instance : address_cov 134 =========================================================== 135 Comment: This is cool 136 SCORE WEIGHT GOAL 137 62.50 50 100 138 139 Group: 140 141 SCORE INSTANCES WEIGHT GOAL NAME 142 87.50 62.50 1 100 test::address_cov 143 ----------------------------------------------------------- 144 Summary for Group Instance address_cov 145 146 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 147 Variables 16 6 10 62.50 148 149 Variables for Group Instance address_cov 150 151 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 152 ADDRESS 8 1 7 87.50 100 1 153 ADDRESS2 8 5 3 37.50 100 1 154 ----------------------------------------------------------- 155 Summary for Variable ADDRESS 156 157 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 158 Automatically Generated Bins 8 1 7 87.50 159 160 Automatically Generated Bins for ADDRESS 161 162 Uncovered bins 163 164 NAME COUNT AT LEAST NUMBER 165 [auto[1]] 0 1 1 166 167 Covered bins 168 169 NAME COUNT AT LEAST 170 auto[0] 1 1 171 auto[2] 1 1 172 auto[3] 2 1 173 auto[4] 1 1 174 auto[5] 1 1 175 auto[6] 2 1 176 auto[7] 2 1 177 ----------------------------------------------------------- 178 Summary for Variable ADDRESS2 179 180 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 181 Automatically Generated Bins 8 5 3 37.50 182 183 Automatically Generated Bins for ADDRESS2 184 185 Uncovered bins 186 187 NAME COUNT AT LEAST NUMBER 188 [auto[2]] 0 2 1 189 auto[1] 1 2 1 190 auto[3] 1 2 1 191 auto[5] 1 2 1 192 auto[6] 1 2 1 193 194 Covered bins 195 196 NAME COUNT AT LEAST 197 auto[0] 2 2 198 auto[4] 2 2 199 auto[7] 2 2

7. Coverage methods

- void:触发covergroup的采样;

- real get_coverage():计算覆盖率,返回值为0-100;

- void set_inst_name(string):给实例设置名称;

- void start:开始收集覆盖率;

- void stop:结束书记覆盖率

1 module test(); 2 3 logic [2:0] addr; 4 wire [2:0] addr2; 5 6 assign addr2 = addr + 1; 7 8 covergroup address_cov; 9 ADDRESS : coverpoint addr { 10 option.auto_bin_max = 10; 11 } 12 ADDRESS2 : coverpoint addr2 { 13 option.auto_bin_max = 10; 14 } 15 endgroup 16 17 address_cov my_cov = new; 18 19 initial begin 20 my_cov.ADDRESS.option.at_least = 1; 21 my_cov.ADDRESS2.option.at_least = 2; 22 // start the coverage collection 23 my_cov.start(); 24 // Set the coverage group name 25 my_cov.set_inst_name("ASIC-WORLD"); 26 $monitor("addr 8'h%x addr2 8'h%x",addr,addr2); 27 repeat (10) begin 28 addr = $urandom_range(0,7); 29 // Sample the covergroup 30 my_cov.sample(); 31 #10; 32 end 33 // Stop the coverage collection 34 my_cov.stop(); 35 // Display the coverage 36 $display("Instance coverage is %e",my_cov.get_coverage()); 37 end 38 39 endmodule 40 41 //simulation 42 43 addr 8'h6 addr2 8'h7 44 addr 8'h4 addr2 8'h5 45 addr 8'h5 addr2 8'h6 46 addr 8'h2 addr2 8'h3 47 addr 8'h3 addr2 8'h4 48 addr 8'h7 addr2 8'h0 49 addr 8'h0 addr2 8'h1 50 addr 8'h7 addr2 8'h0 51 addr 8'h6 addr2 8'h7 52 addr 8'h3 addr2 8'h4 53 Instance coverage is 8.750000e+01 54 55 //report 56 =========================================================== 57 Group : test::address_cov 58 =========================================================== 59 SCORE WEIGHT GOAL 60 87.50 1 100 61 ----------------------------------------------------------- 62 Summary for Group test::address_cov 63 64 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 65 Variables 16 2 14 87.50 66 67 Variables for Group test::address_cov 68 69 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 70 ADDRESS 8 1 7 87.50 100 1 71 ADDRESS2 8 1 7 87.50 100 1 72 ----------------------------------------------------------- 73 Summary for Variable ADDRESS 74 75 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 76 Automatically Generated Bins 8 1 7 87.50 77 78 Automatically Generated Bins for ADDRESS 79 80 Uncovered bins 81 82 NAME COUNT AT LEAST NUMBER 83 [auto[1]] 0 1 1 84 85 Covered bins 86 87 NAME COUNT AT LEAST 88 auto[0] 1 1 89 auto[2] 1 1 90 auto[3] 2 1 91 auto[4] 1 1 92 auto[5] 1 1 93 auto[6] 2 1 94 auto[7] 2 1 95 ----------------------------------------------------------- 96 Summary for Variable ADDRESS2 97 98 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 99 Automatically Generated Bins 8 1 7 87.50 100 101 Automatically Generated Bins for ADDRESS2 102 103 Uncovered bins 104 105 NAME COUNT AT LEAST NUMBER 106 [auto[2]] 0 1 1 107 108 Covered bins 109 110 NAME COUNT AT LEAST 111 auto[0] 2 1 112 auto[1] 1 1 113 auto[3] 1 1 114 auto[4] 2 1 115 auto[5] 1 1 116 auto[6] 1 1 117 auto[7] 2 1

8. Coverage system task

- $set_coverage_db(name):设置覆盖率数据库的文件名;

- $load_coverage-db(name):从给定的文件名加载所有覆盖组类型的累计覆盖信息 ;

- $get_coverage();返回0-100范围内所有覆盖组类型的总体覆盖率;

1 module test(); 2 3 logic [2:0] addr; 4 wire [2:0] addr2; 5 6 assign addr2 = addr + 1; 7 8 covergroup address_cov; 9 ADDRESS : coverpoint addr { 10 option.auto_bin_max = 10; 11 } 12 ADDRESS2 : coverpoint addr2 { 13 option.auto_bin_max = 10; 14 } 15 endgroup 16 17 address_cov my_cov = new; 18 19 initial begin 20 // Set the database name 21 $set_coverage_db_name("asic_world"); 22 $monitor("addr 8'h%x addr2 8'h%x",addr,addr2); 23 repeat (10) begin 24 addr = $urandom_range(0,7); 25 my_cov.sample(); 26 #10; 27 end 28 // Get the final coverage 29 $display("Total coverage %e",$get_coverage()); 30 end 31 32 endmodule 33 34 //simulation 35 module test(); 36 37 logic [2:0] addr; 38 wire [2:0] addr2; 39 40 assign addr2 = addr + 1; 41 42 covergroup address_cov; 43 ADDRESS : coverpoint addr { 44 option.auto_bin_max = 10; 45 } 46 ADDRESS2 : coverpoint addr2 { 47 option.auto_bin_max = 10; 48 } 49 endgroup 50 51 address_cov my_cov = new; 52 53 initial begin 54 // Set the database name 55 $set_coverage_db_name("asic_world"); 56 $monitor("addr 8'h%x addr2 8'h%x",addr,addr2); 57 repeat (10) begin 58 addr = $urandom_range(0,7); 59 my_cov.sample(); 60 #10; 61 end 62 // Get the final coverage 63 $display("Total coverage %e",$get_coverage()); 64 end 65 66 endmodule 67 68 //report 69 =========================================================== 70 Group : test::address_cov 71 =========================================================== 72 SCORE WEIGHT GOAL 73 87.50 1 100 74 75 ----------------------------------------------------------- 76 Summary for Group test::address_cov 77 78 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 79 Variables 16 2 14 87.50 80 81 Variables for Group test::address_cov 82 83 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT 84 ADDRESS 8 1 7 87.50 100 1 85 ADDRESS2 8 1 7 87.50 100 1 86 ----------------------------------------------------------- 87 Summary for Variable ADDRESS 88 89 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 90 Automatically Generated Bins 8 1 7 87.50 91 92 Automatically Generated Bins for ADDRESS 93 94 Uncovered bins 95 96 NAME COUNT AT LEAST NUMBER 97 [auto[1]] 0 1 1 98 99 Covered bins 100 101 NAME COUNT AT LEAST 102 auto[0] 1 1 103 auto[2] 1 1 104 auto[3] 2 1 105 auto[4] 1 1 106 auto[5] 1 1 107 auto[6] 2 1 108 auto[7] 2 1 109 ----------------------------------------------------------- 110 Summary for Variable ADDRESS2 111 112 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 113 Automatically Generated Bins 8 1 7 87.50 114 115 Automatically Generated Bins for ADDRESS2 116 117 Uncovered bins 118 119 NAME COUNT AT LEAST NUMBER 120 [auto[2]] 0 1 1 121 122 Covered bins 123 124 NAME COUNT AT LEAST 125 auto[0] 2 1 126 auto[1] 1 1 127 auto[3] 1 1 128 auto[4] 2 1 129 auto[5] 1 1 130 auto[6] 1 1 131 auto[7] 2 1

浙公网安备 33010602011771号

浙公网安备 33010602011771号