FPGA图像处理算法—基于双线性插值的图像缩放原理

上几天狼哥介绍了基于单线性插值的双线性插值(FPGA图像处理算法—双线性插值),今天介绍一个基于双线性插值的应用,图像缩放。

图像缩放是一个非常实用且常见算法,在电脑上我们经常放大缩小图片,可是它的原理是啥呢?这个就是今天狼哥要讲的内容。

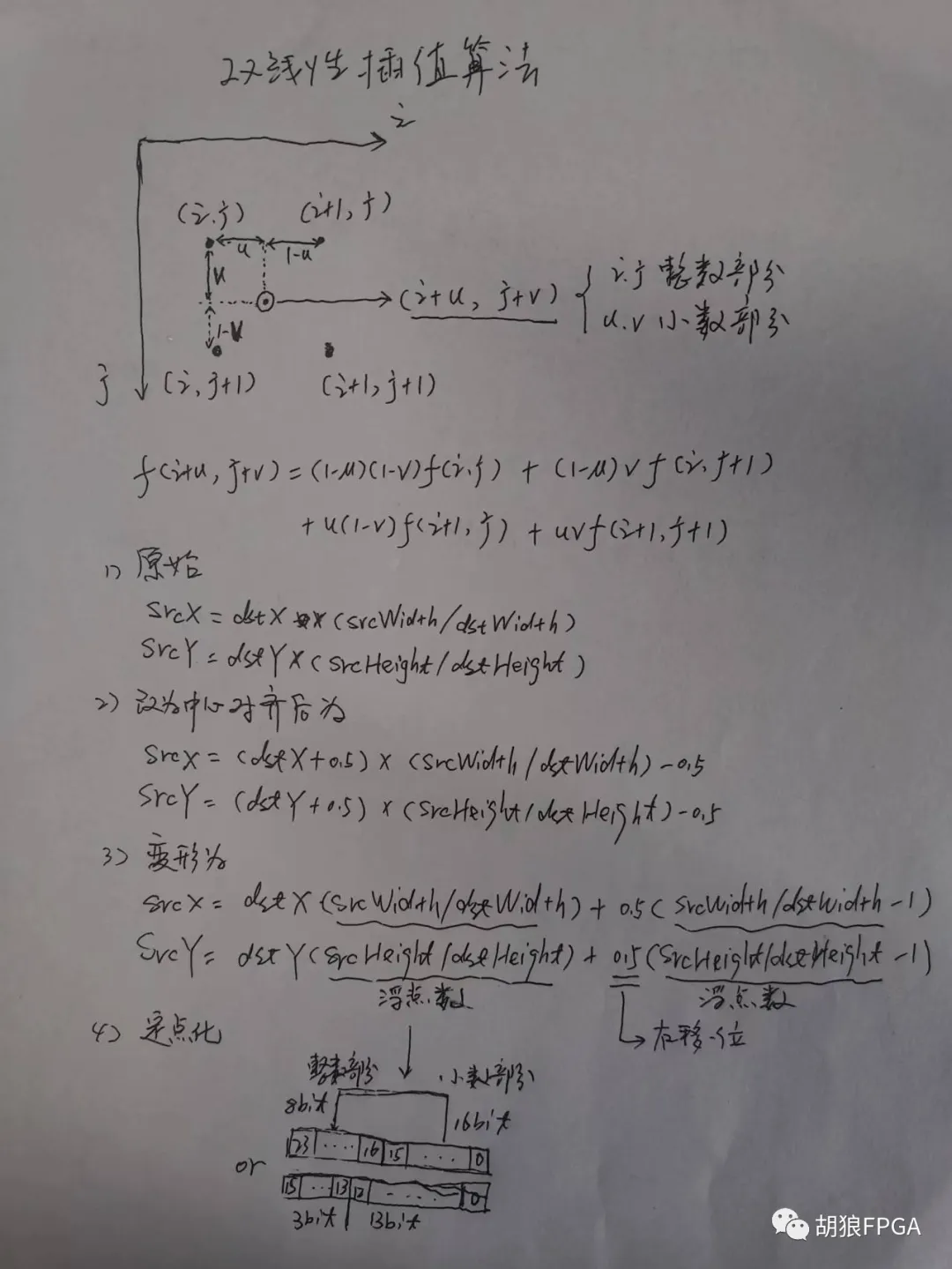

基于双线性插值的图像缩放算法原理如下图所示:

从图中可以看出,图像缩放的核心算法还是双线性插值(其他插值算法不讨论),双线性插值的具体原理参考这个链接(FPGA图像处理算法—双线性插值),缩放的核心思想就是将目标像素点的坐标反映射到原图像对应的像素坐标,也就是步骤1),这里面的dstX,dstY就是目标坐标,srcX,srcY就是原像素坐标。srcWidth/dstWidth为宽度缩放比,srcHeight/dstHeight为高度缩放比,这个是个已知数,反映射出来的坐标srcX,srcY很可能是小数,在原始图像中实际没有存在的坐标,所以在这里需要用到双线性插值,通过srcX,srcY临近的四个点,插值出这个不存在的坐标的像素值;实际上为了实现中心对齐,会对映射后的坐标做一个修正,也就是步骤2),虽然这个步骤不是非做不可;步骤3)是步骤2)的等价变化,也不是非做不可,根据实现需要选做;步骤4)是FPGA实现时必须要做的一个步骤,将浮点数定点化,方便实现。如何将浮点数定点化在FPGA图像处理入门—part4.乘法运算这篇文章的付费部分会介绍,有兴趣的可以去看看或者自己百度。

缩放的整体思路就是目标坐标反映射到原图像坐标,通过双线性插值得到目标坐标点的像数值,以此类推,遍历所有像素点,重复映射插值这个操作,完成整个图像的缩小或者放大。其中缩小和放大会有点区别,缩小本质上是会丢掉很多像素点,而放大则需要多插值出很多的像素点,但是不管是缩小还是放大,最后的像素点都是双线性插值的像素,不再是原始图像里原封不动的像数值。在FPGA实现时,缩小会比放大容易些。目前狼哥还没做具体实现,等实现了再和大家分享实现的要点和细节。

对算法感兴趣的欢迎去狼哥tb店铺胡狼FPGA咨询下单,可以获取源代码和视频讲解课程。

浙公网安备 33010602011771号

浙公网安备 33010602011771号