FPGA——RAM的使用与仿真

RAM的使用

-

嵌入式存储器结构由一列列 M9K 存储器模块组成,通过对这些 M9K 存储器模块进行配置,可以实现各种存储器功能,例如: RAM、移位寄存器、 ROM 以及 FIFO 缓冲器。

-

使用quartus的定制ip核定制一个深度为256,宽度为8位的双端口(读写)RAM存储器,并对存储器进行仿真

-

//仿真代码 `timescale 1ns/1ns `define clk_period 20 module tb_ram_2port(); reg clk; reg [7:0]data; reg [7:0]raddr; reg [7:0]waddr; reg wren; wire [7:0]q; ram_2port ram_2port ( .clock ( clk ), .data ( data), .rdaddress ( raddr ), .wraddress ( waddr ), .wren ( wren ), .q ( q ) ); initial clk = 1'b1; always#(`clk_period/2) clk = ~clk; integer i=0; initial begin data = 0; raddr = 255;//这是一个点 waddr = 0; wren = 0; #(`clk_period*10+1);//关键在这个+1上 for(i=0; i<=5; i=i+1)begin wren = 1'b0; waddr = i; data = {$random}%256; #(`clk_period); end for(i=6; i<=15; i=i+1)begin wren = 1'b1; waddr = i; data = {$random}%256; #(`clk_period); end wren = 1'b0; #200; for(i=0; i<=15; i=i+1)begin raddr = i; #(`clk_period); end #200; $stop; end endmodule -

-

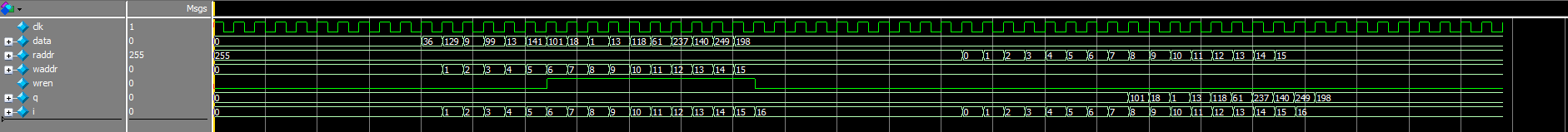

从上图可以看出,在wren为低电平时,数据是写不进去的,并且读写地址可以随机的指定

-

-

-

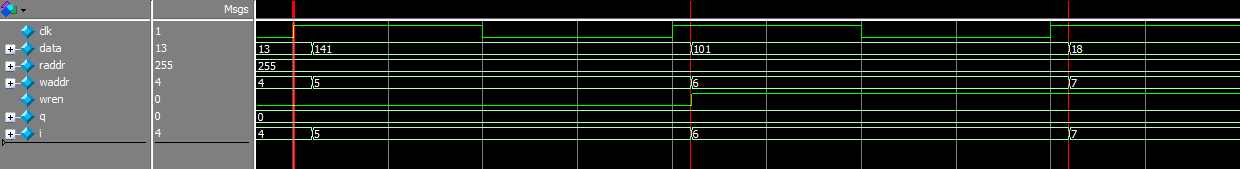

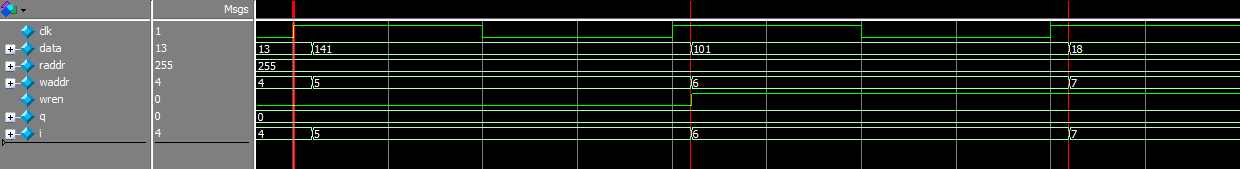

上图可以看出读地址改变后在时钟上升沿被采样,数据在采样后的下一拍时钟输出

-

对比6中的图片,wren = 0,数据是141,地址是5,在7中的图片可以看到,读取地址为5的数据读出数据为0,因为数据并没有被写入,ram中保存着初始值0

-

读地址与时钟沿错开了一点,写地址也同样向后错开一点,这是应为在仿真时

#(`clk_period*10+1);这个+1模拟的是实际情况,或者这么说,信号在传播是总是有延迟,不可能恰好在时钟沿时数据变换采样到新数据,所以需要+1

浙公网安备 33010602011771号

浙公网安备 33010602011771号