物理验证:你选哪款 DRC/LVS

“物理验证是通往 tape-out 的最后一关。”

当工艺推进至 7 nm、5 nm 乃至更先进节点,设计规则变得愈发复杂、模块层级更多、混合信号/3D 封装挑战加剧。此时, DRC (Design Rule Check) 与 LVS (Layout Versus Schematic) 这两项物理验证工作不仅是良率保障,更是与 foundry 签入流程中不可绕开的一环。选对工具,能让你少走弯路、快下 mask。

- 工具一览

Siemens Calibre

Calibre 长期以来在 DRC/LVS 领域享有“行业标准”之称。其工具套件包括 nmDRC、nmLVS 等,被大量 foundry 用作签核平台。

优点在于:签核 rule-deck 一般首先在 Calibre 上成熟、foundry 对 Calibre 的 支持最早且最广。这缩短了“为什么同样规则在不同工具表现不一致”的调试循环。

适用场景:你在领先节点(如 5 nm/3 nm)设计、且 foundry 验核 deck 基于 Calibre。

需要注意:如果你设计流程偏向“在 P&R 内部就想早验早修”,但只用 Calibre 做传统批量签核,可能会错过“在设计进行中实时反馈”的机会。

Synopsys IC Validator (ICV)

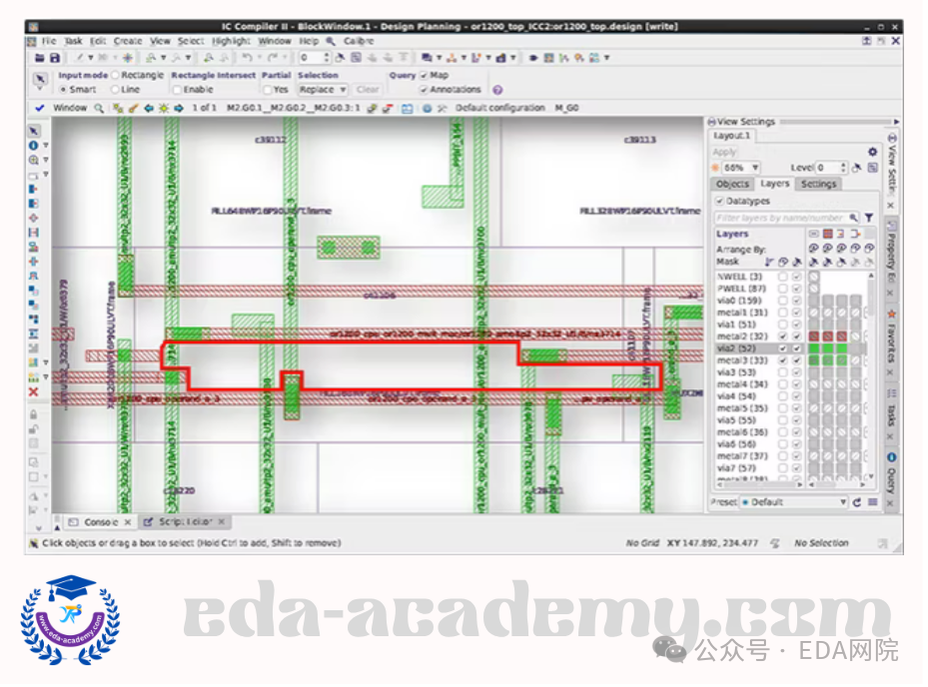

IC Validator 是 Synopsys 专注于物理验证的解决方案,其特色为与 Synopsys 的 P&R 工具(如 ICC2/Fusion)紧密集成。

优势在于:能在设计/实现阶段就进行实时或近实时的 DRC 检查(例如 Live DRC inside ICC2),避免等到最后才发现问题而返工。

适用场景:你主要用 Synopsys 的 P&R 套件,且希望将 DRC/LVS 反馈周期前置。

注意事项:若 foundry 验核 deck 本身在 Calibre 上更成熟,仍需确认规则一致性。

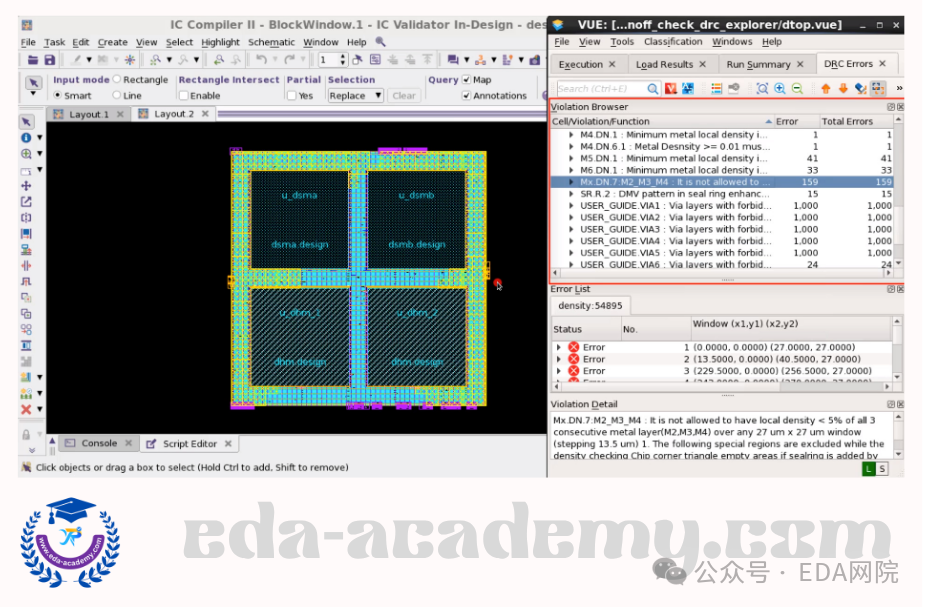

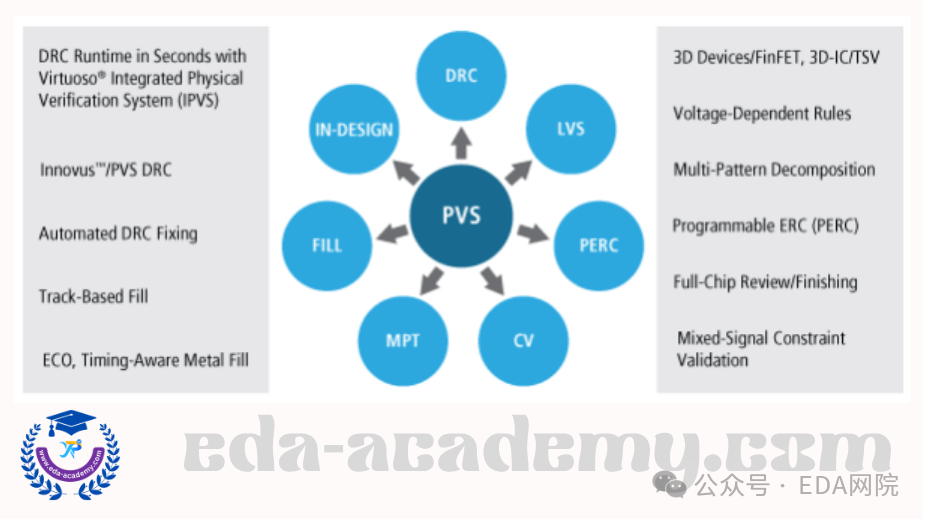

Cadence Pegasus Verification System (/ PVS)

Pegasus 是 Cadence 针对大规模 DRC 签核、高吞吐、云/并行处理优化的方案。其官方称可实现“up to 10×”对比传统工具的 DRC 加速。

优势在于:如果你的挑战是“跑满一整片 GDS 或 3D 封装设计,常常卡在 DRC 排队/跑满一夜”的情况,Pegasus 的弹性并行特性就尤为吸引。

适用场景:大型 SoC、3D IC、封装设计或多片 - 拼 场景,且你能调用云/大规模 CPU 资源。

注意事项:仍需确认 deck 兼容性、现场经验与 foundry 签核流程。

2. 选择标准 & 决策因素

选择标准 & 决策因素

Deck 成熟度与归属

工具并不是孤立存在,最关键的是 rule-deck(检验规则集)是谁写、谁维护、在哪里首先生效。

如果 foundry 本身提供基于 Calibre 的 签核 deck,那么即便你流程用别的工具,也可能因为 deck 不成熟而坑很多。

最快的 debug 循环

在设计阶段就做 DRC/LVS(如 ICV)可以显著减少后阶段返工。

在签核阶段再做(如 Calibre 或 PVS)意味着你可能已积累大量问题。

因此你需要问:我更看重“早期干净”还是“最后签核通关”?

吞吐能力 & 队列痛点

当你赶 tape-out、跑的是整片 GDS 、要在短时间内完成验证:

Pegasus 强项是大规模并行、云/爆发计算能力。

ICV 也有强分布式能力(例如支持数千 CPU 核)

Calibre 虽也有大规模选项,但在“爆发式并行+云”场景上可能略逊。

所以,若你的现实环境是“工具队列长”“跑一次要等待一天以上”,就要优先考虑并行能力。

3D/封装 & 混合信号边界

现代设计越来越不是纯数字 2D 芯片:3D IC、封装结构、混合信号块、芯片-片间互连,都让验证工具必须覆盖这些边界。

因此要确认:你的 工具是否被用来验证 die + interposer + package + BGA/LGA 等场景。

3. 实战分享要点

跑哪一节点/哪个 foundry?节点越先进、规则越复杂,工具选型越重要。

运行时间最长的原因是什么?是密度(density)、层级(hierarchy)、天线效应(antenna)、奇偶数循环(odd-cycle)?

调试/查看界面哪些帮助你省下了时间?强大的 viewer/debug UX 可以让你少卡一小时、甚至一天。

这些实际问题往往决定“选哪个工具”的最终答案。

4. 总结建议

如果你在领先节点,且 foundry deck 已在 Calibre 上成熟:优先选 Calibre。

如果你整个流程以 Synopsys 生态为主,想把验证提前到设计实现阶段:选 IC Validator。

如果你追求极致 DRC 吞吐、暴力并行、大片验证,尤其是 3D/封装场景:考虑 Pegasus。

最好结合你的 IT 资源(有无云/大规模 CPU farm)、团队经验、流程契合度,再做决定。

END

《EDA网院》出品 · 与全球工程师一起探索芯片的世界

浙公网安备 33010602011771号

浙公网安备 33010602011771号