EDA工具入门

在芯片与系统设计日益复杂的今天,电子设计自动化(EDA)工具已从“效率加速器”演进为“成败分水岭”。从原理图、仿真、版图到时序/信号/功耗全链路验证,合理的工具栈与方法论,直接决定首次流片与项目交付的把握度。本文提炼主流入门脉络,结合前沿实践,帮你用更短的时间构建更可靠的设计流。

1、为什么必须是EDA

EDA的核心价值是把“尽早发现问题”的能力前移到虚拟世界(Shift Left)。通过在原理图/布局完成前对电路、互连、封装与系统级行为建立模型、快速迭代仿真,你能在样机前验证大部分风险,显著减少返工与重转版的成本与周期。

2、一个清晰的入门路径

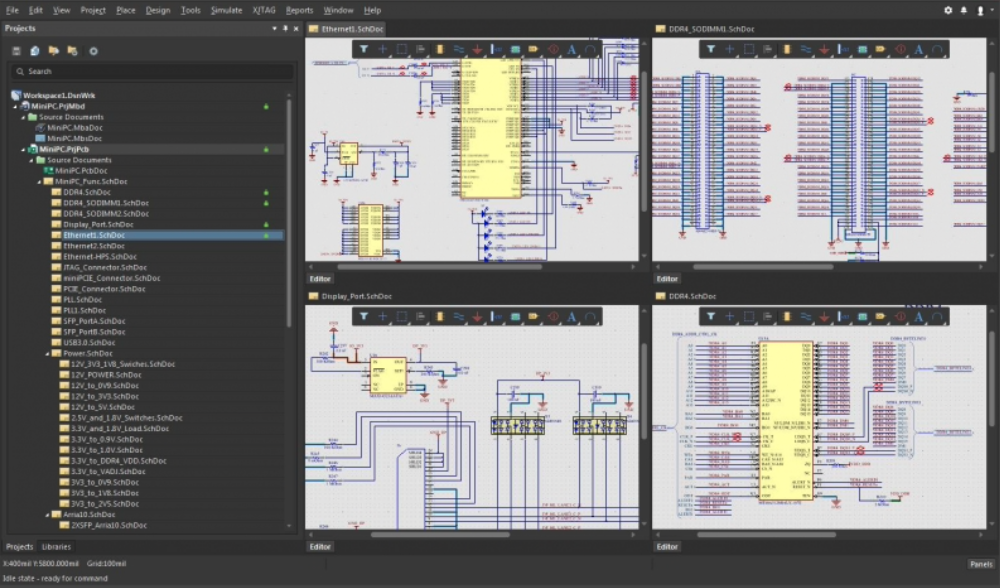

I. 设计输入与功能仿真

原理图/HDL:完成功能定义与接口约束;

电路/系统仿真:从电路级(SPICE/Ngspice)到系统级(IBIS-AMI、行为模型)验证功能与边界;

可复用IP与PDK配合:在工艺/封装约束下做早期可制造性评估。

(开源生态如 OpenROAD/Yosys/OpenLane 已能覆盖从综合到布局布线的流程,适合教学与入门评估;商业工具在大规模设计、模型准确性与标准合规检查上更成熟。)

II. 版图实现与物理验证

布局布线与DRC/LVS:在几何与拓扑层面收敛;

寄生提取与时序收敛:静态时序分析(STA)与角落/工艺漂移覆盖;

封装/PCB协同:SoC/Chiplet → 封装 → PCB 的多域联合。

III. 高速设计的三大刚需分析

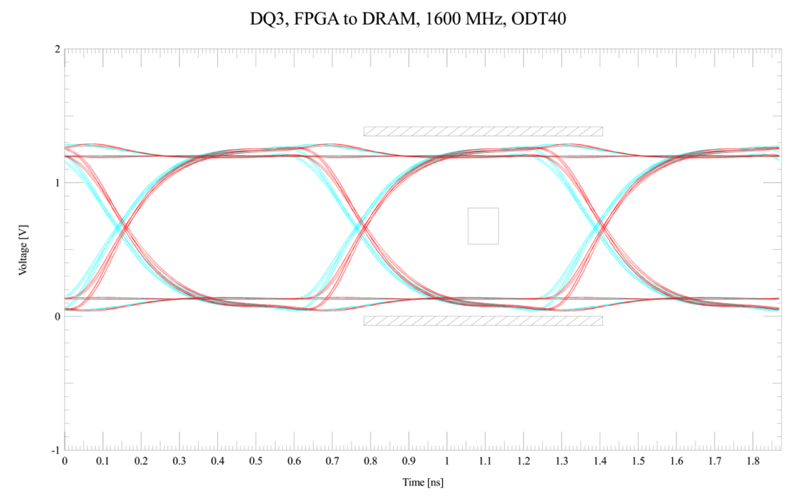

信号完整性(SI):反射、串扰、抖动与ISI;

电源完整性(PI):PDN阻抗展平、瞬态噪声与SSN;

EMI/EMC:在标准与眼图遮罩下满足辐射/传导指标。

IV. 标准一致性与系统联调

PCIe/USB/以太网/DDR等接口对眼图、抖动与面罩要求严苛,建议在仿真阶段即引入一致性检查模板,降低实验室一致性测试失败的风险。

3、新手常见痛点与破解思路

“版图像素点”到 “物理世界”:高速走线不是“拉通就行”。要基于微带/带状线模型、叠层与回流路径做受控阻抗设计,并在EM/时域联合仿真中收敛。

PDN看不见的共振:仅靠数据手册的阶跃负载测试难以暴露最坏纹波,需要阻抗/频域视角定位峰值并优化去耦网络。

“一次过标”的幻想:把一致性检查(如DDR/PCIe眼图面罩)前置到虚拟样机阶段,减少实验室屡测屡改。

4、小案例:高速接口从“能跑”到“跑稳”

在一次DDR子系统优化中,团队基于受控阻抗走线与回流路径管理完成布局,并在仿真中迭代等长/端接策略;随后用眼图模板评估抖动与开口度,最终把实验室一致性失败率降到可接受范围。这个流程的关键并不神秘:尽早建模、用正确的指标收敛、让板前验证更接近板后测试。

5、选型建议(给正要上手的你)

学习与实践并行:先用开源工具栈跑通端到端小例子,理解EDA“数据/模型/约束”的来龙去脉,再评估商业工具在规模、精度与标准库方面的价值。

重视跨域协同:IC/封装/PCB一体化的版图与联合仿真,会显著减少边界问题。

把验证当一等公民:把SI/PI/EMI、时序与一致性检查嵌入日常构建流,而不是项目末期的“补作业”。

6、学EDA,选对路径更重要

如果你希望系统、成体系地掌握以上方法论与落地技巧,EDA Academy(www.eda-academy.com) 是一个省心的入口:

覆盖最新、成体系的专业网课,既有工具实操,也有SI/PI/EMI与一致性测试的案例解析;

你可以注册为导师发布课程,把项目经验转化为影响力与收入;

用一个邮箱免费订阅Newsletter,定期获取前沿题解与实战Tips;

还可加入销售联盟计划,通过推荐课程获得20%–50%佣金。

把学习路径、实践素材与人脉网络一次整合到位,学习效率自然“向左”——更早收敛、更快见效。

学EDA不是“安装工具→点几下”的线性流程,而是“模型—约束—验证”的闭环思维。先用正确的指标做对,再用工具做快;把验证前置到虚拟世界,才是高速复杂设计里最稳的捷径。现在就到 www.eda-academy.com 制定你的学习与实战计划吧。

浙公网安备 33010602011771号

浙公网安备 33010602011771号