DFT 签核精通指南

1、DFT 签核为何至关重要?

DFT 签核确保 IC 设计满足所有测试能力(testability)要求,为制造后测试提供基础保障。通过完善的签核流程,可提前发现问题、减少 costly 迭代,提升产品质量与可靠性。

2、核心签核技术与实践经验

I. 扫描链插入与优化

意义:增强 IC 内部状态的可控性与可观测性,是高效测试的核心之一;

实践案例:某领先厂商利用 Synopsys DFT Compiler 实现扫描链的自动插入与优化,在多核处理器设计中显著提升故障覆盖与减少测试时间。

II. 内建自测(BIST)集成

意义:将测试逻辑直接嵌入芯片,支持 on-chip at-speed 测试;

实践案例:汽车电子厂商采用 Mentor Graphics Tessent,在安全关键系统中集成 BIST,显著提升时序相关故障的检测能力。

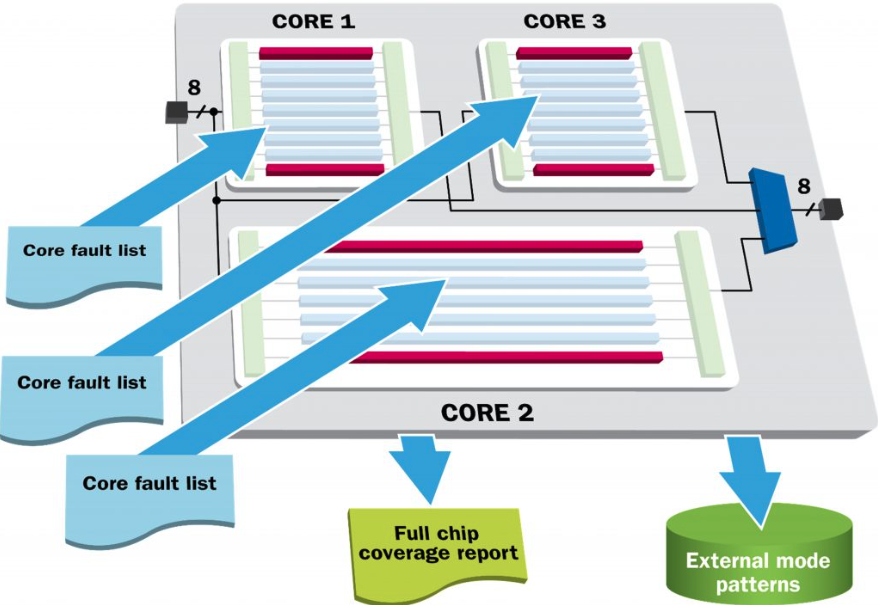

III. 层次化 DFT 签核

意义:在设计层次结构下分别验证各模块的测试能力,再整合签核,简化复杂度;

实践案例:Broadcom 团队利用 Synopsys 工具对各功能块进行签核,提升性能的一致性并降低签核复杂性。

IV. 物理感知 DFT

意义:在 DFT 插入过程中融合布局与布线约束,避免测试结构干扰物理实现;

实践案例:采用物理感知 DFT 工具,在插入扫描链与测试点时考虑布局拥塞和时序闭合,从而减少迭代次数、提升签核效率。

3、为何选择 EDA Academy 深入掌握 DFT 签核?

推荐访问 EDA Academy(www.eda-academy.com) ——这是一个专业、全面且持续更新的 IC 行业网课平台,帮助你系统学习 DFT 签核与关联技术。

在平台上,你可以获得:

覆盖扫描链优化、BIST 集成、层次化签核与物理感知 DFT 等内容的先进课程;

注册成为导师,将实战经验分享给学员并获得收益;

使用邮箱免费订阅 Newsletter,周期性获取最新课程与技术洞察;

参与销售联盟计划,通过推荐课程可赚取 20%–50% 的佣金。

浙公网安备 33010602011771号

浙公网安备 33010602011771号