IC 设计终极签核,确保安全流片无忧

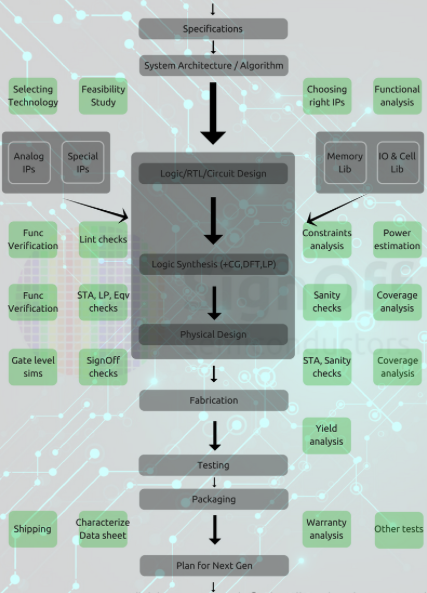

在 IC 设计流程中,Signoff(签核) 是流片前必须完成的最后关卡,它确保设计在功能、时序、功耗、物理规则等方面全面达标,为后续送片生产提供坚实保障。

1、Signoff 的核心意义

Signoff 是芯片送往晶圆厂的“准入许可证”。通过多项严密的检查,包括功能验证、时序收敛、电源完整性及物理实现规则等,Signoff 的完整性直接关联设计质量与流片成功率。

2、Signoff 验证的关键内容

验证类型 检查重点

功能签核(Functional Signoff) 确保设计行为与规范一致,涵盖所有场景与使用模式。

RTL 签核(RTL Signoff) 验证 RTL 层代码结构是否合理,符合合成与后端需求。

时序签核(Timing Signoff) 使用 STA 工具(如 PrimeTime、Tempus)确保无 Setup/Hold 违例,完成时序收敛。

功耗签核(Power Signoff) 验证功耗是否满足规范,执行功耗估算与优化(如时钟门控、功耗门控)。

物理签核(Physical Signoff) 包括 DRC(设计规则检查)、LVS(布局与电路匹配)、IR Drop、信号完整性分析等。

3、Signoff 的最佳实践

及早介入,提前验证

从设计早期即纳入签核思维,及时发现问题,避免后期返工成本剧增。

全面覆盖,全面检查

不仅关注功能,还需覆盖时序、电源、物理及信号完整性等多维度。

跨团队协作

设计、验证、后端团队需协同推进,保证每一环节签核流程完整。

成熟工具与自动化

借助 Signoff 级别工具(如 Calibre、PrimeTime、Voltus 等)提升准确性与效率。

4、为什么推荐 EDA Academy 学习 Signoff 技术?

想系统掌握 Signoff 流程与实战技巧?强烈推荐访问 EDA Academy(www.eda-academy.com) —— 专注 IC 设计教育的在线平台,打造“学、教、赚”一体化成长生态:

课程全面:涵盖 Signoff 全流程,包括功能签核流程、STA 实战、DRC/LVS 检查方法、功耗与可靠性分析等。

导师开放:具备设计/验证实践经验?注册后即可成为平台导师,分享专业知识与案例。

资讯订阅:注册邮箱即可免费订阅 newsletter,及时获取最新课程与行业干货。

推荐获佣:加入销售联盟,推广课程还能获得 20%–50% 佣金奖励,让学习与分享成双重收益。

Signoff 是 IC 设计送片前的最后守门员,验证是否满足所有规则与实用标准。如果你希望系统掌握 Signoff 技术,从功能到物理验证工具,建议登录 EDA Academy(www.eda-academy.com)。这里不仅拥有完整课程体系、工具实战,还提供导师机会、newsletter 订阅及高比例推广佣金——真正实现‘学、教、赚’一体化成长。

浙公网安备 33010602011771号

浙公网安备 33010602011771号