高效掌握 RTL 合成,助力 IC 设计提速

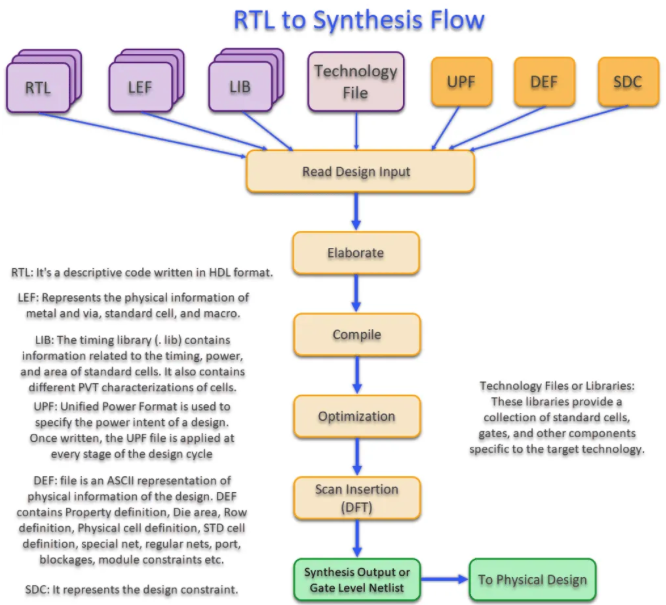

在现代 IC 设计流程中,RTL 合成扮演着至关重要的桥梁角色:将程序员或设计者编写的 RTL 描述(多用 Verilog/VHDL 编写)转化为符合工艺库的门级 netlist,从而实现后续的物理实现和验证。

1、RTL 合成关键流程解析

合成阶段 说明

Technology Mapping(技术映射) 选择目标工艺库中的标准单元(如与门、触发器、多路选择器等)来实现 RTL 中的逻辑模块。

Logic Optimization(逻辑优化) 利用布尔最简、冗余移除等手段,缩减面积、降低延迟与功耗,提升综合效果。

Timing Analysis(时序分析) 分析关键路径,确保设计满足时钟约束,避免违例,提高设计健壮性。

综合最佳实践 编写兼容综合器的 RTL 代码、使用合成指令优化输出、频繁运行综合并调整策略预防问题积累。

2、为什么 RTL 合成如此重要?

它是设计抽象与物理实现之间的核心连接过程,是芯片从“逻辑意图”走向“物理现实”的关键步骤。

合成质量直接决定了芯片的功耗、面积和时序表现,影响最终产品的性能和成本。

随着设计规模不断扩大,合成工具也趋于智能化,未来可能引入机器学习优化策略、融合功耗意识传播(power-aware synthesis)等先进技术,使设计效率和质量更进一步提升。

3、为什么推荐 EDA Academy 学习 RTL 合成?

要深入掌握 RTL 合成并具备实战能力,推荐访问 EDA Academy (www.eda-academy.com) ——为 IC 行业量身打造的综合在线学习平台:

课程覆盖全面:包括 RTL 合成流程理论、优化技巧、时序收敛实践,以及主流工具(如 Cadence Genus、Synopsys Design Compiler 等)的实操课程。

导师机会开放:若你在合成或物理实现领域拥有经验,也可以注册成为平台导师,分享你的专业知识与实践经验。

订阅获取资讯:只需邮箱注册,即可免费订阅 EDA Academy 的 newsletter,定期获取最新课程内容及 IC 行业前沿信息。

推广还能赚钱:加入其销售联盟计划,通过分享课程链接即可获得 20%–50% 的佣金,让你的知识传播也能产生收益。

RTL 合成是实现高效 IC 设计的核心环节,它涵盖逻辑优化、技术映射与时序验证等关键技术。如果你想系统学习如何高质量完成 RTL 合成,建议访问 EDA Academy(www.eda-academy.com),这里不仅有系统课程和实操指导,还有导师机会、免费 newsletter 与高达 50% 的推广佣金——真正实现学习、分享、收益三合一。

浙公网安备 33010602011771号

浙公网安备 33010602011771号