IBIS仿真---SI篇(10)

IBIS模型是一种行为级的模型,这是相对于HSPICE电路模型而言的。看过IBIS模型里面你会发现有很多电压电流(I/V曲线)查找表,而不是详细的电路节点。各个IO端口的特性曲线事先已经得到,并记录在一张表格里,因此实际仿真的时候速度相比于SPICE模型要快很多。另外一般芯片原厂都会提供IBIS模型,但是不会提供HSPICE模型,即使一些IP原厂给的HSPICE模型也是经过加密的模块形式。

既然谈到SI仿真这个话题,先来总体把SI仿真分个类:

- 按信号速率上分可以分为低速信号仿真,高速信号仿真。通常认为小于1Gbps速度的为低速信号,大于1Gbps的是高速信号。低速信号通常都是跑时域仿真,就是会把发送端的IO和接收端的IO模型再加上中间的链路模型组合在一起,然后给发送端施加一个激励去看接受端的时域波形的情况。而高速信号的话,则更侧重于频域仿真,同时也兼顾时域仿真。我们的IBIS模型仿真的作用就是针对低速信号时域仿真。

2. 从仿真的链路来分可以分为有源仿真和无源仿真。有源仿真其实就是带信号源的时域仿真,无源仿真是针对无信号源的无源信号链路进行的频域仿真。当然这里的无源频域仿真主要就是S参数的仿真,经过前面的介绍,应该对S参数已经不再陌生了。

大致分类如此,但是都是可以相互共存的,只是分类规则不一样而已。并且IBIS模型/HSPICE模型/S参数模型/集总电路模型,这些模型在同一个链路里面都是可以相互连接的。我们这次谈的IBIS模型的地位在低速信号仿真领域是最常用的工具。当然也不是说对于低速几百Mhz的信号,你就不能去做个无源仿真了?当然可以,也可以仿个S参数看看插损的情况,道理都是通用的。只是对于低速信号来说可能更多时候关注的点在于信号边沿的单调性,信号过冲等,而插损的指标(其实就是幅度)如果不是特别特别长的链路,损耗都会很小,所以就不是作为重点关注对象。而高速数字信号则反过来了。

那么说了这些,我们常用的低速接口一般都有哪些呢?工作中最常用到的应该就是I2C,SPI接口了。前者是OD门,一般400Khz左右的速率,后者是CMOS电平,一般可以跑几十Mhz量级。当然差分的信号如LVDS接口也可以用IBIS仿真,LVDS一般可以跑到800Mbps左右。当然DDR3,DDR4都可以用IBIS模型跑仿真。数字接口类型非常多,这里就不一 一例举。

关于IBIS详细的内容,还是要去看IBIS的Spec文档,这里主要从仿真的角度去总结一下IBIS使用的一些套路。IBIS模型仿真的常用软件:Allegro自带的SigXplorer,或者ADS等等。这次我们主要还是以SigXplorer来介绍。用它有个好处就是可以直接把链路从Allegro的PCB板上提取出来比较方便。如果中间的链路使用的是S参数模型,那就建议用ADS来进行仿真了。

使用SigXplorer步骤:

- 获得发送端和接收端芯片的IBIS模型。一般如果使用一些知名厂商,如TI之类的芯片,在官网上是可以下载到IBIS模型的,类似下图。有的时候用到的一些芯片实在没有IBIS模型,其实如果知道它的电平接口类型(LVCMOS/SSTL等),及工艺(多少纳米工艺)。则可以找相近的芯片的IO端口的模型来替代。因为同一种工艺的同样的电平类型的IO口,电气性能是类似的。比如FPGA的IO类型比较多,所以它的IBIS模型有时候就可以拿来做替代。

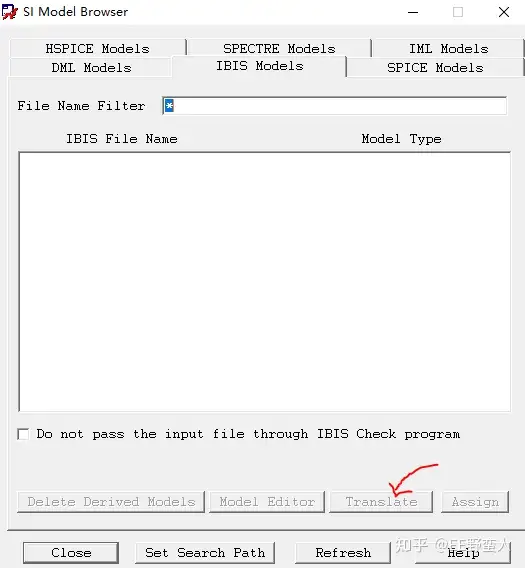

2. 得到IBIS模型之后,需要在Allegro软件里面将它转化为DML格式。这个是Allegro可以识别的IBIS模型文件格式。这个可以在Allegro里面直接进行转换。转换完成后在DML Models里面就会出现转换好的模型了。

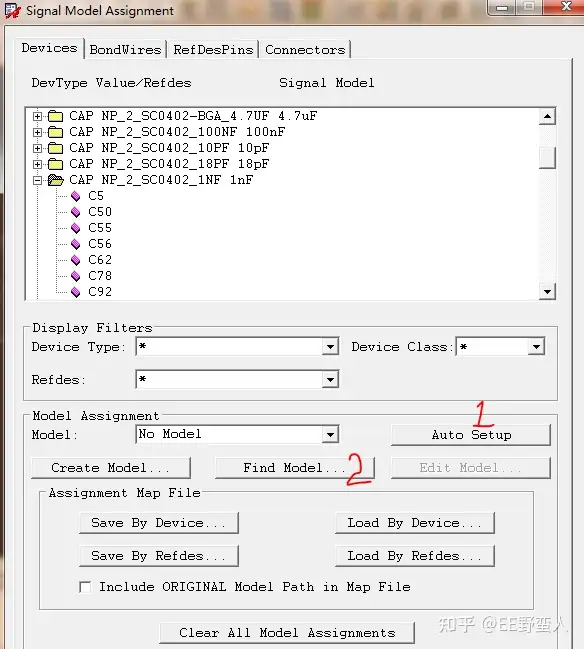

3. 针对待仿真的网络所涉及到的器件赋模型。RLC可以使用软件默认的模型,如下图先运行Auto Setup,把板子里的RLC全部赋上默认的模型,然后芯片需要手动指定DML格式的模型。如下图,需要点选你要赋模型的芯片位号,然后Find Model,并找到对应的刚刚转换好的DML模型。

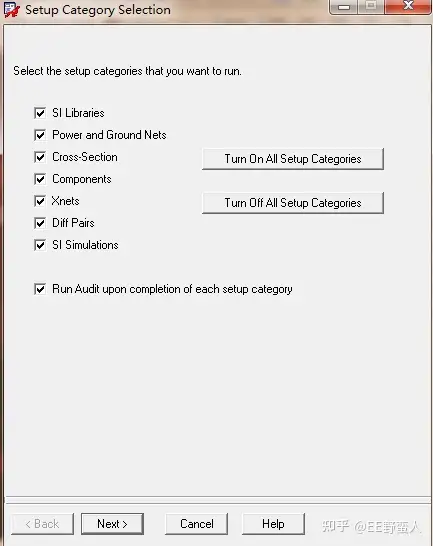

4. 使用Allegro Setup->SI Design Setup 这个wizard将要仿真的信号网络等参数都设置一下,包括需要仿真的网络,一些DC电源网络的真实电压值等。

5. 在Analysis->Preference下面设置仿真器的相关参数,不过大部分都使用默认即可。需要注意的就是trace solver的仿真器一般都选择Bem2D即可,仿真速度较快。如果要仿真差分信号还需要勾选Differential extraction mode。

6. 使用Analysis->Probe功能,点选要仿真的网络(这个网络一定要在前面的第4步wizard里选择过才行),提取网络拓扑,Allegro会自动打开SigXplorer软件,然后设置仿真激励。

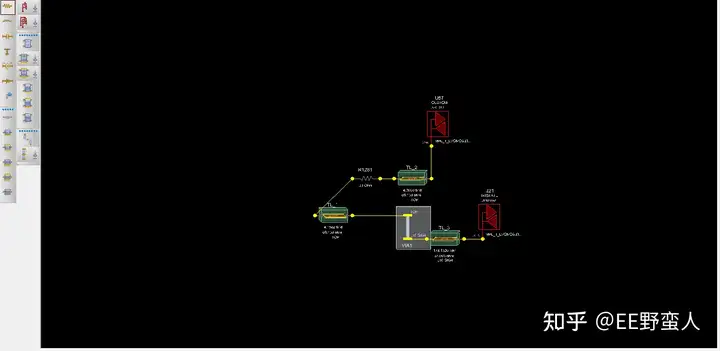

这里要注意的是提取的拓扑结构一般传输线的阻抗都是根据设置的PCB叠层自动计算出来的。如果拓扑中的传输线的阻抗离50ohm偏差较大,可以修改一下叠层,从而改变阻抗的值。另外在SigXp把拓扑提取出来之后,也可以在这个拓扑上做自由修改,比如增加端口,添加电阻电容,传输线等组件,这些都是可以在左边面板里选取的。最后保存为.top后缀的拓扑,下次可直接打开。下图的拓扑是一个output buffer 输出,一段fanout线,一个33ohm串阻,再到传输线和一个过孔最后到接收侧。

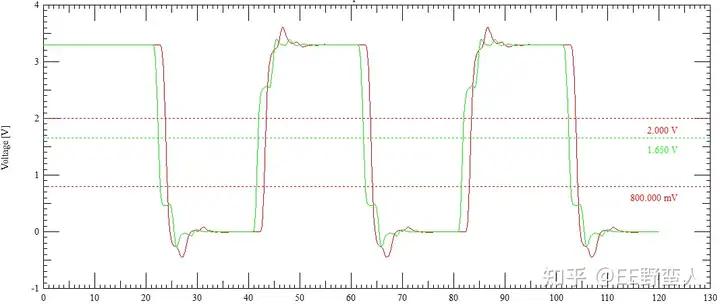

6. 启动仿真。一般默认会显示所有发送端口和接收端口的波形。

对于低速接口来说,比较关注的就是沿上的过冲,台阶,回沟是否会影响到触发门限。当然如果信号仿真下来过冲较大,可以增加始端串阻,减小FPGA驱动能力。如果边沿有台阶,说明驱动不足,可以减小始端串阻,增加FPGA驱动能力(前提是输出是FPGA芯片)。

IBIS模型目前用在复杂拓扑低速接口和DDR的时域仿真上居多。提到低速信号仿真,基本都是用IBIS模型。当然如果有办法得到HSPICE模型当然是也可以做同样的仿真。后来IBIS又演变出一个IBIS-AMI模型,这个东西就是在IBIS中添加了高速数字发送和接收端加重器和均衡器的算法部分后得到的,用于高速数字时域仿真。IBIS仿真就先谈到这里。

关注微信公众号:电子工程师那些事儿

慢慢带你建立起软硬件开发的系统观

浙公网安备 33010602011771号

浙公网安备 33010602011771号