verilog实现开方运算/基于迭代法的平方根计算算法/FPGA实现开根号算法

因老师要我们用verilog实现一个算法,涉及到开根号运算,正好学习一下算法,记录一下我的学习记录

主要算法:

要求:

输入信号:input signed [15:0] a, //数据a

输入信号:input signed [15:0] b, //数据b

输入信号:input [15:0] n, //数据个数

输入信号:valid, //数据有效

输出信号:output [15:0] result_int, //输出结果整数部分

输出信号:output [15:0] result_dec, //输出结果小数部分

输入信号a,b为有符号数。

要求算法结果保留到小数点后三位。

1. 引言

- 背景与动机: 平方根计算在硬件中的重要性,如在图像处理、信号处理、数字滤波器等领域的应用。

- 设计目标: 实现一个高效的硬件平方根计算器,采用迭代法(如牛顿迭代法)来进行计算。

- 文章结构: 概述文章结构,明确每一部分的内容,告诉读者你将从算法原理、硬件设计实现、性能分析等方面进行讨论。

2. 开发工具

开发平台:vivado

仿真平台:modelsim

3. 平方根计算的基本原理

3.1 平方根的定义

平方根是指一个数的平方等于给定数。例如,平方根计算问题可以表述为:给定一个非负数 SS,找到一个数 xx,使得 x2=Sx2=S。

3.2 牛顿迭代法

牛顿迭代法是一种常用的逼近函数根的方法,在求解平方根问题时具有广泛应用。牛顿迭代法用于平方根的计算公式如下:

Xn+1=1/2(Xn+S/Xn)

其中:

- S 是我们要求平方根的数;

- Xn 是第 n 次迭代的近似值;

- Xn+1 是下一个迭代的近似值。

这个公式表示:通过当前的近似值 Xn 和 S,我们可以得到一个新的更接近的平方根值 Xn+1。

3.3 迭代法的优点

牛顿迭代法具有以下优点:

- 快速收敛: 牛顿法的收敛速度非常快,通常经过几次迭代即可获得很高的精度;

- 实现简单: 只需要基本的加法、除法和位移操作,适合在硬件中实现。

4. verilog实现

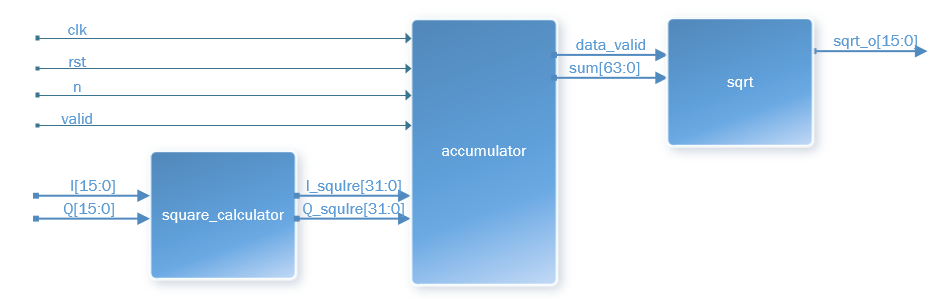

总体设计框架

4.1 square_calculator模块

此模块主要是来判断输入数据正负,并对其进行平方,使用的是组合逻辑,所以并不需要时钟输入

代码设计:

4.2 accumulator模块

此模块主要用来计算根号内容,并输出对应的valid信号,但是为了满足精确到小数点后三位,需要把输入数据乘上1000_000,然后再开完根号之后再除以1000即可得到小数部分和整数部分。

部分代码设计:

4.3 sqrt模块

此模块主要根据上个模块输出的数据和valid来进行开根号运算,并且分离出来整数部分和小数部分

部分代码设计:

5. 仿真验证

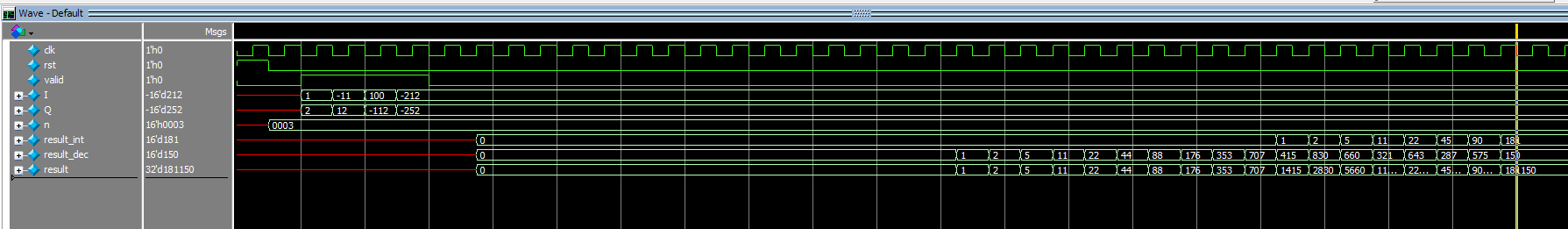

编写仿真文件tb_sqrt_mean_calculator

5.1 理论值

首先先拿计算器运算一下,模拟数据

可以看出来,根据公式算出来为181.150,

5.2 实际值

接下来我们打开modelsim仿真看一下,得出的结果和计算值是否一致

由仿真结果可得,结果和计算值一样

制作不易,记得三连哦,给我动力,持续更新!!!

浙公网安备 33010602011771号

浙公网安备 33010602011771号