每日一摘:AHB总线

一、AHB总线简介

AHB总线是ARM公司提出的,是AMBA总线的一种,被大多数SOC设计采用。AHB总线规范规定了AHB(Advanced High-performance Bus)、ASB(Advanced System Bus)、APB(Advanced Peripheral Bus)。AHB用于高性能、高时钟频率的系统结构,典型的应用:ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。APB用于连接外部设备,对性能要求不高。而考虑低功耗问题,ASB是AHB的一种替代方案。

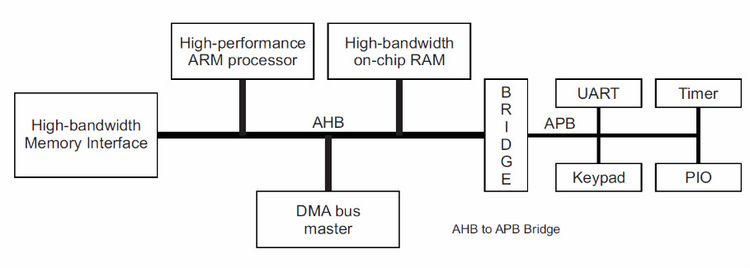

1、AHB总线架构

AHB总线的强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线master、各种拥有AHB接口的控制器等等连接起来构成一个独立的完整的SOC系统。除此之外,AHB还可以通过AHB-APB桥来连接APB总线系统,这样AHB可以成为一个完整独立的SOC芯片的骨架。典型AHB系统总线的结构图:

2、AHB总线基本特性

- burst传输

- split事务处理

- 单周期master移交

- 单一时钟沿操作

- 无三态

- 更宽的数据总线配置(64/128)

- 流水线操作

- 可支持多个总线主设备(最多16个)

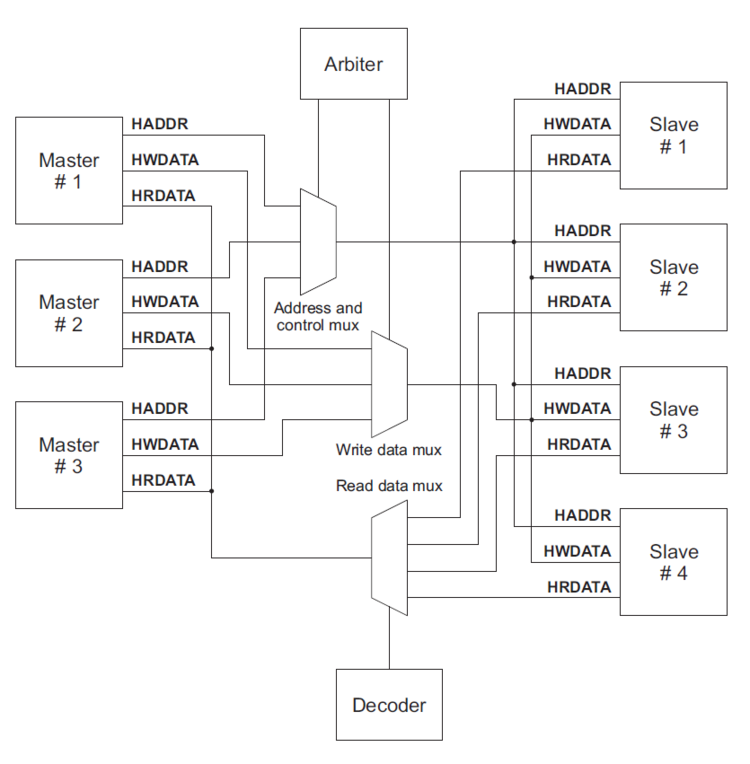

二、AHB总线组成

AHB总线组成:Master、Slave和Infrastructure。其中Infrastructure由arbiter、数据多路、地址控制多路、译码器构成。

- 主设备master

发起一次读/写操作

某一时刻只允许一个主设备使用总线

- 从设备slave

响应一次读/写操作

通过地址映射来选择使用哪一个从设备

- 仲裁器arbiter

允许某一个主设备控制总线

- 译码器decoder

通过地址译码决定选择哪一个从设备

- 总线可以分为三组

写数据总线(HWDATA)

读数据总线(HRDATA)

地址控制总线(HADDR)

三、AHB总线信号描述

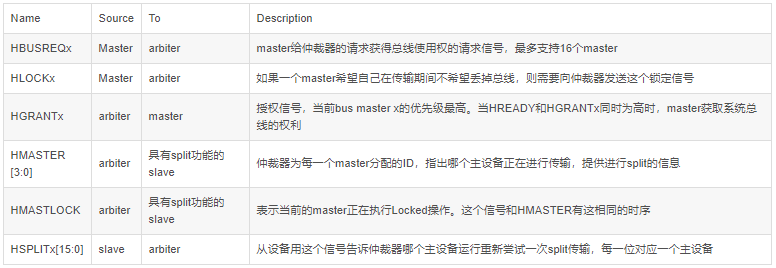

AHB仲裁信号

四、AHB总线操作

有需要占用总线的master向arbiter发出请求,arbiter授权给指定的master。任一时间周期只有一个master可以接入总线,对其指定的slave进行读写操作。

获得授权的总线开始AHB传输,首先发出地址和控制信号,提出地址信息、传输方向、带宽和burst类型。总线统一规划slave的地址,译码器根据地址和控制信号确定哪个slave与master进行数据通信。数据传输通过数据总线完成。为避免出现三态总线,AHB将读写总线分开,写数据总线用于从master到slave的数据传输,读数据总线用于从slave到master的数据传输。每笔传输包括一个地址和控制周期,一个或多个数据周期。地址和控制周期不能被扩展,因此slave必须在一个周期内采样地址信号。数据周期可以通过HREADY信号扩展,但HREADY为低时给传输加入一个等待状态以使slave获得额外的时间来提供或采样数据,另外slave通过响应信号HRESP反映传输状态。

一般情况下master完成完整的burst传输,arbiter才会授权给其他的master接入总线,然而为避免过大的判决延迟,arbiter也可能打断burst传输。在这种情况下master必须再次接入总线以进行中断的burst剩余部分的传输。

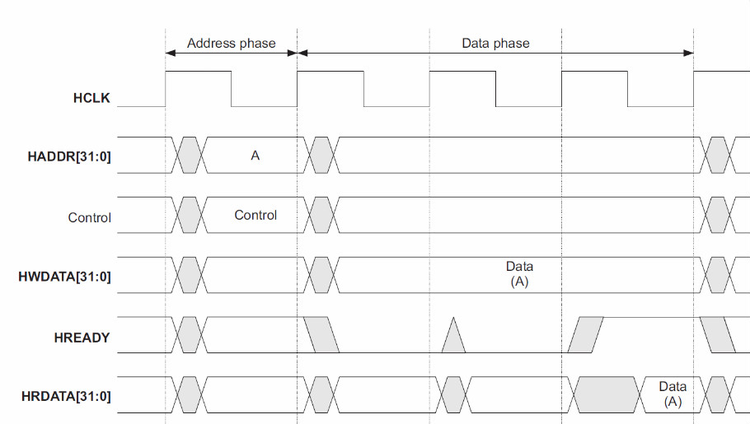

五、AHB总线基本传输

一笔传输由如下两部分组成:

地址阶段:一个周期

数据阶段:一个或多个周期,由Hburst信号决定需要几个有效周期,可以由Hready发出请求延长一个周期。

1、没有等待状态的single transfer

第一个周期的上升沿,master驱动地址和控制信号;

第二个周期的上升沿,slave采样地址和控制信号,并将HREADY拉高;

如果是写操作,master会在第二个周期的上升沿传输要写入的数据;

如果是读操作,slave会在HREADY信号拉高后将读取的数据写入总线;

第三个周期的上升沿,

如果是写操作,master获取HREADY高信号,表明slave已成功接收数据,操作成功;

如果是读操作,master获取HREADY高信号,表明此时的读数据有效并且接收下来,操作成功。

需要注意,HREADY信号在数据有效期间必须为高,并且延续到第三个周期的上升沿之后,确保master的正确采样。

2、slave插入等待状态的single transfer

slave可以及时处理master请求,但也可能存在slave太慢不能立即处理的情况。这时需要让master稍微等一等,需要slave插入一些等待的状态。如下图所示,HREADY信号在第二和第三周期拉低,意在告诉master,slave不能立即处理,需要master等待2个周期。在这里需要注意2点:

如果是写操作,master需要在等待期间保持写数据不变,直到本次传输完成;

如果是读操作,slave不需要一开始就给出数据,仅当HREADY拉高后才给出有效数据。

3、多个single transfer的pipeline操作

扩展数据周期的一个负效应是必需延长相应的下一笔传输的地址周期。A和C为零等待传输,B加入了一个等待周期,因此相应的C地址周期要进行扩展。

第一个周期,master发起一个操作A,并驱动地址和控制信号;

第二个周期,slave收到了来自总线的请求,将HREADY信号拉高;

第二个周期上升沿后,master发现有操作B需要执行,并且检查到上一周期的HREADY为高,则发起第二个操作B;

第三个周期,master获取HREADY信号为高,表示操作A已经完成;

第三个周期上升沿后,master发现有操作C需要执行,并且检查到上一周期的HREADY为高,则发起第三个操作C;

第三个周期上升沿后,slave由于繁忙插入了一个等待状态,将HREADY拉低;

第四个周期,master获取HREADY信号为低,知道slave希望等待,于是master保持和上一拍一样的信号;

第四个周期,slave处理完了事务,将HREADY信号拉高,表示可以继续处理;

第五个周期,master获取HREADY信号为高,知道slave已经可以处理B操作;

第五个周期上升沿后,B操作完成;

第六个周期上升沿后,C操作完成。

需要注意几点:

HREADY在一定程度上表示了slave的pipeline能力,在AHB中是2个pipe,也就是总线上最多存在2个未处理完的transfer。只有当总线上未完成的transfer少于2个时,master才能发起操作。

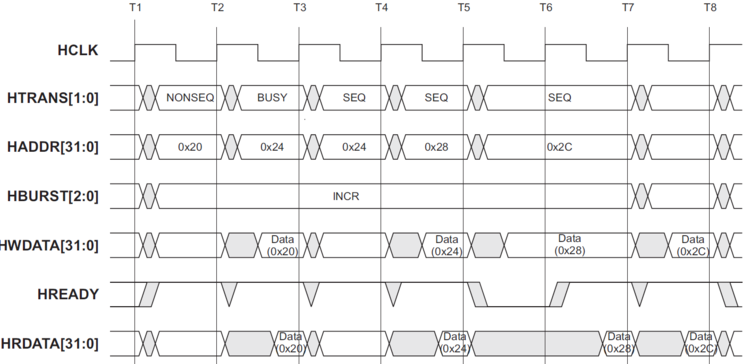

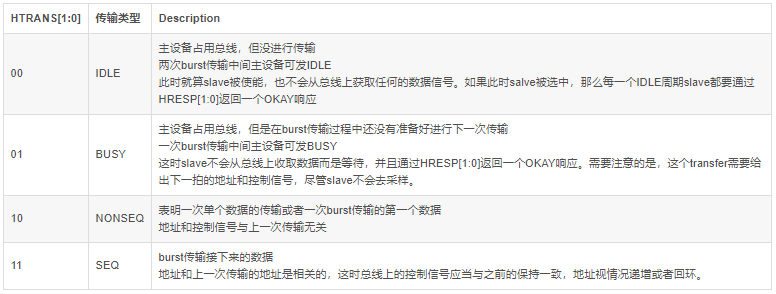

4、递增burst

T1,master传入地址和控制信号,因为是新的burst开始,transfer的类型是NONSEQ;

T2,由于master不能在第二个周期里处理第二拍,所以master使用BUSY transfer来为自己延长一个周期的时间。注意,虽然是延长了一个周期,但是master需要给出第二个transfer的地址和控制信号;

T3,slave采集到了master发来的BUSY,知道master需要等待一拍,所以slave会忽略这个BUSY transfer;

T3,master发起了第二个transfer,因为是同一个burst的第二个transfer,所以transfer的类型是SEQ;

T5,slave将HREADY信号拉低,告诉master需要等待一个周期;

T8时刻完成最后一个transfer。

需要注意的 虽然slave会忽略掉BUSY transfer,但是master也需要给出下一拍的地址和控制信号。

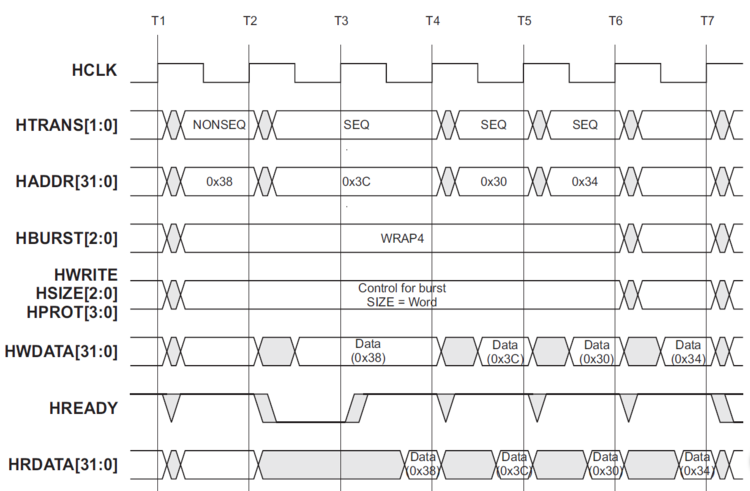

5、wrapping 4-beat burst

跟之前唯一的区别在于地址的不同,在0x3C地址之后,根据回环的地址边界,第三拍的地址变为0x30。一共四拍,4个地址,每个地址各不相同,这四个地址是一个回环范围。起始地址决定了回环操作的回环范围。

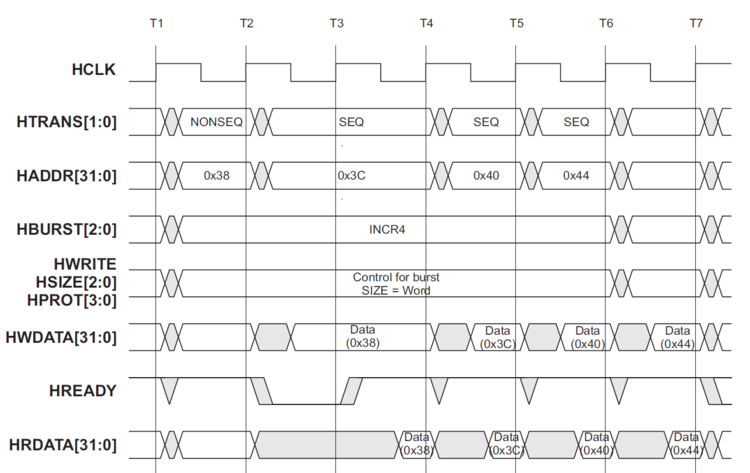

6、递增4拍burst

和上面的基本一致,只不过地址在0x30并不回环,而是递增。

六、AHB总线控制信号

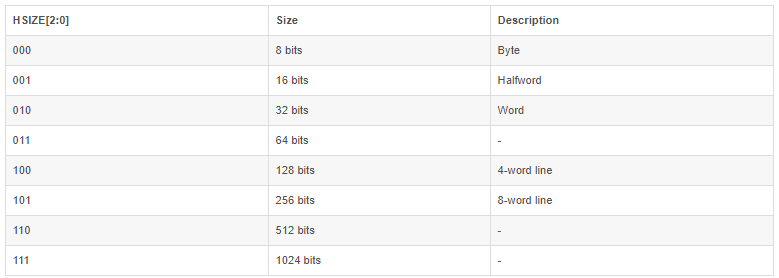

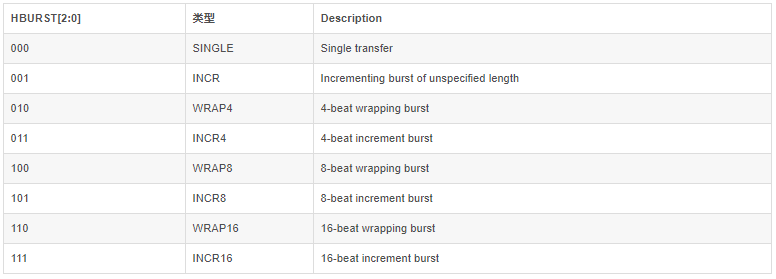

- Burst传输类型

burst不能超过1K地址边界

- 响应信号

master发起一笔传输后,slave可以决定这笔传输的进程,而master不能取消已经发出的传输。slave通过HREADY信号反映传输是否完成,通过HRESP[1:0]反映传输的状态。

slave可以如下方式完成一笔传输:

- 立即完成一笔传输

- 延迟一个或几个周期完成传输

- 传输失败返回error

- 延迟传输,释放总线

- 传输完成Hready

为高时传输完成,为低时传输需要延迟。

传输响应HRESP[1:0]

00: OKAY

01: ERROR

10: RETRY

传输未完成,请求主设备重新开始一个传输,arbiter会继续使用通常的优先级

11: SPLIT

传输未完成,请求主设备分离一次传输,arbiter会调整优先级方案以便其他请求总线的主设备可以访问总线

- 地址译码

地址译码器用于为总线上每个slave提供选择信号HSELx,选择信号是通过组合逻辑对地址码译码产生的。只有当前的数据传输完成后(HREADY为高),slave才会采样地址和控制信号以及HSELx。在一定条件下可能会出现这样的情况:产生HSELx信号而HREADY为低,在当前传输后slave会改变。

每个slave最小的地址空间为1KB,所有的master的burst传输上限也是1KB,如此设计保证了不会出现地址越界问题。当一个设计不会用到所有的地址空间时,可能出现访问到一个不存在的地址的情况,这就需要增加一个附加的默认slave来为上面的情况提供一个响应。当SEQ或NONSEQ传输访问到一个不存在的地址,默认slave应该提供ERROR响应;当IDLE或BUSY传输访问到一个不存在的地址,默认slave会响应OKAY。地址译码器会带有实现默认slave的功能。

- 仲裁

仲裁机制保证了任意时刻只有一个master可以接入总线。arbiter决定哪个发出接入请求的master可以接入总线,这通过优先级算法实现。AHB规范并没有给出优先级算法,设计者需要根据具体的系统要求定义。一般情况下arbiter不会中断一个burst传输,将总线接入权让给其他master。当然未定义长度的burst传输是可以打断的,这要看优先级算法是如何规定的。如果一笔burst被打断,master再度获得接入权限时,会传递剩余的部分。如一笔长度为INCR8的传输在传递3 beat后被打断,master再次获得接入授权后,会继续传输剩余的5 beat,剩余部分可以由一个SINGLE和一个INCR4组成,或者一个INCR。

HBUSREQx:master向arbiter发出接入请求的信号。

HLOCKx:指示是否要进行不可中断的传输,这一信号与HBUSREQx同时由master向arbiter发出。

HGRANTx:arbiter产生指示master获得授权,当HGRANTx信号为高同时HREADY为高时,master可以向总线传输地址信号。

HMASTER[3:0]:arbiter产生指示哪个master获得授权,这一信号用于地址控制多路来选择哪个master接入总线。

HMASTERLOCK:arbiter产生指示当前传输是否为锁定序列传输。

HSPLIT:供支持SPLIT传输使用。

浙公网安备 33010602011771号

浙公网安备 33010602011771号