SDRAM--Verilog及仿真(4)

(4)从SDRAM读出数据。跟写原理一致。

前几个以及这个博文都用到的命令解释!

代码设计就不帖了。

仿真结果:

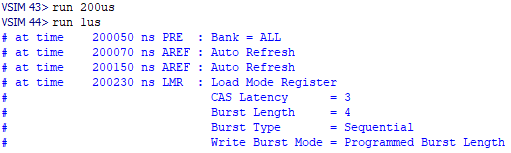

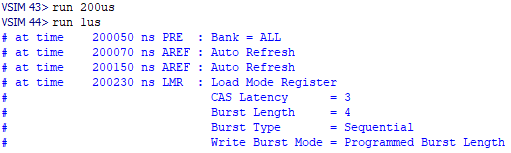

开始初始化:

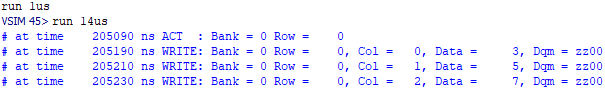

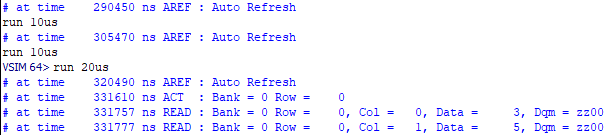

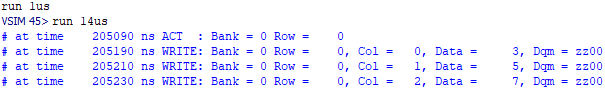

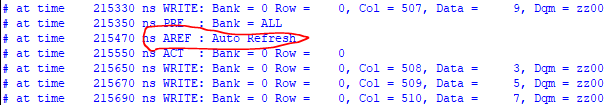

初始化之后就开始写数据,并且满足15us的时间间隔,还会暂停写,跑去刷新,然后继续再写。

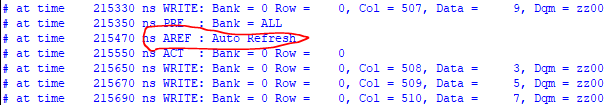

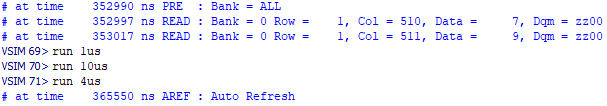

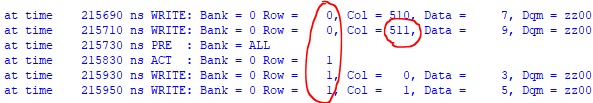

写完512个数据换第二行写

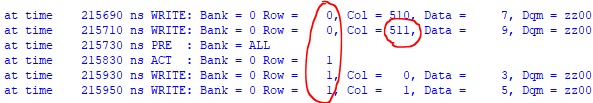

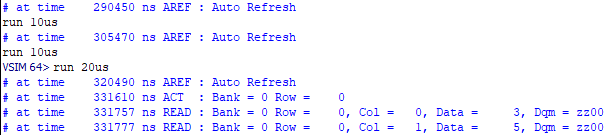

写完数据并不会立即读,而是一直在刷新,当读触发信号到达,开始读数据。

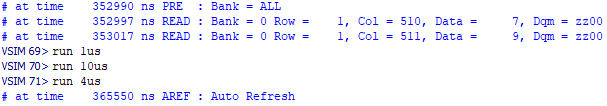

当读完SDRAM的两行数据,那么一直在刷新。

读end!

其中这里由于存在潜伏期,所以PRECHARGE命令之后,又重新读数据。

(4)从SDRAM读出数据。跟写原理一致。

前几个以及这个博文都用到的命令解释!

代码设计就不帖了。

仿真结果:

开始初始化:

初始化之后就开始写数据,并且满足15us的时间间隔,还会暂停写,跑去刷新,然后继续再写。

写完512个数据换第二行写

写完数据并不会立即读,而是一直在刷新,当读触发信号到达,开始读数据。

当读完SDRAM的两行数据,那么一直在刷新。

读end!

其中这里由于存在潜伏期,所以PRECHARGE命令之后,又重新读数据。