Verilog 习题笔记_实例化模块&多路复用器

习题来源:https://hdlbits.01xz.net/wiki/Main_Page

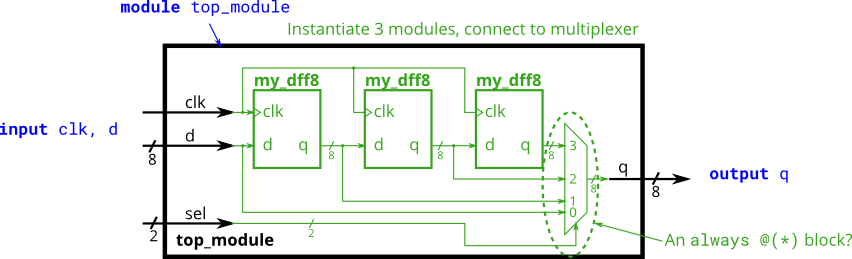

习题要求: 实例化三个my_dff8模块,然后将它们链接在一起,形成一个长度为3的8位宽移位寄存器,在此基础上实现一个4:1多路复用器,根据触发器的取值来选择要输出的内容。

习题分析:

1、需要注意三条8位矢量线,这里可以定义三个wire变量;

2、多路复用器可以用case函数来实现;

3、注意位宽;

1 module top_module ( 2 input clk, 3 input [7:0] d, 4 output [7:0] q 5 ); 6 7 wire [7:0] q1,q2,q3; 8 9 /*实例化三个my_dff8模块*/ 10 my_dff8 my_dff8_1 ( .q(q1), .clk(clk), .d(d) ); 11 my_dff8 my_dff8_2 ( .q(q2), .clk(clk), .d(q1)); 12 my_dff8 my_dff8_3 ( .q(q3), .clk(clk), .d(q2)); 13 14 /*实现多路复用寄存器*/ 15 16 always @(*) begin 17 case (sel) 18 1'd0 : q = d ; 19 1'd1 : q = q1; 20 1'd2 : q = q2; 21 1'd3 : q = q3; 22 endcase 23 end 24 25 endmodule

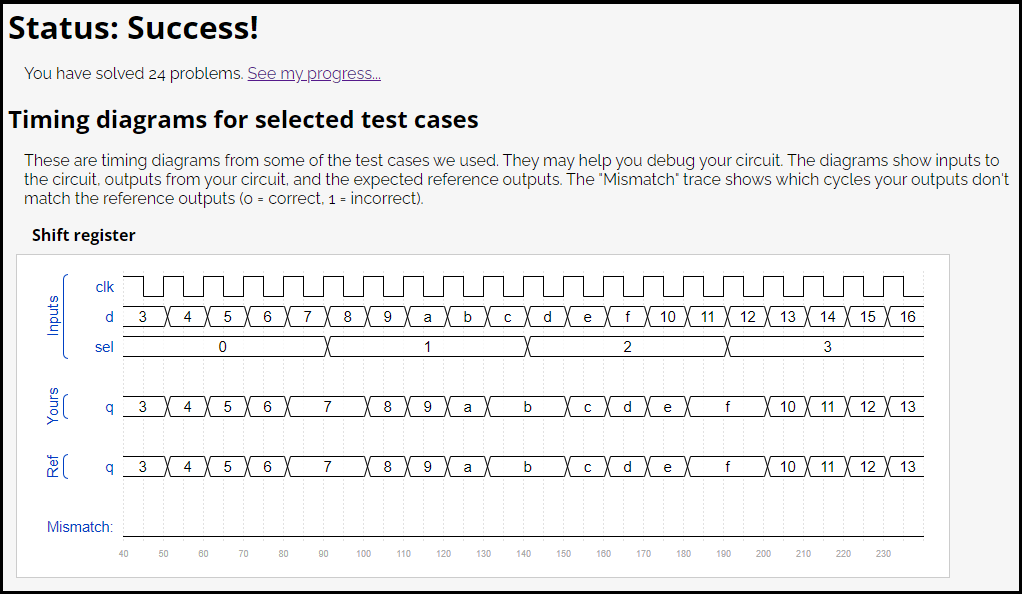

编译结果:

结果分析: sel为0、1、2、3时,d分别输出对应d、q1、q2、q3的值;

浙公网安备 33010602011771号

浙公网安备 33010602011771号