I2S和TDM模式详解

I2S接口

1.I2S简介

I2S,全称为Inter-IC Sound,也可写作Integrated Interchip Sound,有时简称为IIS,是飞利浦于1986年制定(1996年进行修订)的一种数字音频传输标准。它主要用于实现系统内部各器件之间数字音频数据的传输,像编解码器(CODEC)、数字信号处理器(DSP)、数字输入/输出接口、模数转换器(ADC)、数模转换器(DAC)以及数字滤波器等器件之间的音频数据传输都可以借助I2S来完成。需要明确的是,尽管I2S和I2C都是由飞利浦制定的,但二者之间并无关联。

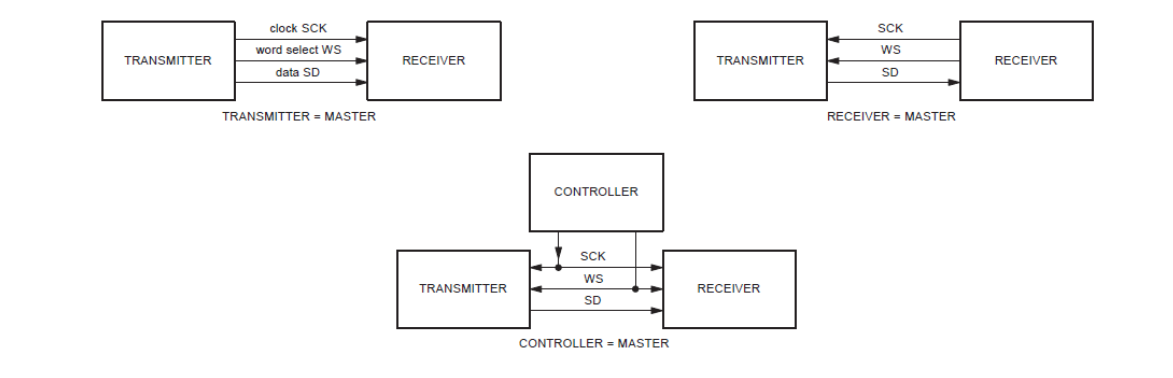

I2S是一种相对较为简单的数字接口协议,它并不具备地址或设备选择机制。在I2S总线所构建的系统中,同一时刻只能有一个主设备和一个发送设备。主设备可以是发送设备,也可以是接收设备,还可以是用于协调发送设备与接收设备之间数据传输的其他控制设备。在I2S系统里,能够提供时钟信号(包括SCK和WS)的设备就被认定为主设备。图3展示了一个典型的I2S系统框图。在一些高端应用场景中,编解码器(CODEC)常常被用作I2S的主控设备,以此来精准地控制I2S的数据流。

I2S系统通信配置框图:

I2S协议涵盖了左右两个声道(Left/Right)的数据传输,通过主设备发出的声道选择/字选择(WS)信号来实现左右声道数据的切换。若需要实现多声道(Multi-Channels)应用,可以通过增加I2S接口的数量或接入其他I2S设备来达成。

2.I2S信号线

在I2S传输协议中,数据信号、时钟信号以及控制信号是独立传输的。I2S协议仅定义了三根信号线:时钟信号线SCK、数据信号线SD以及左右声道选择信号线WS。

- 时钟信号 Serial Clock

SCK是模块内部的同步时钟信号。当模块处于从模式时,该信号由外部设备提供;而在主模式下,模块会自行生成SCK信号。需要注意的是,不同厂商生产的芯片型号中,时钟信号的命名可能有所差异。例如,有些芯片可能会将该时钟信号称为BCLK(Bit Clock)或SCL(Serial Clock)。 - 数据信号 Serial Data

在I2S协议中,SD(Serial Data)表示串行数据,它以二进制补码形式在数据线上传输。当WS(声道选择信号)发生变化后,第一个SCK(时钟信号)脉冲会先传输数据的最高位(MSB,Most Significant Bit)。这种传输方式的原因是发送设备和接收设备的字长可能不一致。如果系统的字长大于发送端的字长,数据在传输过程中可能会被截断(Truncated)。具体来说,当接收端接收的数据位数超过其规定的字长时,超出部分的最低位(LSB,Least Significant Bit)及之后的所有位将被忽略。反之,如果接收端的字长小于规定的字长,空余的位数将以0填充。这种机制确保了音频信号的最高有效位能够被正确传输,从而保障了音频的音质效果。 - 左右声道选择信号 Word Select

WS是声道选择信号,表明数据发送端所选择的声道。

在I2S操作模式为标准I2S模式时:WS=0,表示选择左声道;WS=1,表示选择右声道。

在I2S操作模式为左对齐模式或右对齐模式时::WS=1,表示选择左声道;WS=0,表示选择右声道。

注:关于I2S操作模式下文会提到

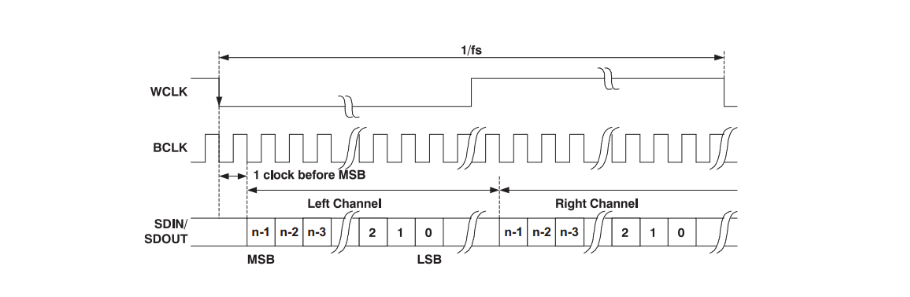

WS信号,也被称为帧时钟(Frame Clock),或者称为LRCLK(Left Right Clock)。它的频率与音频采样率相匹配。WS信号可以在SCK(时钟信号)的上升沿或下降沿发生变化。从设备会在SCK的上升沿对WS信号进行采样。数据信号的最高有效位(MSB)在WS变化后的第二个SCK上升沿才开始有效(即延迟了一个SCK周期)。这种设计是为了给从设备足够的时间来存储当前正在接收的数据,并为接收下一组数据做好准备。

I2S时序图:

3.I2S操作模式

I2S协议根据SD(串行数据)信号与SCK(时钟信号)和WS(帧时钟信号)之间的相对时序关系,被划分为三种不同的工作模式,分别是标准I2S模式、左对齐模式以及右对齐模式:

- I2S Phillips Standard 标准I2S格式

- Left Justified Standard 左对齐格式

- Right Justified Standard 右对齐格式

标准I2S模式

I2S模式可以被视为左对齐模式的一个特殊形式,也被称作PHILIPS模式。它是基于标准左对齐格式进一步延迟一个时钟周期而形成的。如图5所示,左声道数据的最高有效位(MSB)在WS信号的下降沿之后的第二个SCK/BCLK上升沿开始有效,而右声道数据的MSB则在WS信号的上升沿之后的第二个SCK/BCLK上升沿开始有效。

左对齐模式

左对齐模式的应用相对较少,其时序图如下图所示。与标准I2S模式对比可以发现,标准左对齐格式的数据最高有效位(MSB)并未相对于BCLK延迟一个时钟周期。在左对齐模式下,左声道数据的MSB在WS信号上升沿之后的第一个SCK/BCLK上升沿有效,而右声道数据的MSB在WS信号下降沿之后的第一个SCK/BCLK上升沿有效。标准左对齐格式的优势在于,由于在WS变化后的第一个SCK上升沿就开始采样,它无需考虑左右声道数据的具体字长。只要WS的时钟周期足够长,左对齐模式能够支持16到32位的字长格式。

右对齐模式

标准右对齐模式也被称作日本格式,即EIAJ(日本电子工业发展协会)格式或SONY格式,其时序图如图7所示。在这种格式下,左声道数据的最低有效位(LSB)在WS信号下降沿之前的那个SCK/BCLK上升沿开始有效,而右声道数据的LSB在WS信号上升沿之前的那个SCK/BCLK上升沿开始有效。与标准左对齐格式相比,标准右对齐模式的一个缺点是接收设备必须提前知晓传输数据的字长。这也正是许多编解码器(CODEC)提供多种右对齐格式选择功能的原因所在。

TDM

1.TDM简介

最开始出现的I2S只能传输左右两通道的数据,后来为了传输多通道数据,出现了I2S的变体,即应用了TDM(时分复用)模式。

协议时序与旧版I2S类似,但是出现了slot(槽)的概念。slot是指某个通道的一帧数据。

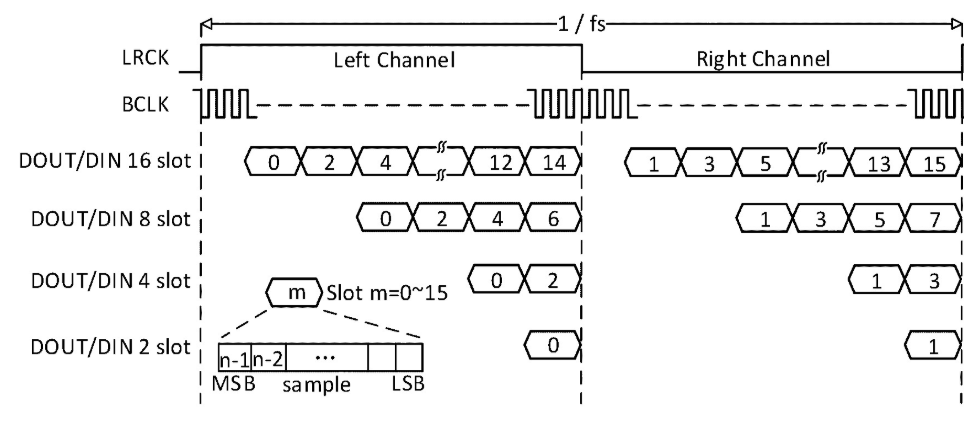

TDM数据传输示意图:

如上图,TDM数据传输示意图。 每个音频信号都被分配一个固定的slot(时间槽),这些slot按顺序排列组成一个帧。每个slot的长度相等且固定,可以容纳一个音频信号的数据。通过按照事先约定的顺序轮流填充每个slot,多个音频信号的数据被交错传输。

在发送端,音频TDM协议将多个音频信号的样本值分别放置在对应的slot中。

在接收端,协议按照相同的顺序将slot的数据取出,并重新还原成原始的音频信号。通过这种方式,多个音频信号可以同时传输在同一个信道上,实现了信道资源的高效利用。

注意:上面提到的slot与音频的声道没有直接的对应关系,跟实际芯片平台和Codec定义有关,不能简单的讲slot1理解位音频数据的第一个声道。例如假设slot1的长度位32bit时,slot1可以传输两路16位的音频数据。这种灵活性允许在不同的TDM实现中,根据具体的需求和约定来确定时间槽的长度以及每个时间槽所承载的音频信号的格式。

2.TDM信号线

音频TDM通过使用BLCK作为位时钟信号来确定数据传输的时钟速率和时序。Frame Sync信号用于标识音频帧的开始和结束,确保正确地组合和解析音频数据。Data IN和Data OUT信号引脚用于输入和输出音频数据,实现多路音频信号的合并和传输。

1、BLCK(Bit Clock):BLCK引脚是音频TDM中的时钟信号引脚。在每个BLCK时钟周期内,只能传输一个数据位。BLCK信号的频率决定了数据传输的速率,每个数据位在一个时钟周期内进行传输。发送端在每个时间槽中依次填充数据位,并在每个BLCK时钟周期根据BLCK信号的边沿将数据位传输出去。接收端根据BLCK信号的时钟边沿来采样和解析数据位,以还原音频信号。

2、Frame Sync(帧同步):Frame Sync引脚用于标识数据帧的开始和结束。在音频TDM中,多个slot被组合成一个完整的音频帧。Frame Sync信号的状态变化指示一个新的音频帧的开始。接收端根据Frame Sync信号来识别和解析每个slot的数据,并将其组合成原始的音频信号。

3、SD IN引脚:SD IN引脚是用于输入音频数据的引脚。

4、SD OUT引脚:SD OUT引脚是用于输出音频数据的引脚。

3.TDM时序

标准I2S模式

左对齐模式

右对齐模式

浙公网安备 33010602011771号

浙公网安备 33010602011771号