DRAM

DRAM

1. DRAM概念

DRAM,即动态随机存储器,一般由单MOS晶体管和电容器组成。

2. DRAM存储元

2.1 DRAM存储元结构及01存储

SRAM存储元是一个触发器,具有两个稳定的状态。但是SRAM使用MOS管数量多,成本大,价格高昂。

DRAM简化了存储元的结构,减少了MOS管的使用,所以存储密度更高;使用了电容器来表示数据的存储。

- 当电容器充满电时,代表存储了1。

- 当电容器放电至没有电时,代表存储了0。

2.2 DRAM读、写、刷新过程

这里讲一下MOS管和电容器如何存储01数据以及为何要进行刷新操作:

- MOS管的漏极与电容器相连并接地,当MOS管的栅极通电(即高电平时),PN结被导通,形成N沟道,源极和漏极导通。

- 如果给MOS管的源极输入高电平,即数据1。这时,没电的电容器开始充电,充满电后就代表存储了1,一般充电过程大约几纳秒(因为电容器容量极小,大约\(10^{-15}F\),只是起表示数据作用);如果输入低电平,则充满电的电容器开始放电(因为源极和漏极导通),放电结束后没有电的电容器代表数据0。

- 电容器的放电操作可以视为读操作,因为我们可以通过打开输出缓冲器/读放(读出放大器)获取数据。可以发现读操作是会对存储数据有破坏作用的:因为电容器放电在没有高电平输入的情况下是不可逆的,读一个1,存储该1的存储元被改写为0;同时,未读写的存储元也要定期刷新,因为电荷量会逐渐泄露而减少(1漏电至0)。

所以,需要在读操作后添加刷新操作,同时对未读写数据进行定期刷新,将被破坏的数据进行恢复。

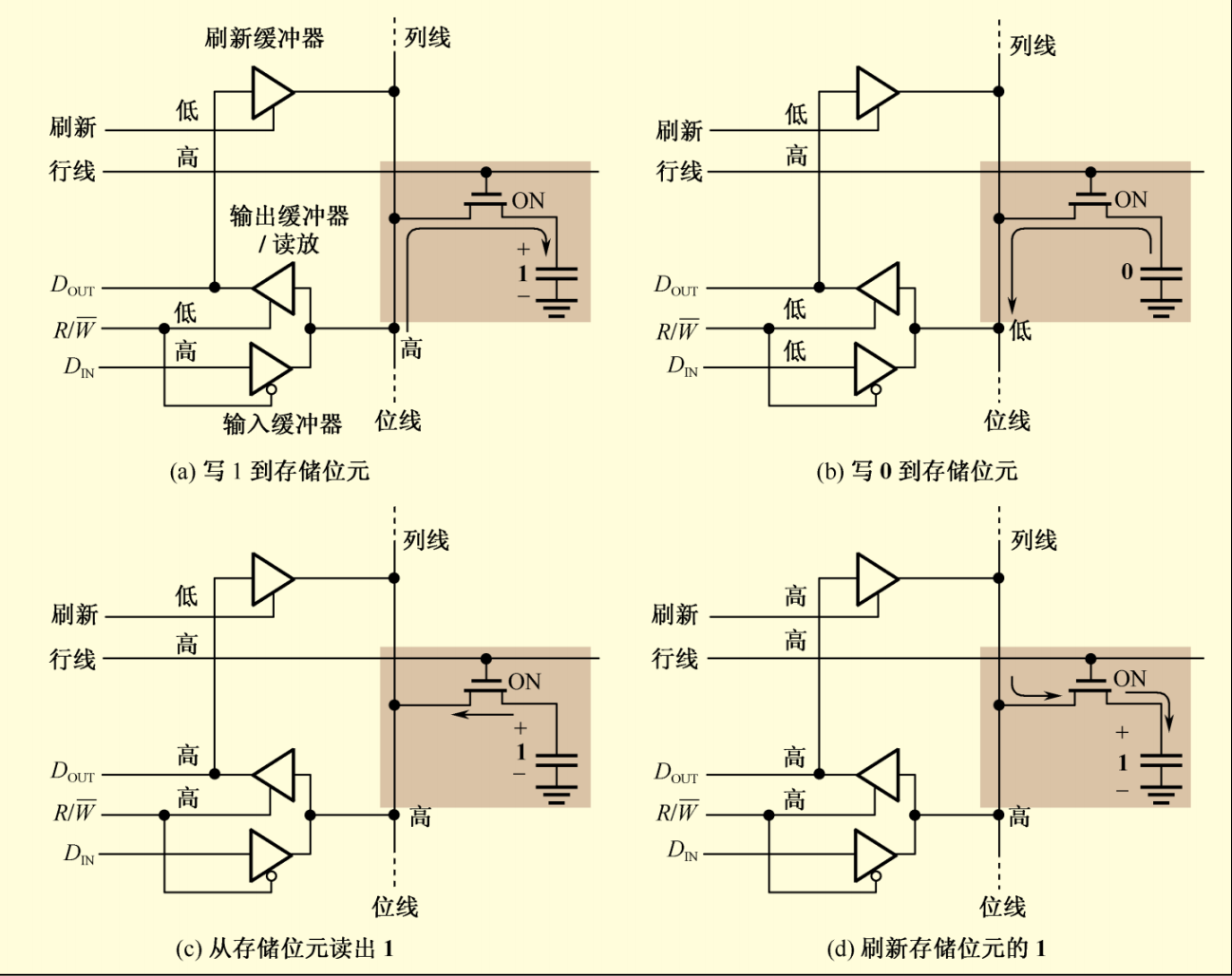

(1)写1到存储元和写0到存储元

前文已提到,这里不再赘述。

注意写操作中输入缓冲器打开(\(R/\overline{W}\)为低),输入\(D_{IN}=1或0\)到存储位元上;刷新缓冲器和输出缓冲器/读放要关闭,行选线为高电平因为要导通MOS管。

(2)从存储位元读出1

首先行选线为高电平,导通MOS管。

输出缓冲器/读放要打开(\(R/\overline{W}\)为高),输入缓冲器和刷新缓冲器要关闭。

如果当前存储元是1,就把1送到位线上,通过输出缓冲器/读放(读出放大器)使\(D_{OUT}=1\)。

(3)刷新存储位元的1

前文讲了刷新数据的原因。

读出的过程中可以完成刷新:读出1,输入缓冲器关闭,刷新缓冲器打开,输出缓冲器/读放打开,读出的数据\(D_{OUT}=1\)又经刷新缓冲器送到位线上再经MOS管写到电容上,存储元存储1。

注意:

- 输入缓冲器与输出缓冲器是互锁的,因为读操作和写操作是互斥的,不会同时发生。

- 读、写、刷新操作时行选线都是高电平,MOS管都是导通的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号