NFC芯片选型及基本电路框架

RFID作为一项专业度较高的技术,在一些公司,可能还会专门招聘专业的RFID工程师。本篇阐述的涉及到的只是基本选型设计、电路框架,关于RFID天线调试、低功耗检卡调试等,后续再其他篇章会继续更新!

NFC(Near Field Communication)芯片选型:

主要考量点:

芯片支持的协议、是否支持低功耗检卡、是否能过金融认证、芯片价格

芯片支持协议:

-

ISO14443A/B、ISO15693、 ISO18092 和 ISO21481 等

-

ISO14443A 卡:Mifare 系列、 Ultralight 系列、 Plus 系列、 CPU 卡系列等。

-

ISO14443B 卡:身份证、 SR176、 SRI512 等。

-

ISO15693:NXP 的 ICODE 系列、 TI 的 Tag_it HF-I、 ST LRI 等。

-

ISO18092:包括读卡模式、卡模式、点对点通信模式。

-

ISO21481:在 ISO18092 基础上兼容 ISO15693 协议。

-

LPCD 功能:芯片低功耗检测卡片功能。没有卡片靠近时,芯片处于低功耗状态, 仅需10uA 电流,就能完成卡片侦测, 当卡片靠近时,芯片侦测到卡片,唤醒单片机读卡。

-

金融认证:PBOC2.0/3.0 标准、 EMV 标准

电路架构:

NFC芯片外部电路通常由以下几个部分组成:供电电路、通信接口电路、天线电路、振荡电路;

供电电路:主要包括模拟电源AVDD、数字电源DVDD、发射器电源TVDD、引脚电源PVDD、测试引脚电源PVDD2;

a. 如果需要提高发射功率可提高TVDD的电压,例如5V供电的TVDD形成的发射功率会比3V的要强;

b. 芯片的供电电流通常在几十到几百mA,主要的能量消耗在发射器的电路上。例如FM175xx的天线发射电流在100mA,RC663则可以达250mA,因此选择供电芯片、电感器件时,需要注意留足余量;

c.读卡芯片天线13.56MHz的正弦波信号会干扰电源,为减少传导干扰,可以在电源端加π型滤波器,但为减少电路设计冗余度,一般情况下不添加。

通信接口:

通常都支持SPI/I2C/UART,一般通过外部引脚配置选择,为方便升级,可做兼容设计;

天线设计:

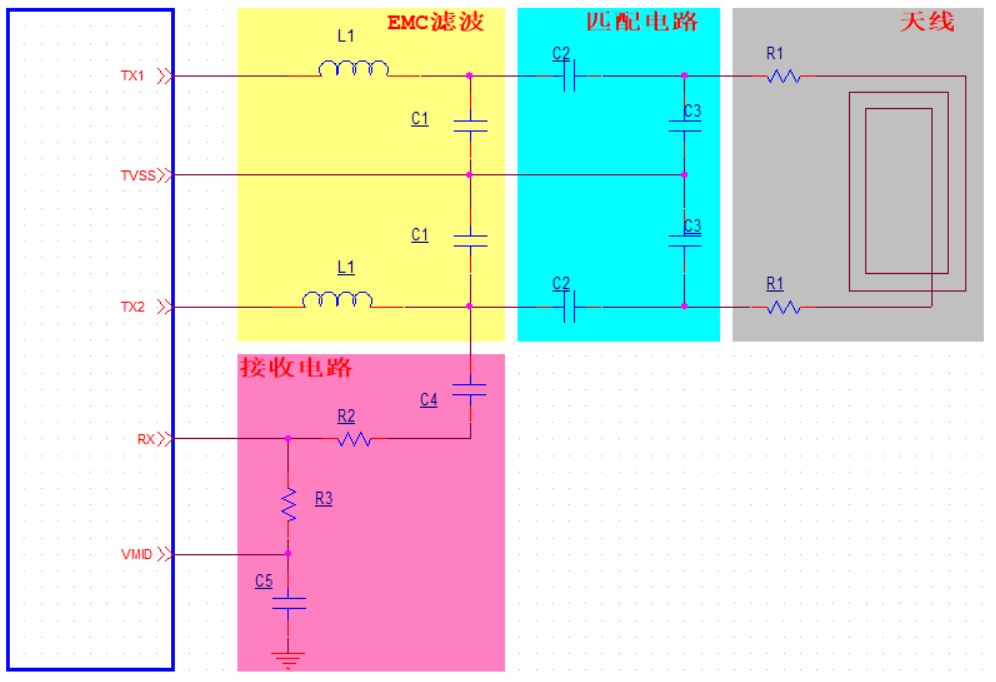

天线电路主要由4部分组成:EMC滤波、匹配电路、天线、接收电路。以FM17550为例,如下:

滤波电路:

由L1、C1组成的低通滤波器用于滤除13.56MHz的衍生谐波,该滤波器截止频率应设计在14MHz以上。L1电感不可靠近摆放,以免互相干扰(互感效应)。滤波电路元件匹配公式:f=1/(2π√LC)

匹配电路:

用于调节发射负载和谐振频率。射频电路功率受芯片内阻和外阻抗影响,当芯片内阻和外阻抗一致时,发射功率效率最高。C2是负载电容,天线感量越大,C2取值越小。C3是谐振电容,取值和天线电感量直接相关,使得谐振频率在13.56MHz。

接收电路:

C4滤除直流信号,R2和R3组成分压电路,使得RX接收端正弦波信号幅度在1.5-3V之间。

天线:

-

由R1电阻(通常是1ohm或0ohm)和印制PCB组成。

-

天线越大,读卡距离越远,当天线面积达到5cm x 5cm以后,再增大天线,读卡距离没有明显提升。

-

天线线宽建议选择0.5mm - 1mm。天线大于5cm x 5cm不能多于3圈,小于3cm x 3cm不能小于4圈

-

为减小EMC辐射干扰,需要将PCB走线转角处画成圆弧。

-

天线区域内和天线边缘禁止将信号、电源、地线画成圈或者半圆,天线圈内不可有大面积金属物体、金属镀膜,避免引起磁场涡流效应造成能力严重损耗。

-

天线PCB绕线方式是相对的,不是同向。

-

天线电路设计元件的精度应控制在2%以内,否则容易导致天线谐振频点偏差,导致读卡性能严重下降,产品一致性难以保证

天线大小和读卡距离关系

浙公网安备 33010602011771号

浙公网安备 33010602011771号