数字IC无毛刺时钟切换电路

背景

时钟切换在许多场景中是必要的,例如在时钟频率变化、电源管理、时钟域之间的通信以及故障恢复等。尤其是SoC中通常会有多个时钟,有芯片内部RC电路震荡的不那么精确的时钟,也有外部晶振输入的较精确的时钟,也有经过PLL倍频后的高速时钟,也有低功耗休眠时的低速时钟,在不同的场景进行时钟的切换以满足性能、功耗的需求等。

然而,时钟切换过程中常常伴随着时钟毛刺的问题,这对系统的性能和可靠性产生了负面影响。时钟切换过程中出现的不稳定和不理想的时钟信号可能导致电子系统中的逻辑错误、数据损坏以及时序故障。

无毛刺时钟切换是一种能够实现平滑过渡的技术,它的目标是在时钟切换过程中消除或最小化时钟毛刺,从而保证系统的正常运行。

接下来,介绍几种无毛刺时钟切换电路,并进行仿真,展示其在时钟切换中的性能和可靠性。

其中电路来自于《数字IC设计入门》。使用增加延时的Verilog前仿来进行实验。

无毛刺时钟切换的重要原则

- 确保先关断再使能

- 与门在下降沿采样选择信号,或门在上升沿

电路1

module clk_exchange1(

input clk_in_0,

input clk_in_1,

input rst_n_0,

input rst_n_1,

input sel,

output clk_out

);

wire sel_bar;

wire sel_result_0;

wire sel_sync_0;

wire sel_sample_0;

wire sel_fb_0;

wire clk_and_0;

wire sel_result_1;

wire sel_sync_1;

wire sel_sample_1;

wire sel_fb_1;

wire clk_and_1;

assign sel_bar = ~sel;

assign sel_result_0 = sel_bar & sel_fb_1;

sync #(

.STAGES(2),

.RESET_VALUE(0)

) u_sync_0(

.clk_in(clk_in_0),

.rst_ni(rst_n_0),

.serial_in(sel_result_0),

.serial_out(sel_sync_0)

);

DFF_N #(

.RESET_VALUE(0)

)u_dffn_0(

.clk(clk_in_0),

.rst_n(rst_n_0),

.d(sel_sync_0),

.q(sel_sample_0)

);

assign sel_fb_0 = ~sel_sample_0;

assign clk_and_0 = clk_in_0 & sel_sample_0;

assign sel_result_1 = sel & sel_fb_0;

sync #(

.STAGES(2),

.RESET_VALUE(1)

) u_sync_1(

.clk_in(clk_in_1),

.rst_ni(rst_n_1),

.serial_in(sel_result_1),

.serial_out(sel_sync_1)

);

DFF_N #(

.RESET_VALUE(1)

)u_dffn_1(

.clk(clk_in_1),

.rst_n(rst_n_1),

.d(sel_sync_1),

.q(sel_sample_1)

);

assign sel_fb_1 = ~sel_sample_1;

assign clk_and_1 = clk_in_1 & sel_sample_1;

assign clk_out = clk_and_0 | clk_and_1;

endmodule

大致可分4级:

- sel信号switch

- 同步器

- 下降沿采样与反馈

- 时钟与和或

下降沿采样的必要性

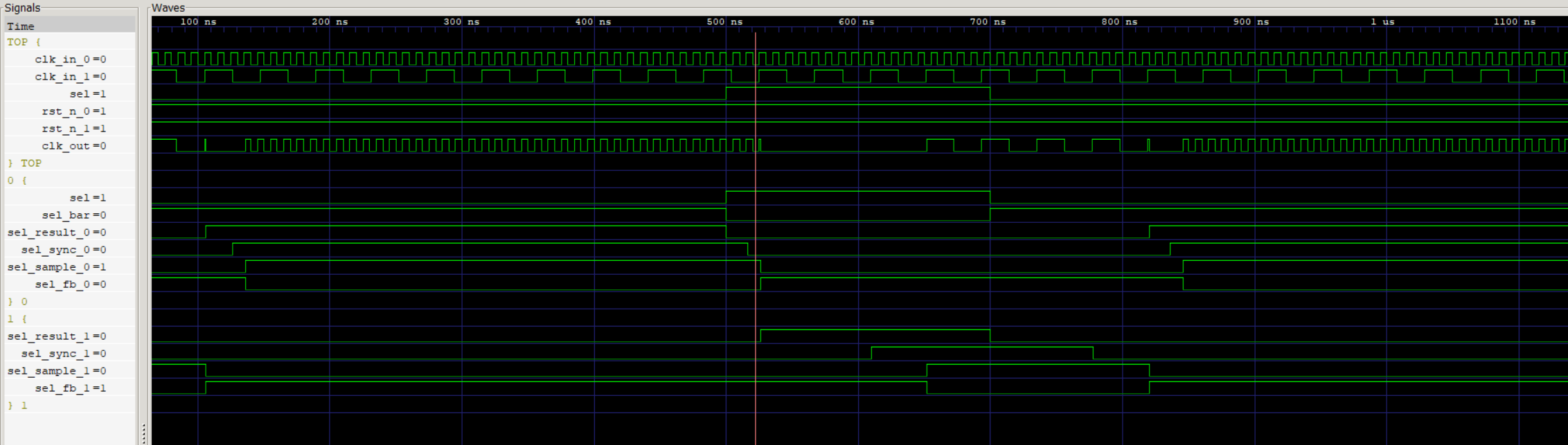

下图是模拟触发器有一定延迟时采用上升沿采样的现象,有毛刺

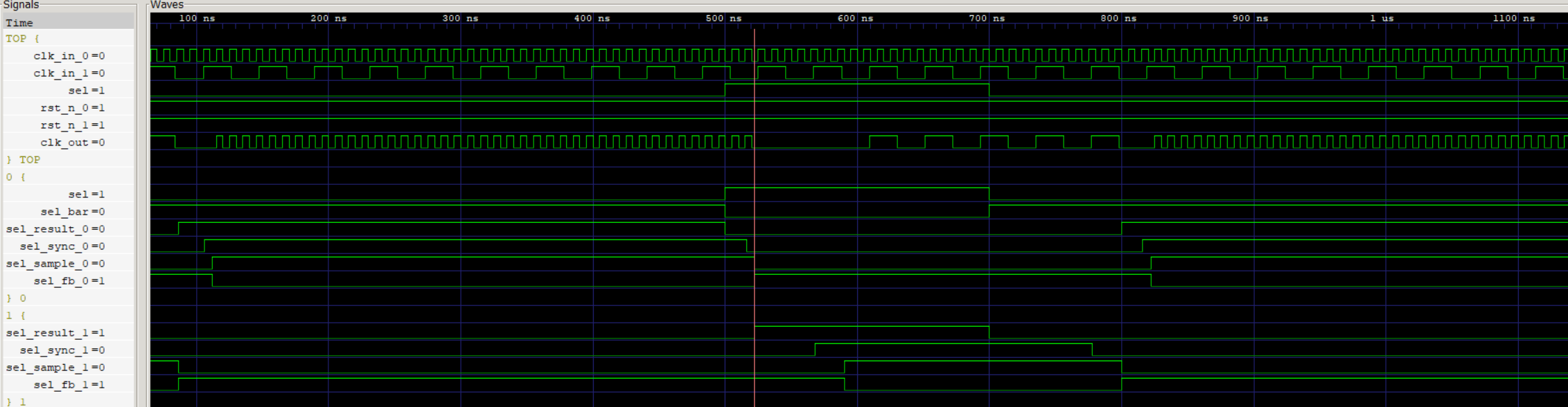

下图是同样触发器有延迟,采用下降沿采样的现象,无毛刺

因为是选择信号最终与时钟信号相与,而触发器有一定延迟,采样的信号相比时钟上升沿有一个延迟,而相与之后会产生一个窄脉冲,而这就是我们不希望的时钟毛刺

在A->B和B->A时都可能产生这个毛刺

而如果使用下降沿采样,则就算有延迟,但这个时候时钟为0,相与还是为0。

同步器

时钟切换中,哪怕多一些延迟,我们也不希望有毛刺。

这里控制信号以及对方反馈来的信号相对当前时钟都是异步信号,为了避免亚稳态,采用典型2级触发器来实现同步。

浙公网安备 33010602011771号

浙公网安备 33010602011771号