AXI4协议专题实战——基于AXI4-Lite的PL2PS数据交互

在 ZYNQ SoC开发中都会遇到这样一个问题:如何让 PS(ARM 处理系统)读取到PL(FPGA 可编程逻辑)内部的数据?

比如,你在 PL 里实现了一个计数器、滤波器,或者采集了传感器的实时数据,接下来要交给 PS 端去处理和显示。那么问题来了:

数据交互通道选哪种? AXI4、AXI4-Stream 还是 AXI4-Lite?

如何设计接口? 是用 DMA 搬运高速数据,还是只需要简单的寄存器访问?

怎样验证交互是否正确? 光靠软件输出够不够,还是需要借助 ILA 上板抓数?

在这些场景中,如果你只是需要 低速的寄存器读写,让 PS 能随时访问 PL 内部状态,那么 AXI4-Lite 就是最合适的选择。

本文将结合一个完整的实验案例,从 AXI协议原理 出发,带你逐步完成基于 AXI4-Lite的PL2PS数据交互, 并通过Verilog HDL源码实现与ILA上板验证,让你真正把书本上的协议知识转化为可运行的工程。

- 本篇文章重点介绍基于AXI4_LITE的PL2PS进行数据交互的操作。全文的章节分为以下四个部分组成:

1、AXI4、AXI4_STREAM、AXI4_LITE的基本原理;

2、基于AXI4_LITE的PL2PS数据交互实验的开发环境;

3、基于AXI_LITE的PL2PS数据交互的Verilog HDL实现;

4、基于ILA的实际上版测试结果。

- 基本原理

在 AMBA (Advanced Microcontroller Bus Architecture) 总线体系中,AXI(Advanced eXtensible Interface)是目前最常用的接口协议,主要包括以下几种:

- AXI4-Full

- AXI4-Stream

- AXI4-Lite

小结: 在本次实战中,我们选择 AXI4-Lite,实现 PS 端通过寄存器访问方式,获取 PL 内部的数据。

-

开发环境

🔹开发环境: VIVADO 2019.2 + Vitis 2019.2

🔹仿真环境: Modelsim SE-64 10.7

🔹硬件平台: XC7Z020CLG400-2(自定义开发板即可)

🔹代码文本编辑器: Microsoft VS Code🔹实验目标:

1、在 PL 中实现一个 AXI4-Lite 从设备(Slave)IP核。

2、在该 IP 内部定义寄存器,用于存放数据(如计数器值);

3、通过 AXI4-Lite 总线将寄存器数据传递到 PS 端;

4、在 PS 端编写 C 程序读取寄存器,实现PL→PS数据交互;

5、在 PS 端编写 C 程序写入寄存器,实现PS→PL数据交互; -

Verilog HDL实现

在PL中设计一个简单的AXI4-Lite从设备,实现如下功能:

🔹通过地址映射,PS可以读取PL内部的寄存器;

🔹PL内部寄存器存储一个递增计数器值(这里FPGA以1s的周期产生计数器传递给PS端,便以观察);

🔹PS端控制寄存器下发数据给PL端(PL在ILA中进行观察是否为下发的数据);

🔹PS端每次都能读取寄存器,都能获得最新的数据。本文从零开始,从搭建基本的工程开始一步一步讲解AXI4-LITE的数据交互程序实现:

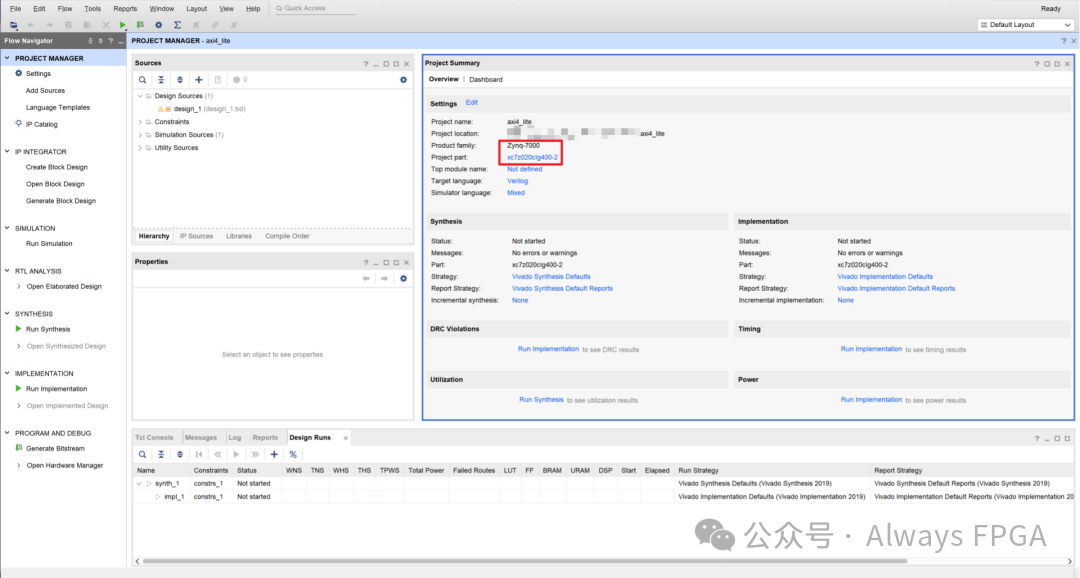

第一步, 搭建的VIVADO工程如下图所示,这一步选择指定开发板的型号即可,本文所使用的FPGA型号为XC7Z020CLG400-2(读者可根据手中开发板的型号相应选择即可)。

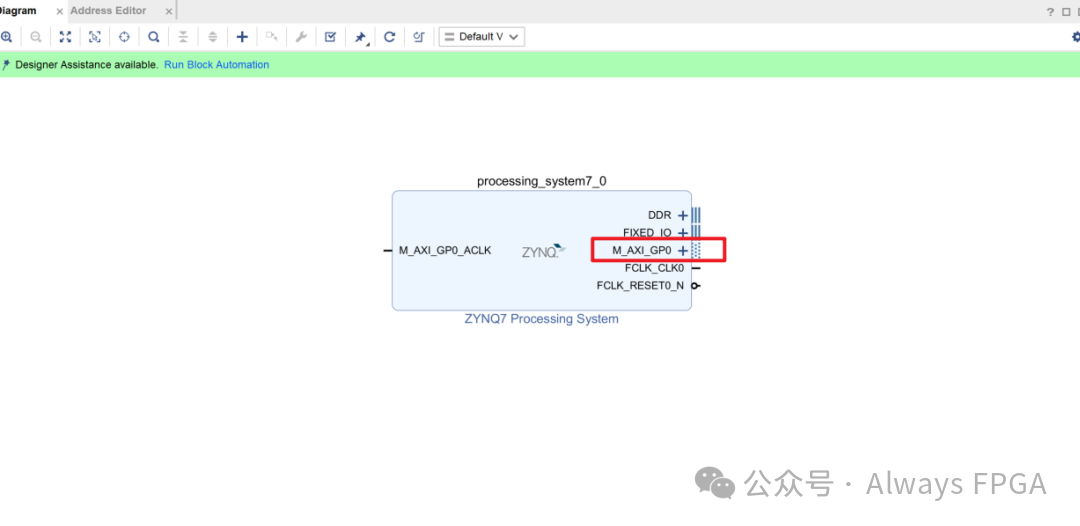

第二步, 搭建好相应的Block Design设计如下图所示,在这一步的BD中,只需要添加ZYNQ的软核(processing_system7_0),打开M_AXI_GP0接口,修改相应的DDR型号即可。

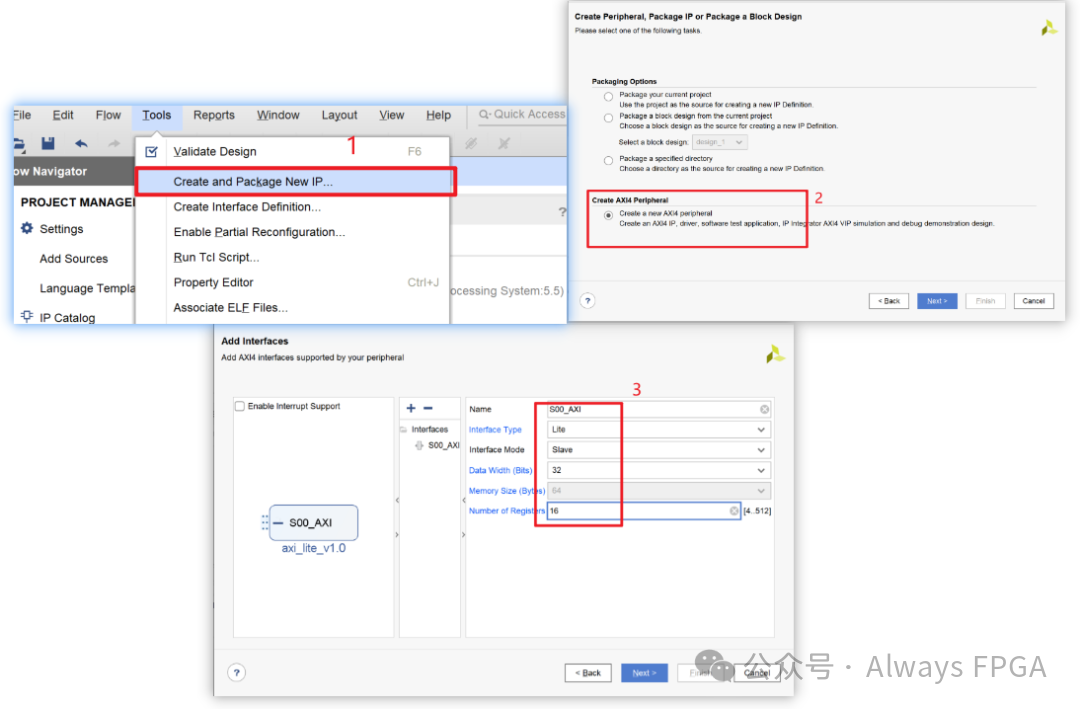

第三步,也是最关键的一步,添加AXI4-LITE的IP模板,安装下图中操作步骤即可完成AXI4-LITE的创建模板,后续在Xilinx提供的模板上进行操作即可。

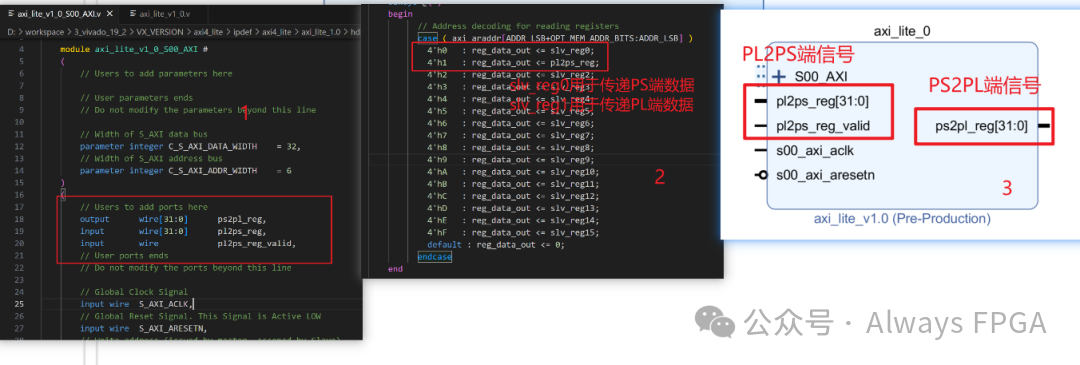

第四步,打开AXI4-LITE模板,修改代码,完成本次实验,如下图添加“PS2PL_REG”、“PL2PS_REG”两个端口完成PL2PS以及PS2PL的操作流程。在第一步中添加顶层端口,在第二步中修改模板传递FPGA端的数据,第三步为修改后模板的IP核界面。

第五步,BD工程完成连线布局,整体的连线框图如下所示,axi_lite的address为0x43c0_0000—0x43c0_ffff,后续在PS端操作读写这个地址即可完成PL2PS的数据交互。

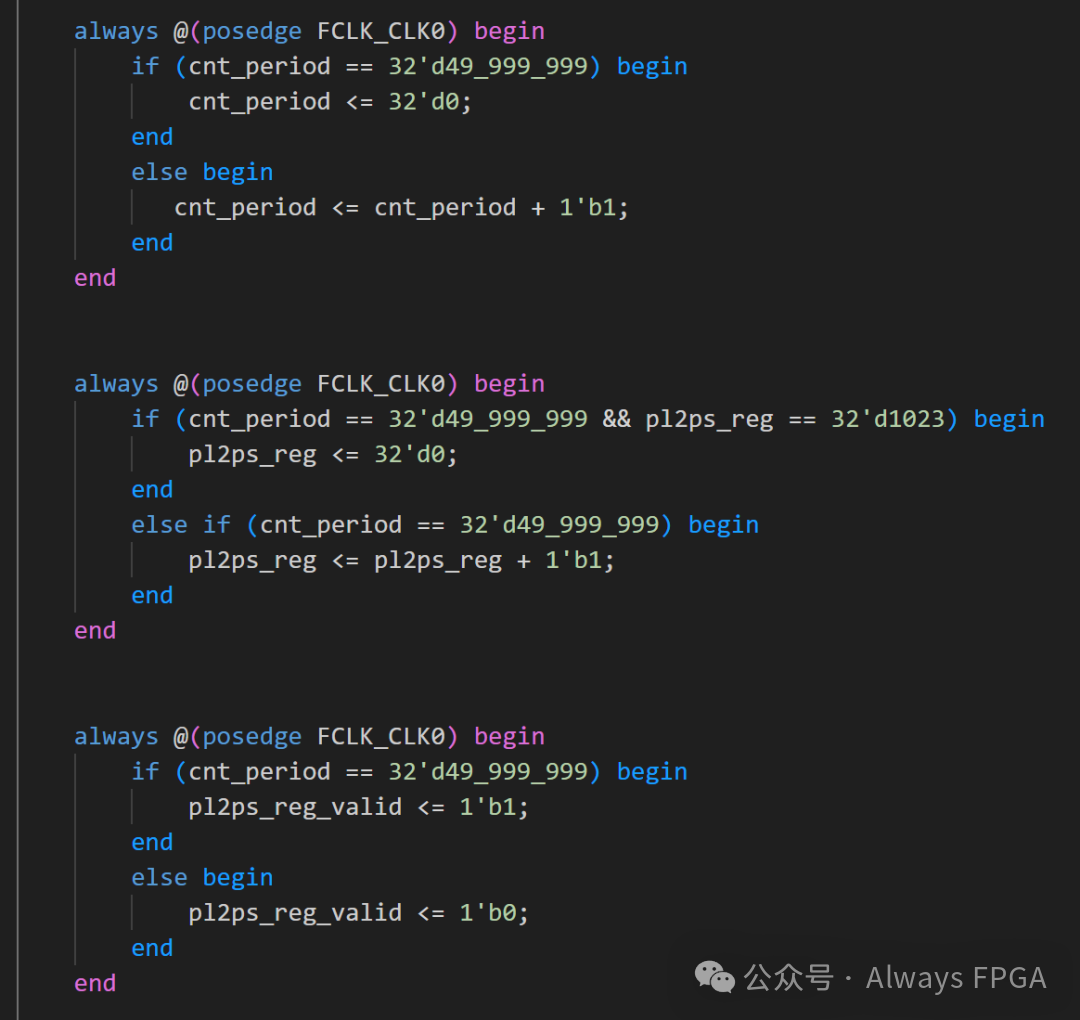

第六步,为添加相应的计数器传递给PS端,PL端简单编译的计数器如下图所示。PL传递的递增数每过一秒加1,递增范围为0~1023递增。

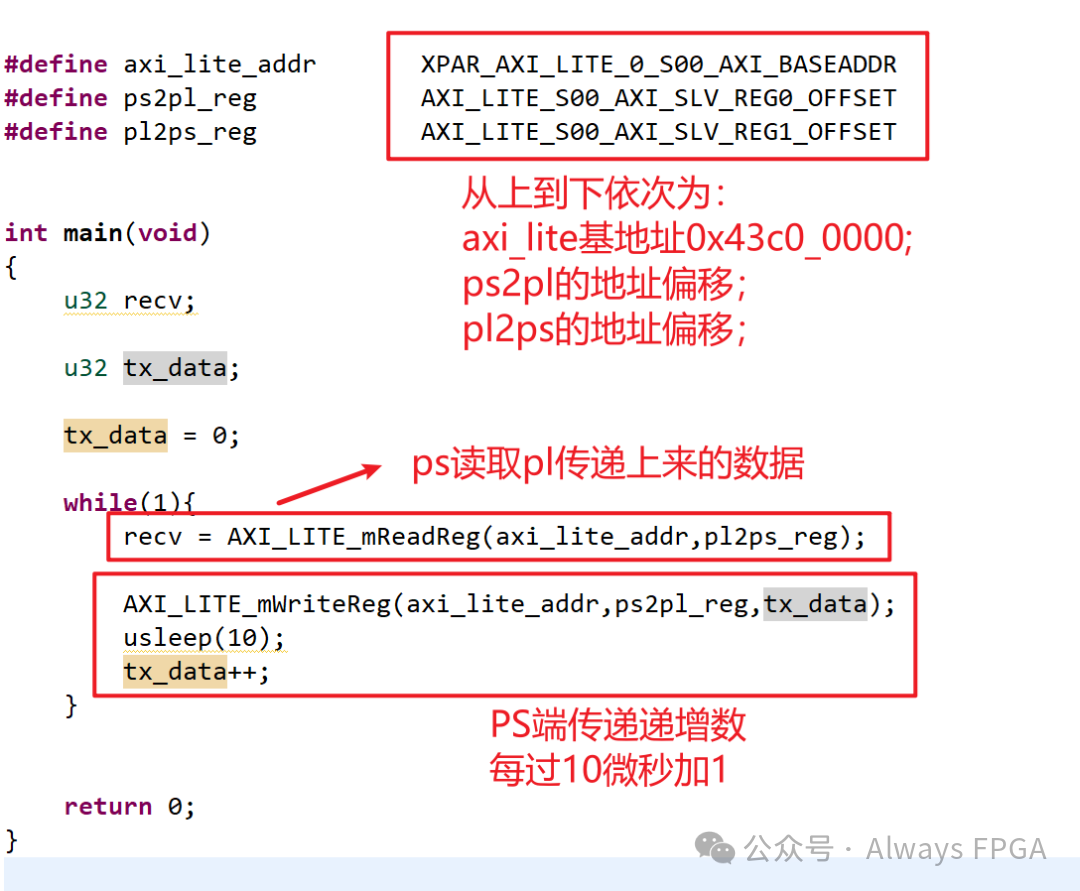

第七步,PS端编写相关C代码,完成PL2PS的数据传递,PS端的部分代码如下图所示,PS端每过10微秒读取一次PL端传递的数据,同时PS端每过10微秒,将传递给PL端的计数器加一。

- ILA实际上板测试结果

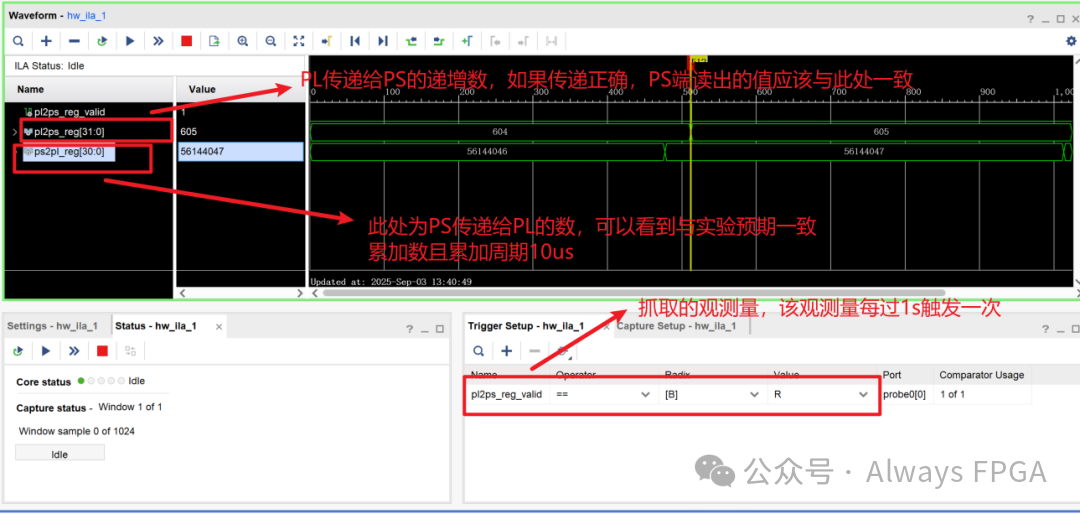

为了验证上述的数据交互是否按理论运行,在VIVADO中添加了ILA(Integrated Logic Analyzer),对PL内部信号进行实时采集。

测试过程:

🔹接入 ILA,对计数器输出与 AXI4-Lite 读数据通道进行观测;

🔹在 PS 端运行 C 程序,循环读取寄存器;

🔹比较 ILA 采集波形与 PS 端输出结果。

实际通过ILA观察的结果如下图所示,PS传递给PL的数据和我们所预想的一样,10us周期的累加数,PS2PL数据传递成功。

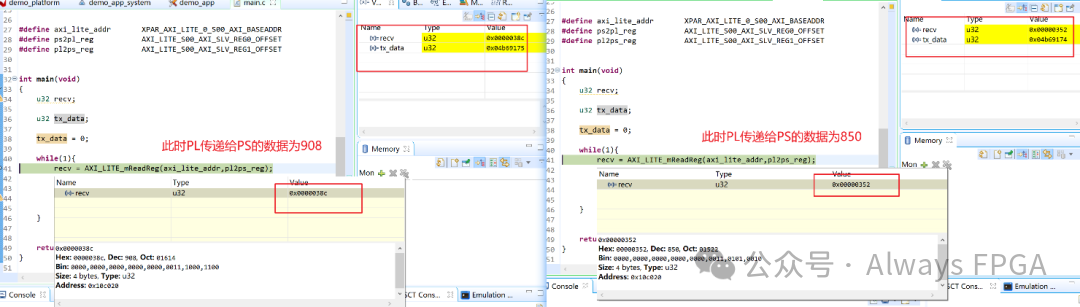

接着,在VITIS观察PL2PS的数据,是否为1s周期的累加数,在PS端相应的数据接收端打断点,连续两次捕获的数据可以看到数据为累加数,与我们的预期一致。

- 全文总结

通过本文的实验,我们完整走了一遍 AXI4-Lite 的PL2PS数据交互流程: 从协议原理,到开发环境搭建,再到 Verilog 实现与 ILA 验证。可以看到,AXI4-Lite 的优势就在于简单、直观、寄存器级控制,非常适合状态寄存器读取、低速控制信号交互等场景。

不过,** AXI4-Lite ** 并不是万能的。当我们需要传输大规模数据块(如图像帧、波形数据)时,就必须借助AXI4 高性能接口结合 DMA;当我们需要处理实时流式数据(如视频流、ADC采样流),则要用到AXI4-Stream。

换句话说,本文只是 AXI4协议实战的起点。 掌握了 AXI4-Lite,你就能顺利迈向 AXI4 与 AXI4-Stream 的更复杂应用。未来,你完全可以在此基础上扩展出 PL侧产生高速数据 → 通过 DMA 搬运 → PS侧处理显示 的完整链路,从而把 ZYNQ 的优势发挥到极致。

到这里,我们就完成了一个完整的 AXI4-Lite 实战案例:从协议原理到 Verilog 实现,再到 ILA 验证,验证了 PL 到 PS 数据交互的全过程。

那么问题来了:

👉 在你的项目中,你更常用 AXI4-Lite 来做寄存器控制,还是更倾向于用 AXI4/AXI4-Stream 来处理高速数据?

👉 你觉得在实际工程中,AXI4-Lite 的应用场景还有哪些?欢迎在评论区留言,分享你的使用经验和踩过的坑,也许会帮到正在学习 AXI 的朋友们。😊

- 本文由Always FPGA原创,转载请注明以上来源。同时欢迎大家关注我的微信公众号:Always FPGA,如需交流,欢迎与我联系!

浙公网安备 33010602011771号

浙公网安备 33010602011771号