ram接口的读写时序

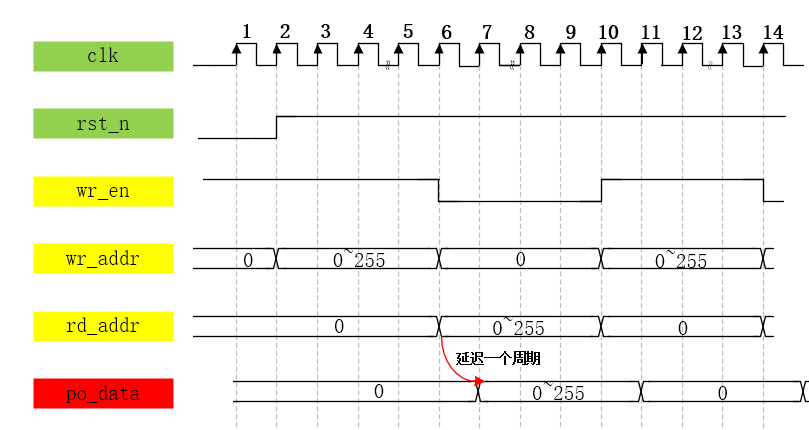

RAM的分类比较多,单口RAM,双口RAM等等,详细的不再介绍。这里使用的是simple dual port RAM。本次实验的内容是RAM的交替读写,RAM的读写位宽和深度都设置为256x8来完成这部分的内容。

内部产生一个写使能信号,当写使能信号为高时向RAM中写入数据,写端口的地址开始叠加,当写完数据之后把写使能信号拉低,此时开启RAM的读端口,读地址开始叠加,当读完数据后在写使能信号拉高,开始写入数据,如此往复循环。

绘制波形如下:

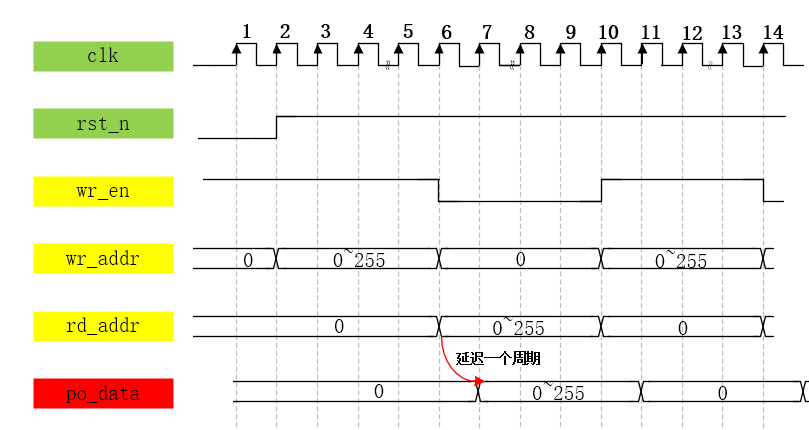

RAM的分类比较多,单口RAM,双口RAM等等,详细的不再介绍。这里使用的是simple dual port RAM。本次实验的内容是RAM的交替读写,RAM的读写位宽和深度都设置为256x8来完成这部分的内容。

内部产生一个写使能信号,当写使能信号为高时向RAM中写入数据,写端口的地址开始叠加,当写完数据之后把写使能信号拉低,此时开启RAM的读端口,读地址开始叠加,当读完数据后在写使能信号拉高,开始写入数据,如此往复循环。

绘制波形如下: