AHB中的ERROR response

1.前言

AHB是Advanced High-performance Bus的简称,AHB是

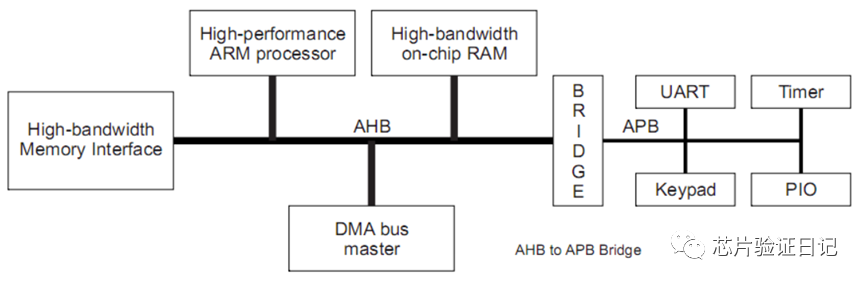

AMBA(Advanced MicrocontrollerBus Architecture高级微控制器总线架构)总线的一部分,AMBA总线最初是ARM公司提出的,如今被市面上大多数SoC芯片所采用。典型的应用如ARM核与系统内部的高速RAM,Nand Flash,DMA,Bridge 的链接,也有项目用AHB总线配置寄存器。下图是ARM官方协议中给出的一个典型的应用场景。

2. 几个常用术语

2.1 Bus cycle[总线周期]:总线时钟周期的基本单元,对于AHB协议的描述目的是定义为从上升沿到上升沿的转变。总线信号的时序都是基于总线周期时钟的。

2.2 Bus transfer[总线传输]: AHB总线传输是对数据目标的读写操作,可能会持续一个或者多个总线周期。总线传输在收到对应从机的完成响应(completion response)后终止。

2.3 Burst operation[突发操作]: 突发操作定义为一个或多个数据的传输,由总线主机发起,在地址空间增加时传输宽度保持一致。每次传输增加的步长(地址)由传输大小决定(字节,半字,字)。其本质就是:在一段时间中,连续地传输多个(地址相邻的)数据或地址。Burst由beats组成,一个beat就是一个transfer。

2.4 transfer[传输]:每个burst中传输一至多个数据,每个传输的数据被称为transfer。transfer又被称为beat,一拍数据。

2.5 beat[节拍]:Beat是突发传输(burst)中的单个数据传输,一拍数据。

2.6 transacton[事务]:主机启动一个transaction与从机通信,主机和从机之间一整套的信息交换构成了一个transaction。简单来讲,transaction就是传输一段数据所需要的一整套操作。

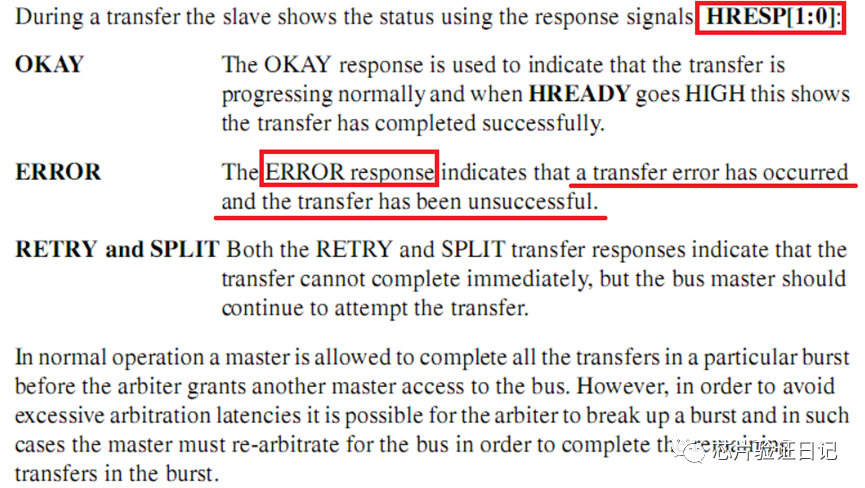

- ERROR response

3.1 双周期响应

如下图所示,ERROR response由信号HRESP[1:0]来表示,仅有OKAY响应可以在单个周期里给出。ERROR/SPLIT/RETRY response需要至少两个周期。为了完成这些响应(ERROR/SPLIT/RETRY response)中的任意一个,那么在倒数第二个(最后一个的前一个)周期,从机驱动HRESP[1:0]以表示ERROR/SPLIT/RETRY,并同时驱动HREADY为低电平,以给传输扩展一个额外的周期。在最后一个周期HREADY被驱动为高电平以结束传输,同时HRESP[1:0]保持驱动以表示ERROR/SPLIT/RETRY。

需要双周期响应是因为总线的流水线性质(pipelined nature of the bus)。在从机开始发出ERROR/SPLIT/RETRY中任何一个响应时,接下来传输的地址已经广播到总线上了。双周期响应允许主机有足够的时间来取消该地址并且在开始下一次传输之前驱动HTRANS[1:0]为空闲(IDLE)。

如果从机需要两个以上的周期以提供ERROR/SPLIT/RETRY response,那么可以在传输开始时插入额外的等待状态。在此期间,HREADY信号将为低电平,同时响应必须被设置为OKAY。

对于ERROR response,由于当前传输不被重复,所以可以选择完成接下来的传输。

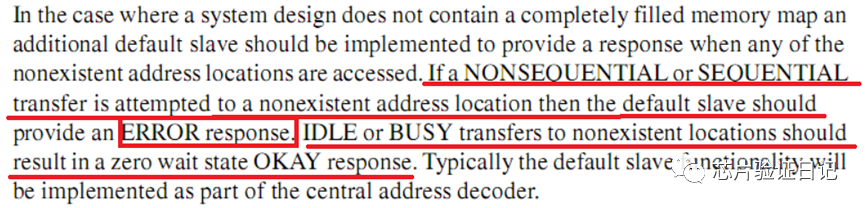

3.2 ERROR response的场景

如下面截图中所说,在系统设计中,如果有包含一个存储器映射并未完全填满(存储空间)的情况时,应该设置一个额外的默认从机以在访问任何不存在的地址空间时提供响应。如果一个非连续(NONSEQUENTIAL)或者连续(SEQUENTIAL)传输试图访问一个不存在的地址空间时,这个默认从机应该提供一个ERROR response。

ERROR response被从机用来表示某种形式的错误条件和相关的传输。典型的这被用作保护错误,例如试图写一个只读的存储空间。

需要双周期响应是因为总线的流水线性质(pipelined nature of the bus)。在从机开始发出ERROR/SPLIT/RETRY中任何一个响应时,接下来传输的地址已经广播到总线上了。双周期响应允许主机有足够的时间来取消下一次访问,并在开始下一次传输之前驱动HTRANS[1:0]为空闲(IDLE)。

3.3 ERROR response的时序分析

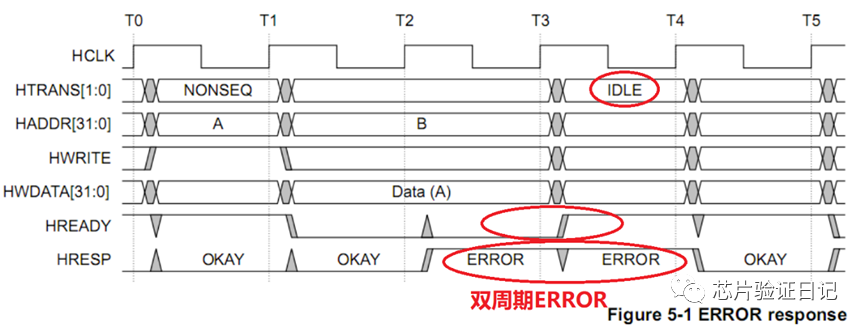

下图是ERROR response的时序图:

T1-T2: 从机插入一个wait状态,并且回OKAY 响应(response);

T2-T3: 从机回ERROR response。这是ERROR响应的第一个周期,因为HREADY为低电平;

T3-T4: 从机回ERROR response。这是ERROR响应的最后一个周期,因为HREADY为高电平,这时主机将传输类型(HTRANS)更改为IDLE,这就取消了在时间T2的HADDR=B的预定的交易(transaction)。

T4-T5: 从机回一个OKAY响应(response)。

如果从机提供一个ERROR response,那么主机可以选择取消突发中剩下的传输。然而,这并不是一个严格要求,同时主机可以继续突发中剩下的传输。对于读操作,当接收到从机的ERROR response时,主机可能仍在使用数据。从机不能依靠ERROR response来阻止读取HRDATA上的值。对于读操作,当ERROR response发生时,建议将HRDATA驱动为零。

【提醒】对于上面高亮部分的解释说明,有些VIP(比如C家的vipcat)的检测机制比较严格,并不会遵守这一点,而是会严格的根据下图中的时序进行时序检查,大家注意这一点。

3.3 ERROR response的时序分析

下图是ERROR response的时序图:

T1-T2: 从机插入一个wait状态,并且回OKAY 响应(response);

T2-T3: 从机回ERROR response。这是ERROR响应的第一个周期,因为HREADY为低电平;

T3-T4: 从机回ERROR response。这是ERROR响应的最后一个周期,因为HREADY为高电平,这时主机将传输类型(HTRANS)更改为IDLE,这就取消了在时间T2的HADDR=B的预定的交易(transaction)。

T4-T5: 从机回一个OKAY响应(response)。

如果从机提供一个ERROR response,那么主机可以选择取消突发中剩下的传输。然而,这并不是一个严格要求,同时主机可以继续突发中剩下的传输。对于读操作,当接收到从机的ERROR response时,主机可能仍在使用数据。从机不能依靠ERROR response来阻止读取HRDATA上的值。对于读操作,当ERROR response发生时,建议将HRDATA驱动为零。

【提醒】对于上面高亮部分的解释说明,有些VIP(比如C家的vipcat)的检测机制比较严格,并不会遵守这一点,而是会严格的根据下图中的时序进行时序检查,大家注意这一点。

参考文献

[1] https://blog.csdn.net/juvenilexhq/article/details/126241189

[2] AMBA5 AHB Protocol Spec.pdf

[3] AMBA2 Spec.pdf

浙公网安备 33010602011771号

浙公网安备 33010602011771号