验证环境获取DUT内部信号的方法

在UVM寄存器模型的操作中,寄存器用于设置DUT状态和芯片状态信息的上报,有前门和后门读写两种方式。

推而广之,其他的DUT内部信号,由于验证的需要,有时也需要进行后门读写。这些信号除了包含前门可读的寄存器以外,还会包含reg/wire信号、状态机的状态值、memory内容等。总的来看,获取DUT内部状态分为前门和后门两种方式。

前门读写

前门读写:使用总线对DUT发起真实的读写,一般需要总线VIP支持,仅针对DUT内部可访问的地址空间,如配置和上报寄存器、memory。

这种方式好处在于能够和芯片真实的工作场景保持高度相似,能够发现时序配合上的一些问题。

缺点一方面也是前门的“真实性”,当需要读写的地址空间数量很大时,会消耗非常多的仿真时间,影响用例的执行效率。

另一方面是这种耗时的读写不满足“实时性”比对的验证要求。某些验证环境中,可能需要在几个cycle内完成对DUT状态的获取和比对,这种场景下前门读取方式则无法满足。

后门读写

后门读写:绕过前门总线,直接通过DUT内信号的hierarchy路径强制force或者读取信号值。

后门操作的方式可以分为:按信号的Hierarchy读取、interface连接DUT信号、和VPI访问。

- 信号的Hierarchy读取

DUT经过编译后,内部的信号都有对应的hierarchy路径,如dut.a.b.c,dut.out。在验证环境中可以直接使用,例如:

bit A;

A=dut.sub_block.A;

if(A==0) begin

.....

end

此种方式的缺点是会直接在环境中出现各种繁杂的hierarchy路径,当dut的层次变化时,环境也需要做适配,如此不利于环境管理。

另外最重要的特点在于:使用hierarchy不能出现在package中。

package的定义和使用是systemverilog的一大特色,可以进行组件结构化设计,package之间互不影响,如UVM的env、agent、driver等组件,一般都会封装在一个package内。

2. interface连接

对上述方式改进后,可以使用interface作为DUT和验证环境的中间代理。在testbench的顶层完成DUT和interface的连接,并将interface传递到验证环境中。virtual interface可以出现package、class内,验证环境内使用interface中的信号,尽可能减少DUT改动对验证环境内部的影响。

3. VPI访问

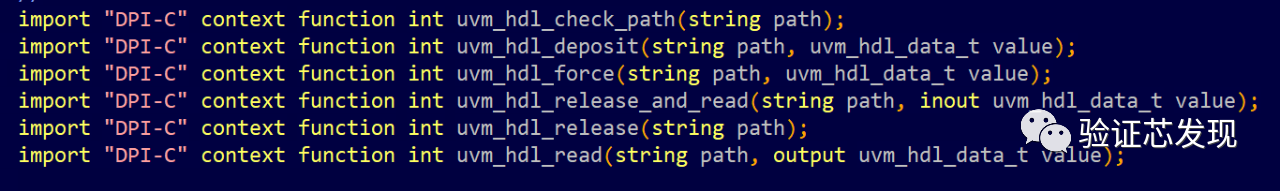

systemverilog支持VPI接口,DUT经过编译后,可以通过VPI接口访问DUT内部信号,把信号的hierarchy换成字符串即可。经过UVM封装后,可以直接使用uvm_hdl_force/read等接口。

bit A;

bit[15:0] B

if(uvm_hdl_read("dut.sub_block.A",A)) begin

.....

end

//bit[31:0] Y

uvm_hdl_read("dut.X.Y[15:0]",B) //错误!

使用VPI访问缺点:不能按位域驱动和读取。对于多bit信号,无法只对其中的部分bit操作。

一般而言对于黑盒验证中的加密代码,使用Hierarchy和VPI方式都是无法获取加密代码内部信号的状态。当然如果在已知加密代码层次前提下,通过一些处理,还是可以通过Hierarchy方式进行后门操作。

浙公网安备 33010602011771号

浙公网安备 33010602011771号