verilog中右移符号>>>和>>的区别

下面首先定义输入输出:a和b都是有符号位的5bit端口,c和d是无符号位的5bit端口。

input signed [4:0] a;

input signed [4:0] b;

output [4:0] c;

output [4:0] d;

//右移一位

assign b = a >>> 1;

assign d = c >>> 1;

//右移二位

assign b = a >>> 2;

assign d = c >>> 2;

仿真结果

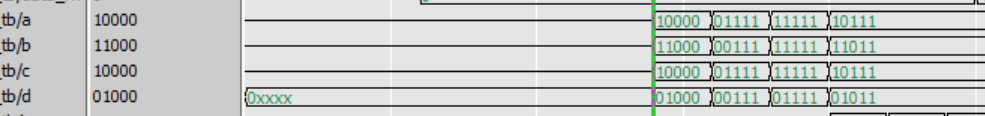

向右移1位的运算结果

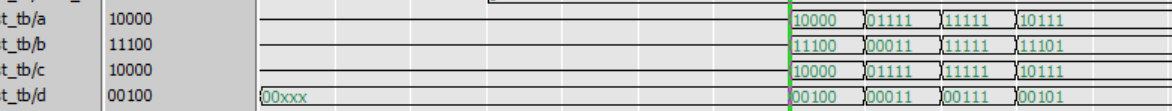

向右移2位的运算结果

结论

1、有符号数,符号位为1,使用>>>,高位补1;

2、有符号数,符号位为0,使用>>>,高位补0(和>>相同);

3、无符号数,无论最高位是什么,使用>>>,高位补0;

浙公网安备 33010602011771号

浙公网安备 33010602011771号