Lockup - enhance timing closure

ref link: https://www.edn.com/enhanced-timing-closure-using-latches/

1. complexity & importance of hold fixing

当代SoC timing timing closure的效率很大程度上取决于timing fix的效率。当技术发展到深亚微米级,芯片复杂度与日俱增,timing closure不仅仅受限于工具优化。STA team需要做很多的手动优化,成为了设计周期中的重要工作。另一方面signoff coner和cell variation的增多让标准的setup hold fixing也加大了难度。setup可以比较容易被满足,只要放宽clock频率,但是hold需要完全被满足。这篇文章谈论一下在在一些特殊的timing senerio下使用latch来帮助hold timing fix。

2. lockup insertion

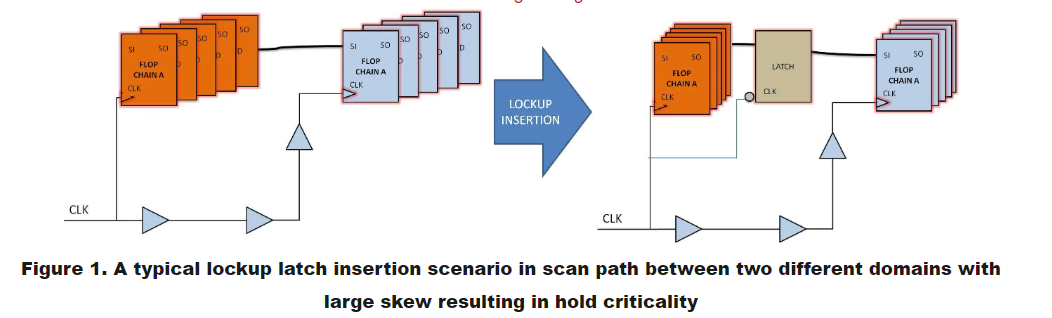

hold fixing通常通过增加data path的delay来完成,比如增加buffer。但是有一些情况下不能插buffer,比如scan chain上mix clock的case:

3. lockup增加hold余量

考虑蓝色ff(clk2,D2,G1)的clk2上升沿略快于橙色ff(clk1,D1.G1)clk1上升沿的情况,当蓝色ff时钟上升沿到达,橙色ff的G1必须保持一定的时间以保证蓝色ff采集到数据,但是该hold time时间内如果橙色ff时钟上升沿也到达就可能会改变G1的状态,导致蓝色ff采集到亚稳态。如果在橙色ff后增加一个时钟下降沿触发的latch,则橙色ff 输入端D1发生的变化则会在clk1半个周期后才传达到蓝色ff输入端,因此就增加了后一个ff半个周期的hold余量。

浙公网安备 33010602011771号

浙公网安备 33010602011771号