基于FPGA的16QAM+卷积编码Viterbi译码通信系统开发,包含帧同步,高斯信道,误码统计,可设置SNR

1.引言

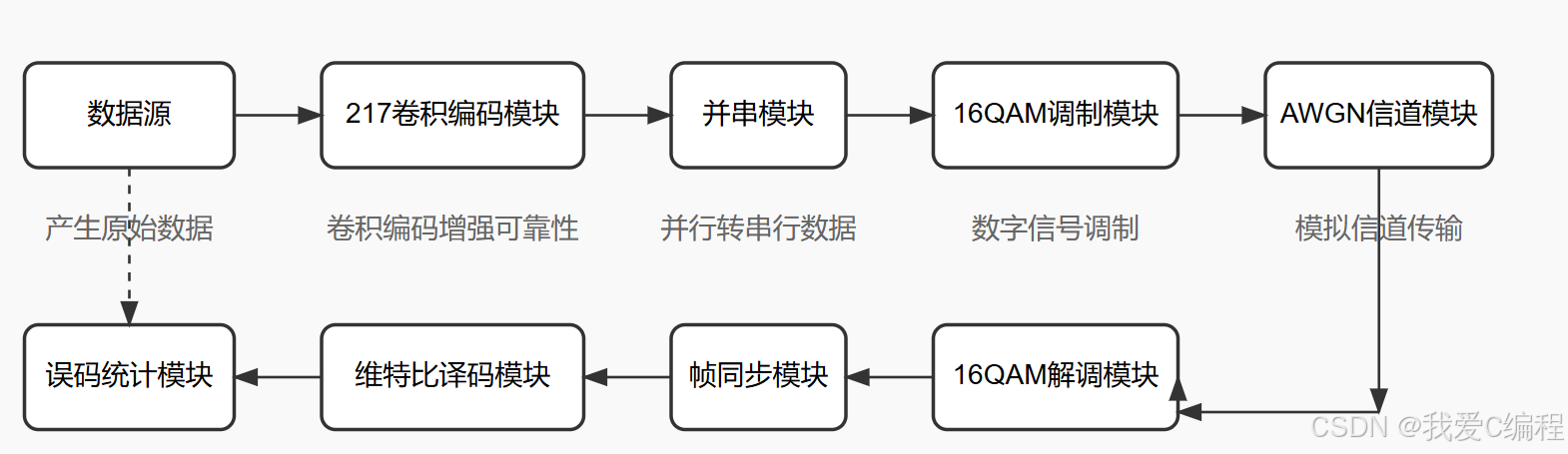

基于FPGA的16QAM+卷积编码Viterbi译码通信系统开发,包含帧同步,高斯信道,误码统计,可设置SNR。系统包括16QAM调制模块,16QAM解调模块,217卷积编码模块,维特比译码模块,AWGN信道模块,误码统计模块,帧同步模块,数据源模块等。

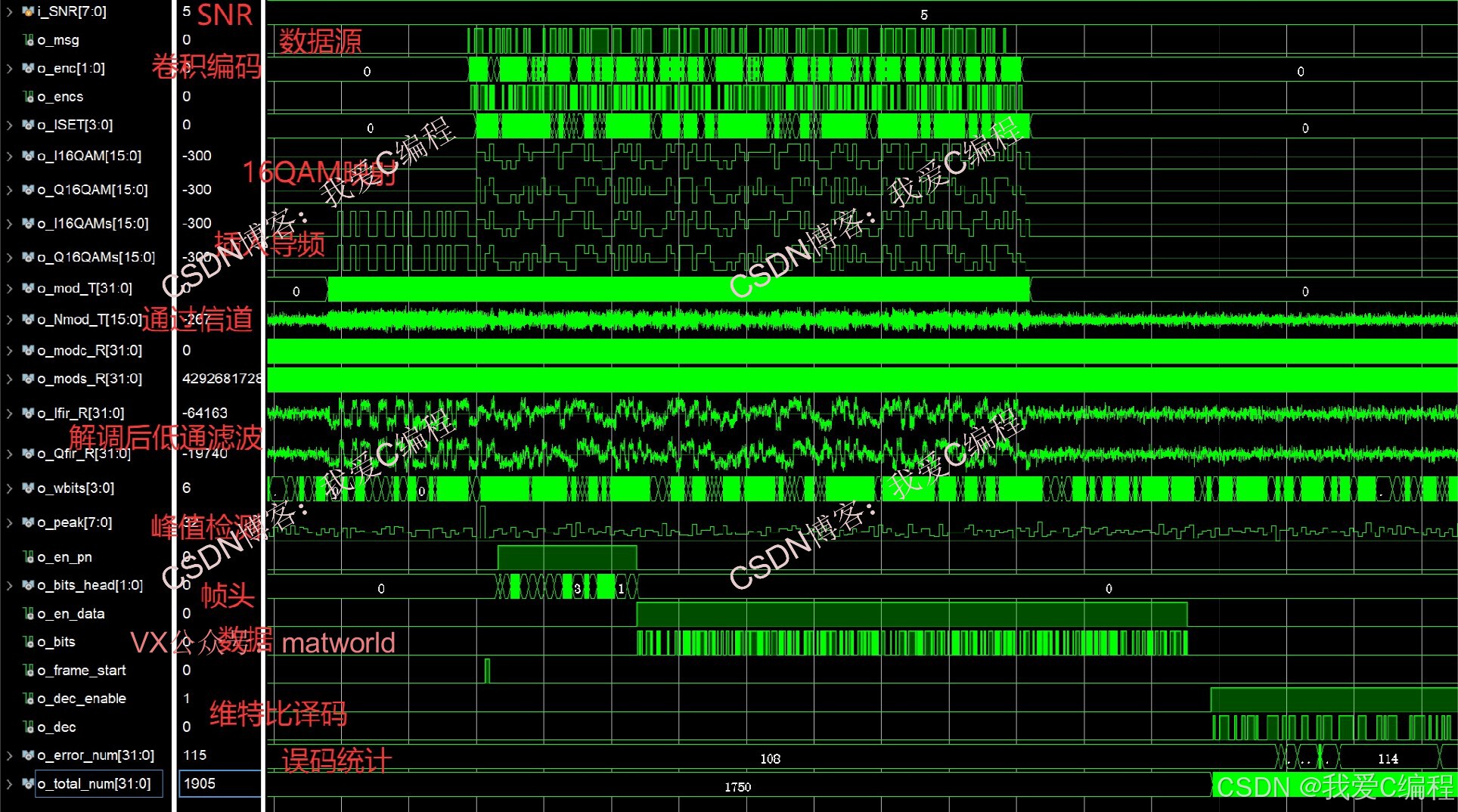

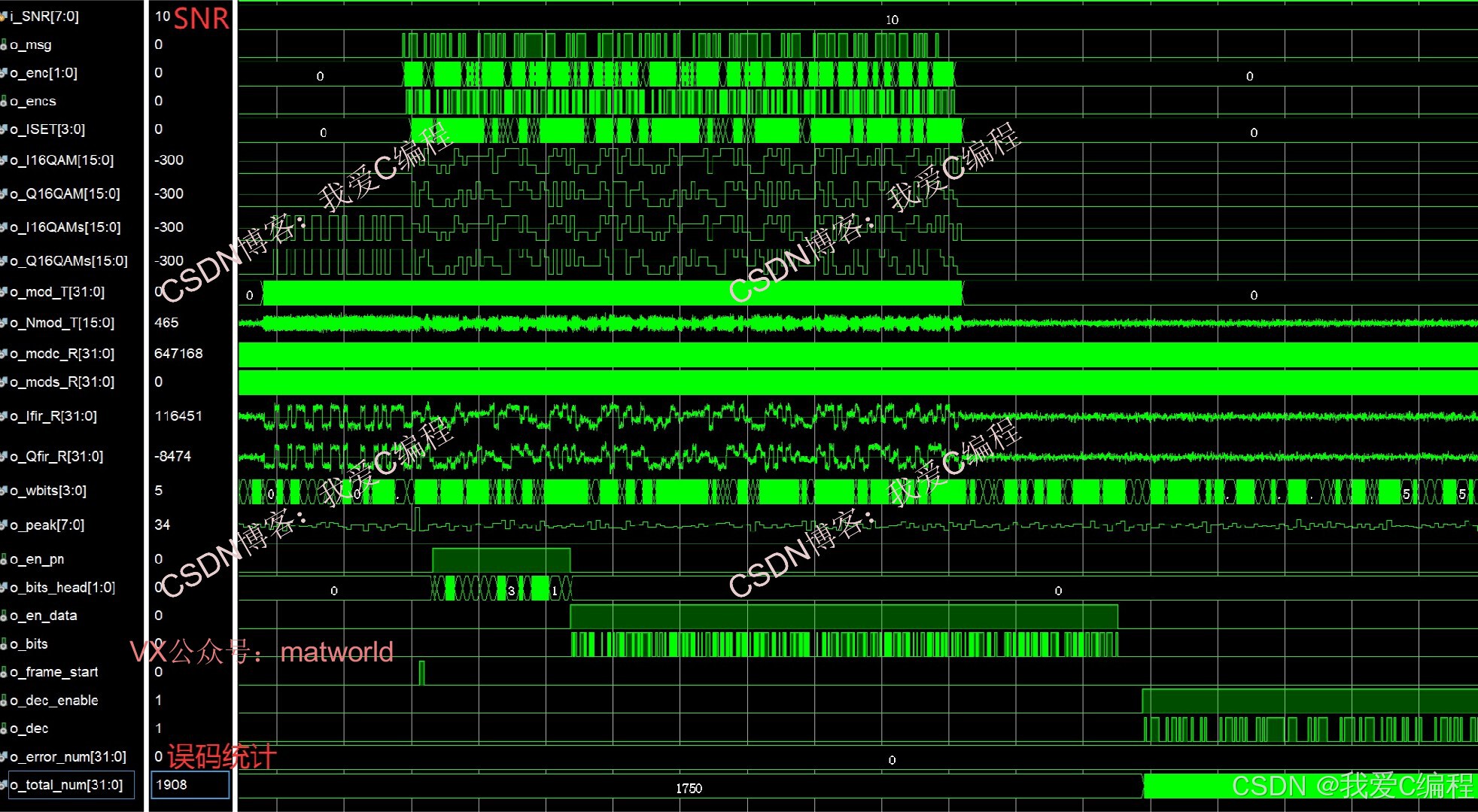

2.算法仿真效果

3.算法涉及理论知识概要

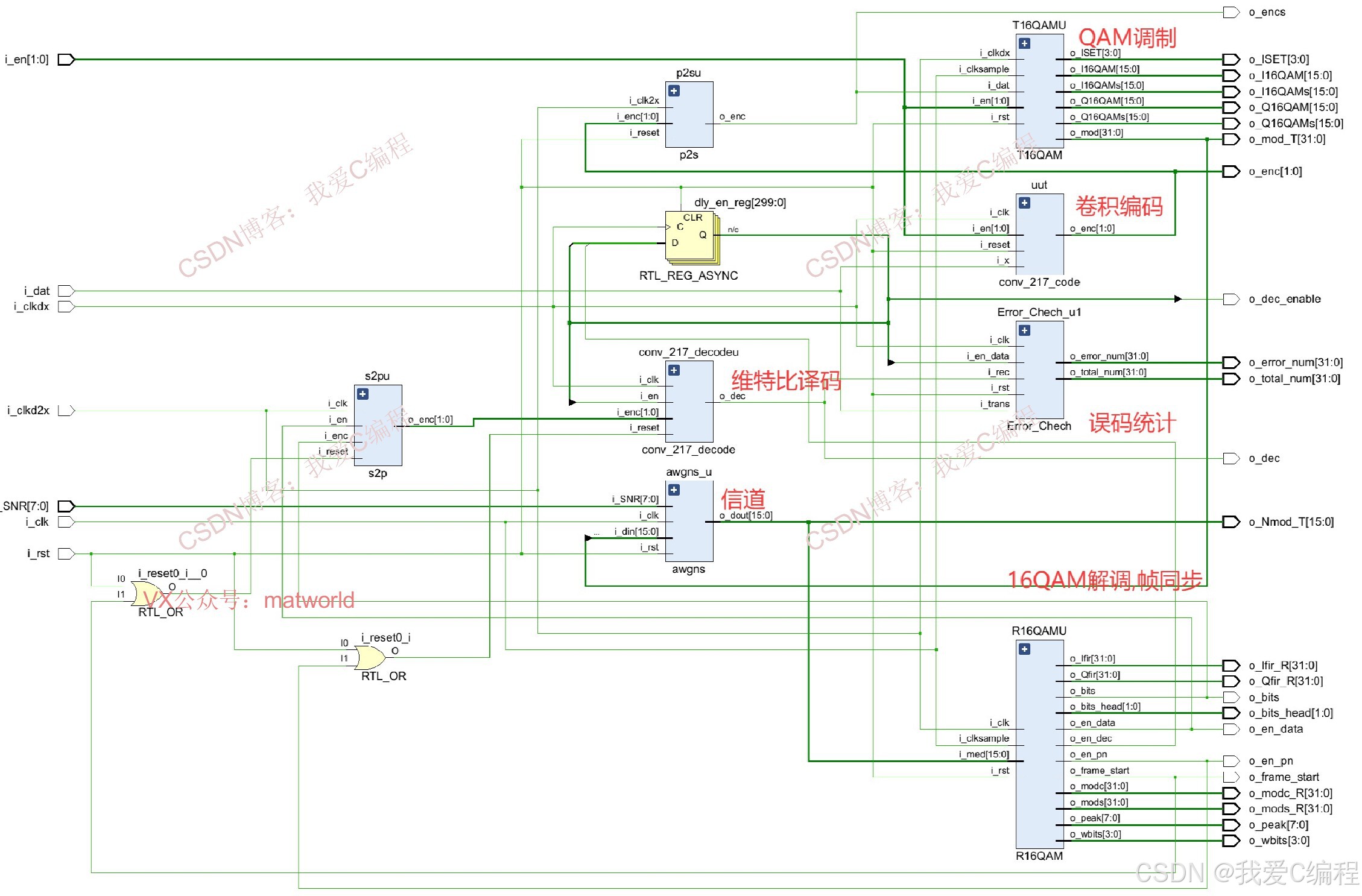

整体系统结构如下所示:

4.Verilog程序接口

module TOPS_16QAM( input i_clk, input i_clkdx, input i_clkd2x, input i_rst, input signed[7:0]i_SNR, input[1:0]i_en, input i_dat, //卷积编码 output [1:0]o_enc, output o_encs, output [3:0]o_ISET, output signed[15:0]o_I16QAM, output signed[15:0]o_Q16QAM, output signed[15:0]o_I16QAMs, output signed[15:0]o_Q16QAMs, output signed[31:0]o_mod_T, output signed[15:0]o_Nmod_T, output signed[31:0]o_modc_R, output signed[31:0]o_mods_R, output signed[31:0]o_Ifir_R, output signed[31:0]o_Qfir_R, output [3:0]o_wbits, output o_bits, output [1:0]o_bits_head, output [7:0]o_peak, output o_en_data, output o_en_pn, output o_frame_start, output o_dec_enable, output o_dec, output signed[31:0]o_error_num, output signed[31:0]o_total_num );

浙公网安备 33010602011771号

浙公网安备 33010602011771号