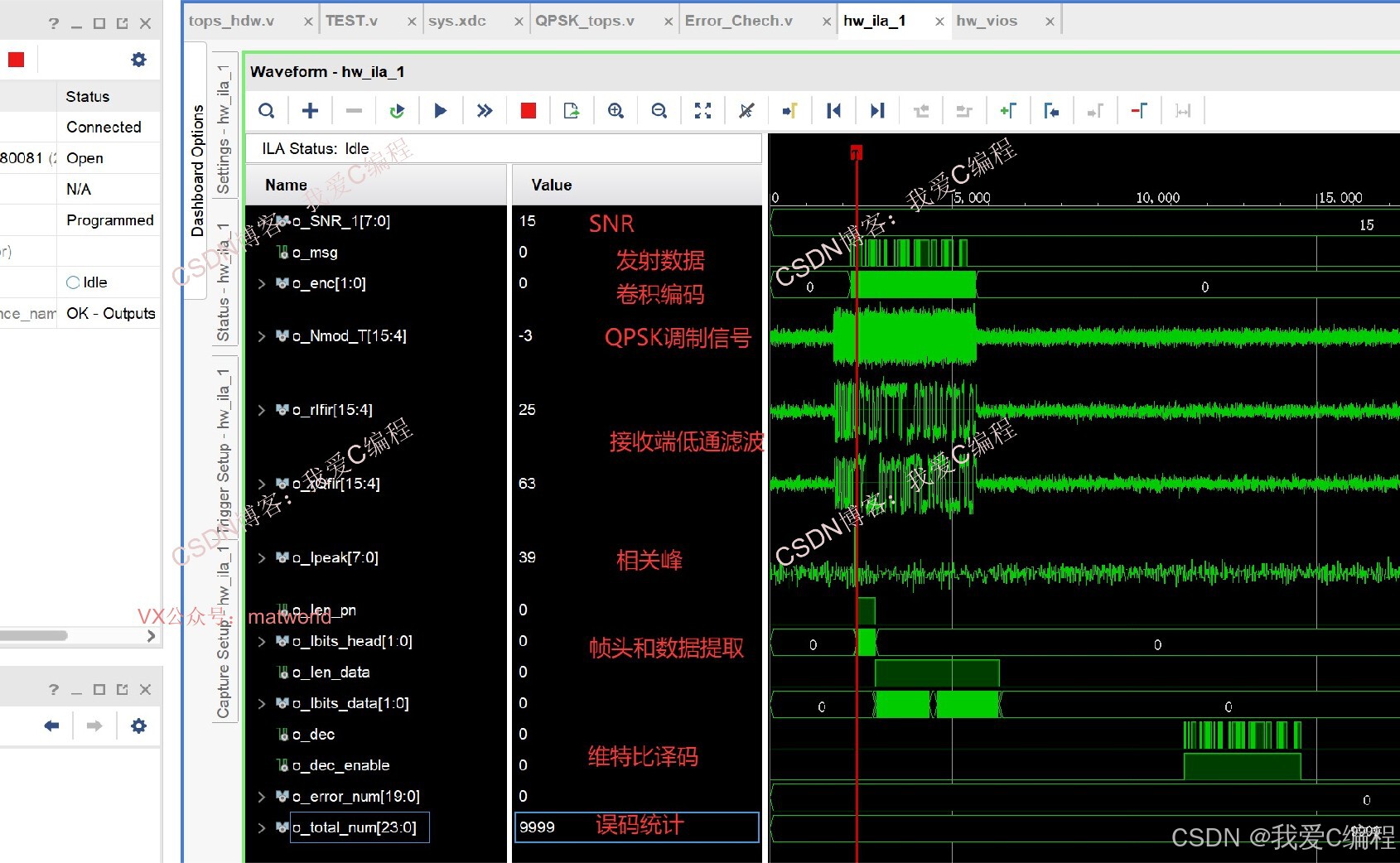

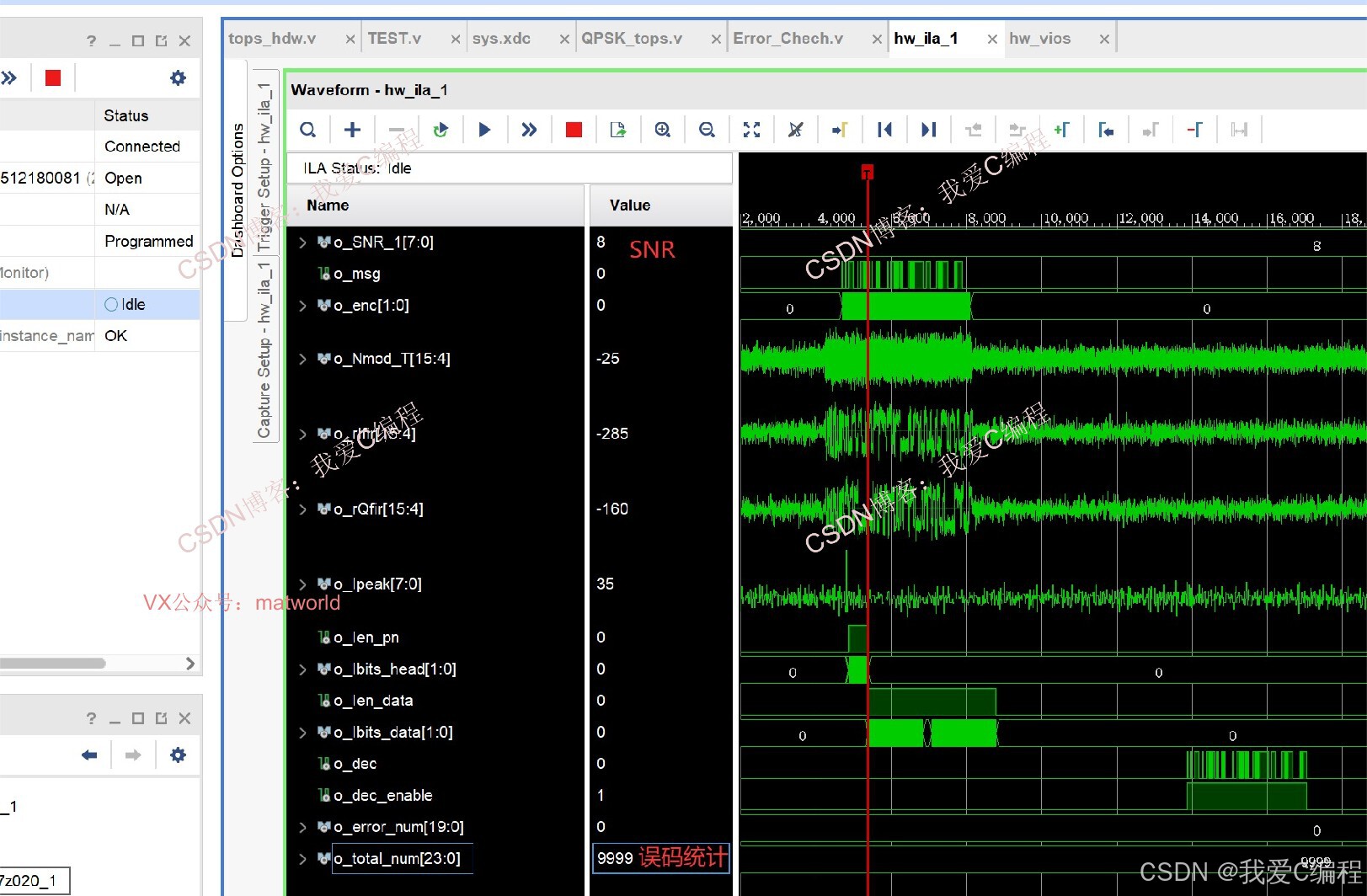

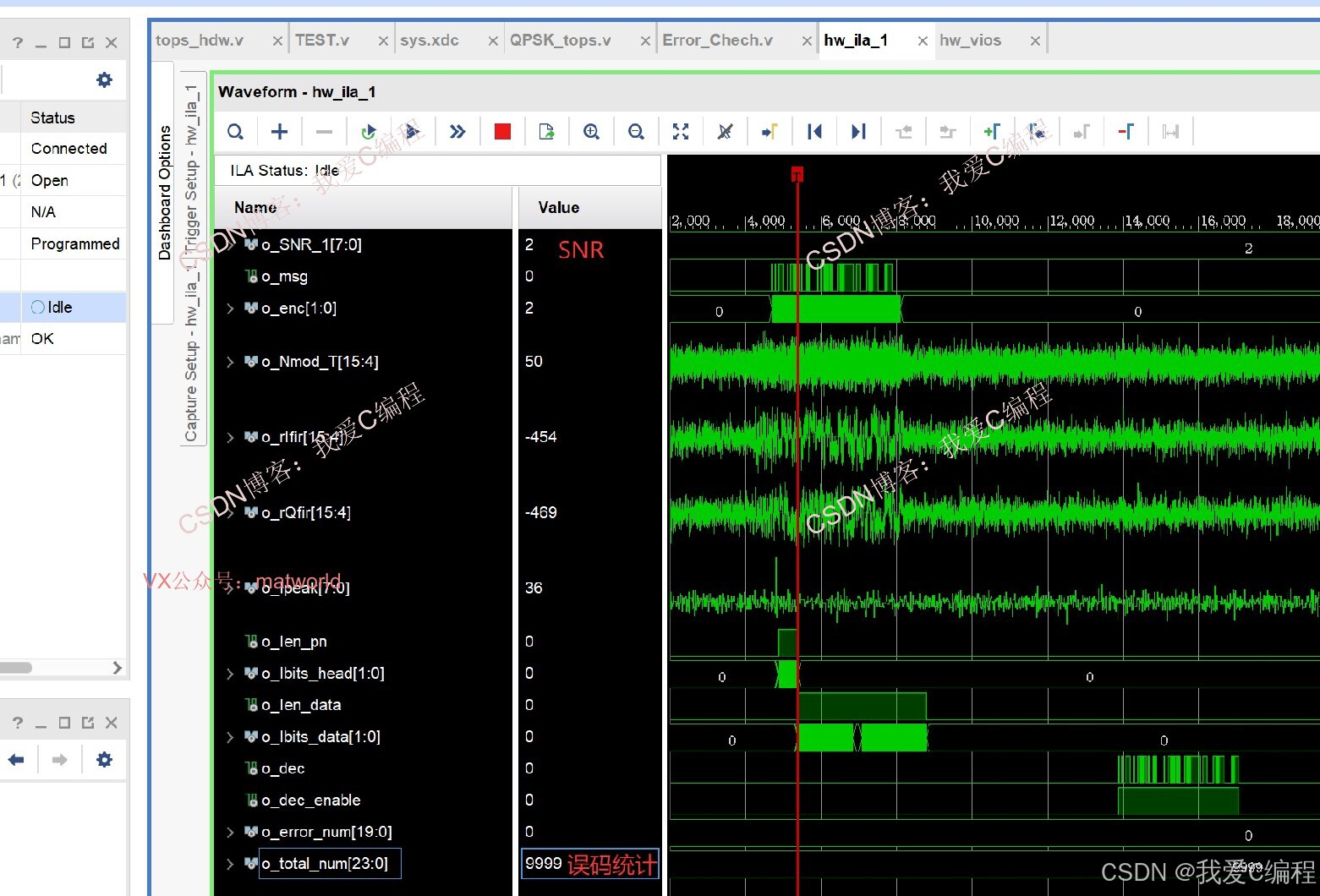

【硬件测试】基于FPGA的QPSK软解调+卷积编码Viterbi译码系统开发,包含帧同步,信道,误码统计,可设置SNR

1.引言

基于FPGA的QPSK软解调+卷积编码Viterbi译码通信系统开发,包含帧同步,高斯信道,误码统计,可设置SNR。系统包括QPSK调制模块,QPSK软解调模块,217卷积编码模块,维特比译码模块,AWGN信道模块,误码统计模块,帧同步模块,数据源模块等。

2.算法仿真效果

3.算法涉及理论知识概要

整体系统结构如下所示:

数据源模块 → 217卷积编码模块 → QPSK调制模块 → AWGN信道模块 →

QPSK软解调模块 → 帧同步模块 → 维特比译码模块 → 误码统计模块

4.Verilog程序接口

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2024/11/04 19:54:30 // Design Name: // Module Name: tops_hdw // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module tops_hdw( input i_clk, input i_rst, output reg [3:0] led ); wire signed[1:0]o_en; wire o_msg; wire dat_clk; wire dat_2clk; signaler signaler_u( .i_clk (i_clk), .i_rst (~i_rst), .o_en(o_en), .o_bits(o_msg), .dat_clk(dat_clk), .dat_2clk(dat_2clk) ); //设置SNR wire signed[7:0]o_SNR; vio_0 your_instance_name ( .clk(i_clk), // input wire clk .probe_out0(o_SNR) // output wire [7 : 0] probe_out0 ); wire [1:0]o_enc; wire signed[15:0]o_Ifir; wire signed[15:0]o_Qfir; wire signed[15:0]o_Nmod_T; wire signed[31:0]o_rmodc; wire signed[31:0]o_rmods; wire signed[31:0]o_rIfir; wire signed[31:0]o_rQfir; wire [1:0]o_Ibits_data; wire [1:0]o_Ibits_head; wire [7:0]o_Ipeak; wire o_Ien_data; wire o_Ien_pn; wire [1:0]o_Qbits_data; wire [1:0]o_Qbits_head; wire [7:0]o_Qpeak; wire o_Qen_data; wire o_Qen_pn; wire signed[31:0]o_error_num; wire signed[31:0]o_total_num; wire o_dec_enable; wire o_dec; QPSK_tops uut( .i_clk(i_clk), .i_clkdx(dat_clk), .i_clkd2x(dat_2clk), .i_rst (~i_rst), .i_en (o_en), .i_bits (o_msg), .i_SNR (o_SNR), .o_enc (o_enc), .o_Ifir (o_Ifir), .o_Qfir (o_Qfir), .o_Nmod_T (o_Nmod_T), .o_rmodc(o_rmodc), .o_rmods(o_rmods), .o_rIfir(o_rIfir), .o_rQfir(o_rQfir), .o_Ibits_data (o_Ibits_data), .o_Ibits_head (o_Ibits_head), .o_Ipeak (o_Ipeak), .o_Ien_data (o_Ien_data), .o_Ien_pn (o_Ien_pn), .o_Iframe_start (), .o_Qbits_data (o_Qbits_data), .o_Qbits_head (o_Qbits_head), .o_Qpeak (o_Qpeak), .o_Qen_data (o_Qen_data), .o_Qen_pn (o_Qen_pn), .o_Qframe_start (), .o_dec_enable (o_dec_enable), .o_dec (o_dec), .o_error_num (o_error_num), .o_total_num (o_total_num) ); //ila篇内测试分析模块 ila_0 ila_u ( .clk(i_clk), // input wire clk .probe0({ o_msg,o_SNR,o_enc,o_Nmod_T[15:4],//24 o_rIfir[15:4],o_rQfir[15:4],//24 o_Ibits_data,o_Ibits_head,o_Ipeak,o_Ien_data,o_Ien_pn,//14 o_dec_enable,o_dec,//2 o_error_num[19:0],o_total_num[23:0]//44 }) ); endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号