基于FPGA的4FSK+帧同步系统verilog开发,包含testbench,高斯信道,误码统计,可设置SNR

1.算法仿真效果

vivado2019.2仿真结果如下(完整代码运行后无水印):

设置SNR=25db

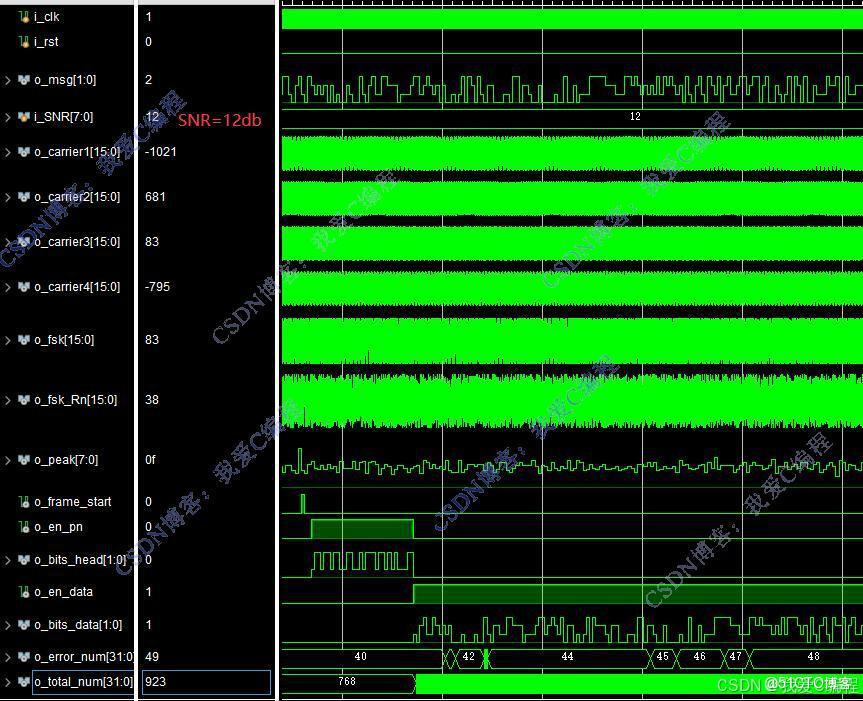

设置SNR=12db

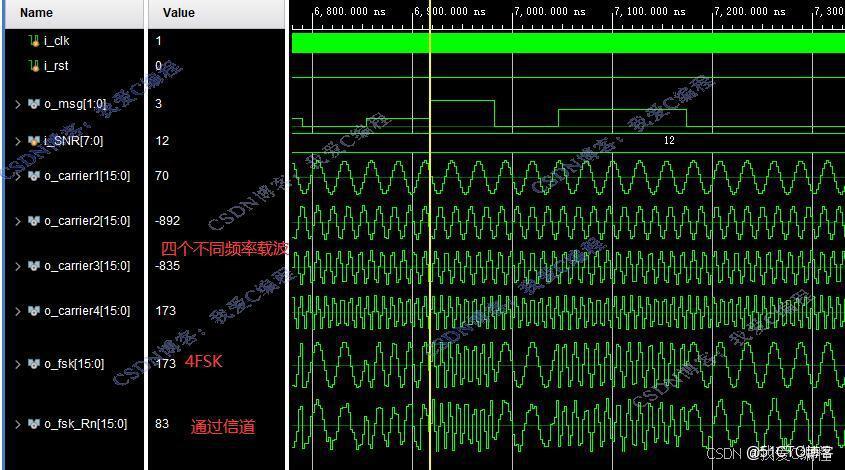

将波形局部放大:

仿真操作步骤可参考程序配套的操作视频。

2.算法涉及理论知识概要

四频移键控(4FSK)是一种常用的数字调制方法,具有较高的频带利用率和抗干扰性能。它利用不同的频率来传输二进制数据,通常应用于无线通信和数据传输等领域。

2.1 原理与数学公式

4FSK调制的基本原理是将输入的二进制数据转换为不同频率的信号,以实现数据的传输。解调则是将接收到的不同频率的信号还原为原始的二进制数据。

在4FSK调制中,输入的二进制数据被分为两组,每组有两个比特。根据这两个比特的值,选择相应的频率输出。具体来说,有四个频率f1、f2、f3、f4与之对应,每个频率都代表一个二进制组合(00、01、10、11),即十进制的0,1,2,3。

频率选择:根据输入的比特组合选择相应的频率输出。例如,当输入为“00”时,选择频率f1;当输入为“01”时,选择频率f2;当输入为“10”时,选择频率f3;当输入为“11”时,选择频率f4。

调制信号:将选择的频率进行幅度调制,以便在传输过程中具有更好的抗干扰性能。通常采用开关键控(OOK)或脉冲幅度调制(PAM)等方法进行幅度调制。

解调信号:在接收端,根据不同频率的信号进行解调。首先通过带通滤波器将所需的频率信号提取出来,然后通过解调器将其还原为原始的二进制数据。解调方法通常采用相干解调或非相干解调。

2.2 帧同步

在数字通信中,信息通常是以帧为单位进行组织和传输的。帧同步的目的是确定每一帧的起始位置,以便接收端能够正确地解调出每帧中的数据。

设发送的帧结构为:帧同步码 + 信息码元序列 。帧同步码是具有特定规律的码序列,用于接收端识别帧的起始。

帧同步的过程就是在接收序列中寻找与帧同步码匹配的位置,一旦找到匹配位置,就确定了帧的起始位置,后续的码元就可以按照帧结构进行正确的划分和处理。

3.Verilog核心程序

//调制

FSK_mod FSK_mod_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_en (i_en),

.i_bits (i_bits),

.o_carrier1(o_carrier1),

.o_carrier2(o_carrier2),

.o_carrier3(o_carrier3),

.o_carrier4(o_carrier4),

.o_fsk (o_fsk)

);

awgns awgns_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,

.i_din(o_fsk),

.o_noise(),

.o_dout(o_fsk_Rn)

);

解调//解调//解调//解调//解调//解调//解调//解调//解调//解调//解调//解调//解调

FSK_demod FSK_demod_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_fsk(o_fsk_Rn),

.o_de_fsk1(o_de_fsk1),

.o_de_fsk2(o_de_fsk2),

.o_de_fsk3(o_de_fsk3),

.o_de_fsk4(o_de_fsk4),

.o_de_ffsk1(),

.o_de_ffsk2(),

.o_de_ffsk3(),

.o_de_ffsk4(),

.o_bits(o_bits),

.o_bits_data (o_bits_data),

.o_bits_head (o_bits_head),

.o_peak (o_peak),

.o_en_data (o_en_data),

.o_en_pn (o_en_pn),

.o_frame_start (o_frame_start)

);

//error calculate

Error_Chech Error_Chech_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_trans(i_bits),

.i_en_data(o_en_data),

.i_rec(o_bits_data),

.o_error_num(o_error_num),

.o_total_num(o_total_num),

.o_rec2()

);

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号