m基于CCSDS标准的LDPC编码器的FPGA实现,包含testbench,码长1024,码率0.5

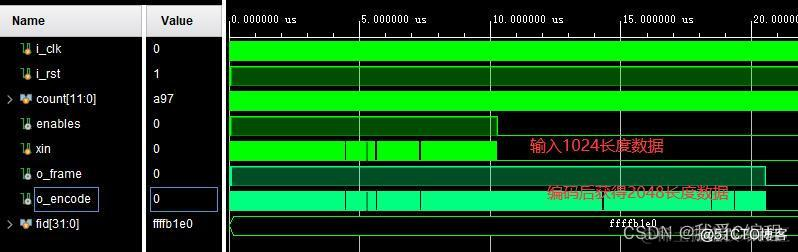

1.算法仿真效果

vivado2019.2仿真结果如下:

2.算法涉及理论知识概要

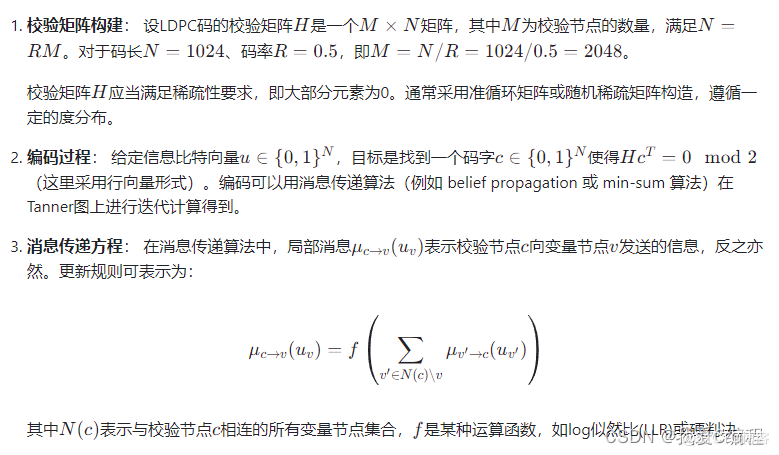

LDPC码是一种具有稀疏校验矩阵的线性分组码,由Robert G. Gallager在1962年首次提出。它利用图论中的 Tanner 图来表示其编解码结构,其中节点分为变量节点和校验节点。变量节点对应于消息比特,而校验节点则对应于对变量节点的线性约束。对于码长为N、码率为R的LDPC码,其编码过程可以通过以下步骤实现:

CCSDS标准定义了一套适用于空间通信系统的LDPC编码方案,该方案规定了特定的校验矩阵结构和编码流程。对于CCSDS-LDPC(1024,512)码,其特点是使用准循环结构,确保了良好的纠错性能和较低的实现复杂度。

在实际编码过程中,CCSDS LDPC编码器通常采用一种高效的硬件友好的编码算法,例如累积和编码(Accumulate-Repeat-Jagged-Edge,ARJ)或其他适合于准循环结构的算法。

若已知CCSDS-LDPC(1024,512)码的校验矩阵H,编码过程可以简化为:

1).将信息比特序列按照指定方式填充到一个长度为1024的向量u中;

2).对于每一个校验节点对应的子矩阵块,计算其线性组合,如果结果不符合偶校验条件,则相应地翻转变量节点比特,直至满足所有校验关系。

3.Verilog核心程序

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2024/04/15 15:00:23 // Design Name: // Module Name: TEST_encoder_top // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module TEST_encoder_top(); reg i_clk;// 时钟信号 reg i_rst;// 复位信号 initial// 初始状态设置 begin i_clk = 0;// 初始化时钟信号为低电平 i_rst = 0;// 初始化复位信号为低电平 # 20 i_rst = 1;// 20个时间单位后复位信号变为高电平 end always # 5 i_clk = ~i_clk;// 产生时钟信号,每5个时间单位翻转一次 // 定义中间数据信号 reg xin; always @ (posedge i_clk or negedge i_rst)// 在时钟上升沿或复位信号有效时更新中间数据 begin if(!i_rst) xin <= 1'b0; else if(count >= 0 && count <= 1023)// 在特定计数值范围内从文件读取数据 #1 $fscanf(fid,"%d",xin);// 延迟1个时间单位后执行文件读取操作 else xin <= 1'b0;// 计数值超出范围时,中间数据清零 end wire o_frame; wire o_encode; // 实例化LDPC_tops模块 LDPC_tops LDPC_tops0( .i_clk (i_clk), .i_rst (i_rst), .i_x (xin), .i_en (enables), .o_frame (o_frame), .o_encode (o_encode) ); endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号