两次数字电路模拟作业迭代总结:从基础门电路到复杂组合逻辑的进阶之路

一、前言

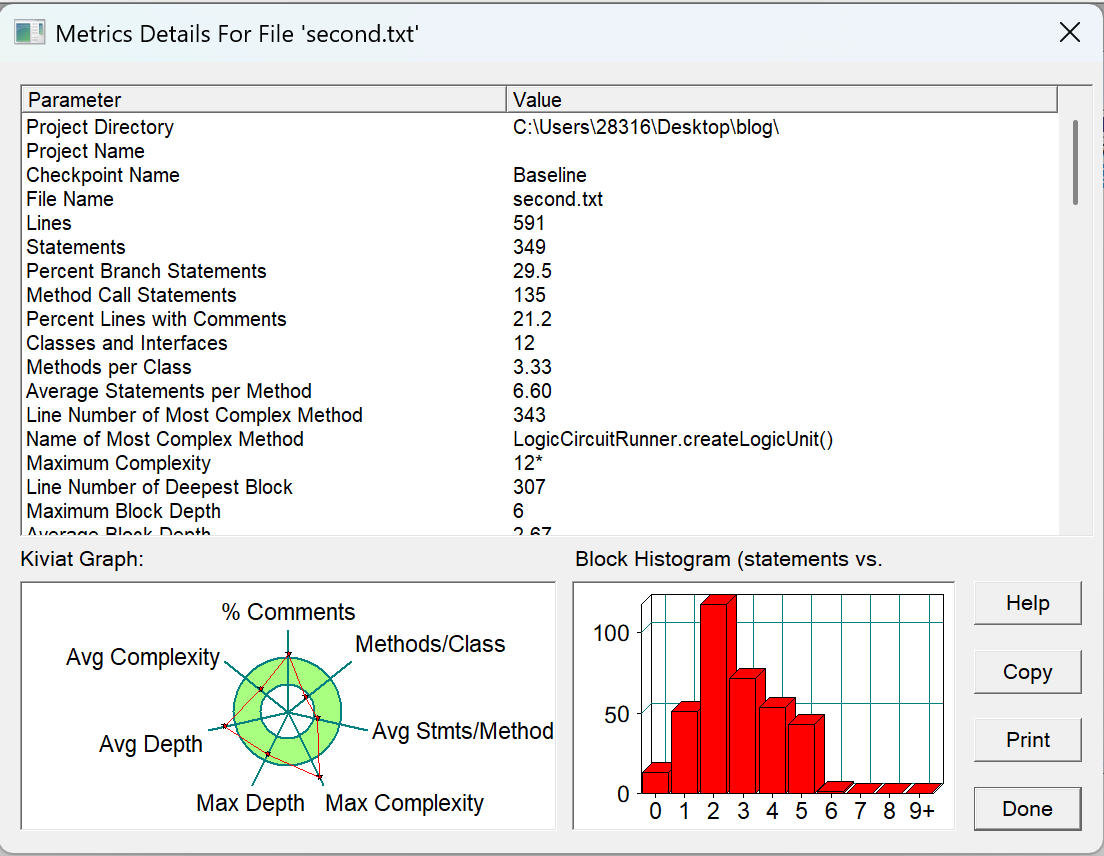

这两次数字电路模拟作业,简直是“从新手村到进阶副本”的升级体验。第一次作业聚焦最基础的五种逻辑门(与、或、非、异或、同或),核心是实现“输入解析-信号传递-结果计算”的基础流程;第二次直接新增了四种复杂元件(三态门、译码器、数据选择器、数据分配器),还加入了“控制引脚”的概念,引脚分类、输出格式都变得更复杂。

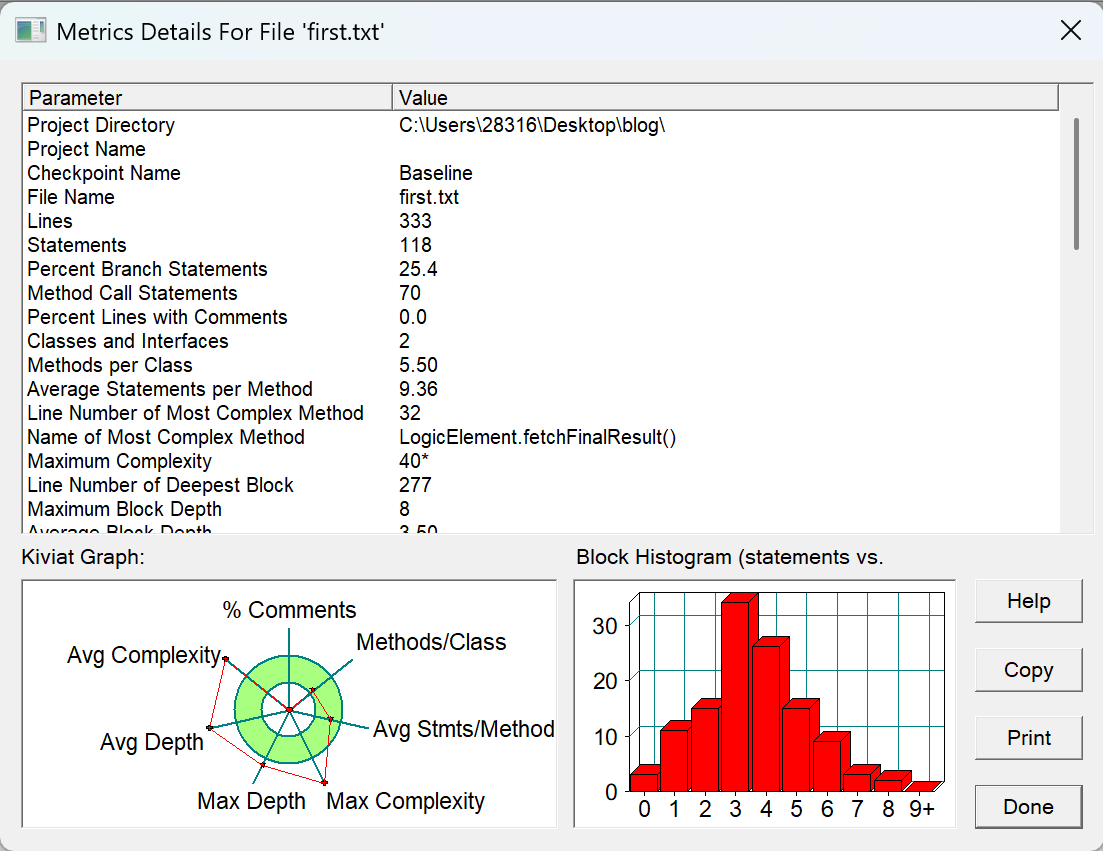

知识点上,第一次主要练Java抽象类、集合操作、正则解析和简单逻辑运算;第二次则升级到多态应用、复杂引脚管理、条件逻辑仿真(比如译码器的控制条件)和多样化输出适配。题量上,第一次代码约300行,第二次直接冲到500多行,新增的元件逻辑和输出格式处理占了不少篇幅,难度明显上了一个台阶——不仅要“能跑”,还要“适配不同元件的特殊规则”。

二、设计与分析

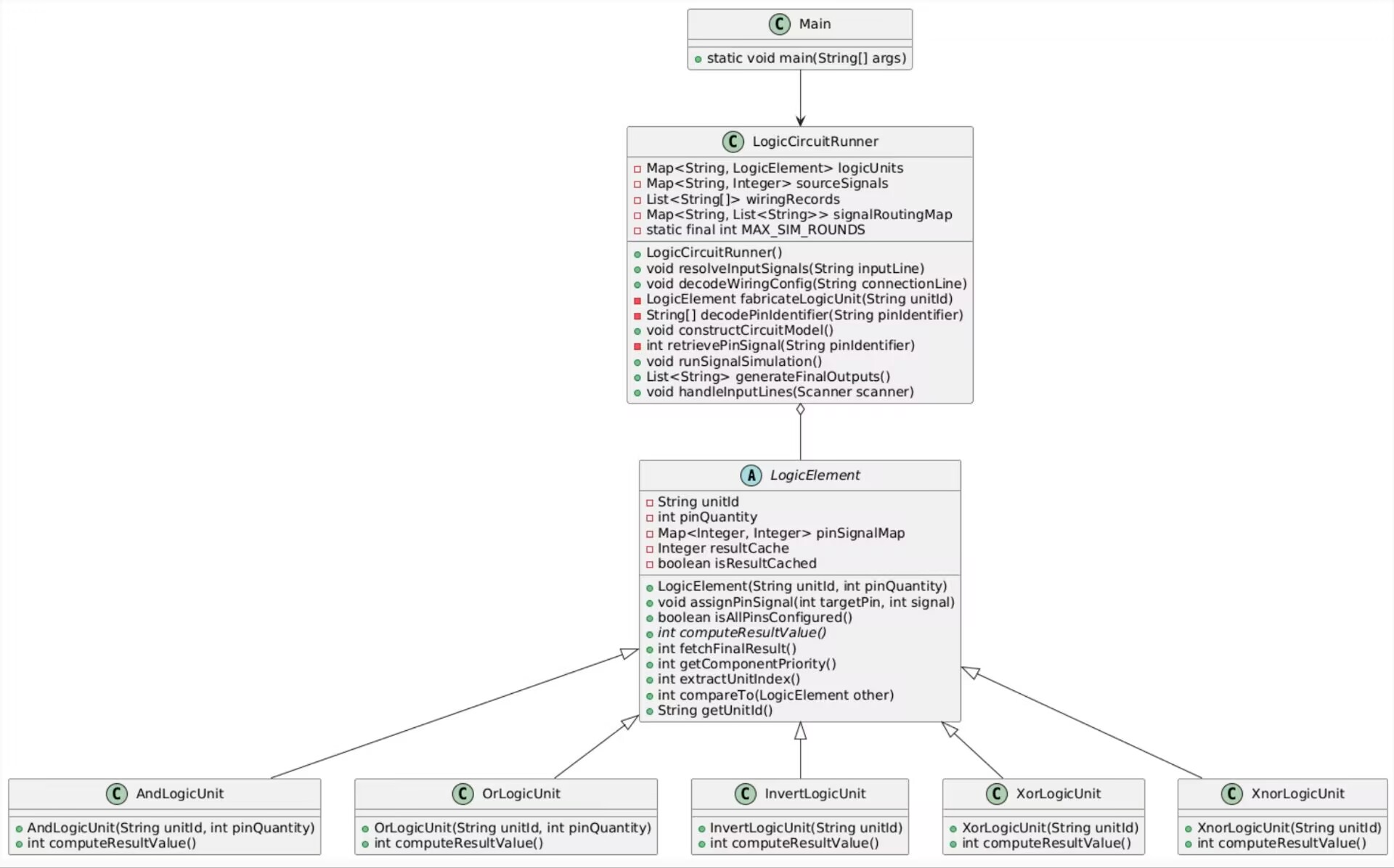

(一)第一次作业:基础逻辑门的“雏形实现”(first.java)

1. 类设计核心

第一次的设计很直接,核心就三层:

- 抽象类LogicElement:封装所有元件的公共属性(元件ID、引脚数、信号映射、结果缓存),定义抽象方法

computeResultValue(),还实现了排序接口(按元件类型+编号排序); - 五个具体门类:And、Or、Invert等,各自实现

computeResultValue(),比如与门判断所有输入为1才输出1,非门直接取反; - LogicCircuitRunner:“大管家”角色,负责解析输入信号、解析连线配置、创建元件实例、运行信号仿真、生成输出结果。

2. 核心逻辑与局限

核心流程是“解析→构建→仿真→输出”:先读INPUT行拿到原始信号,再读连线行建立引脚映射,然后创建对应元件,接着循环传递信号直到稳定,最后按优先级输出结果。

但局限也很明显:

- 引脚管理粗糙:所有引脚混在一起,用

pinSignalMap.size() == pinQuantity判断是否全部配置,比如非门只有1个输入引脚,与门有8个输入引脚,虽然能工作,但扩展性差——后面加带控制引脚的元件就完全不适用; - 元件扩展困难:新增元件需要修改LogicElement的优先级判断(switch语句),违反“开闭原则”;

- 输出格式单一:所有元件都输出“元件ID-0:信号值”,没法适配后续复杂元件的特殊输出需求(比如译码器要输出引脚号)。

不过作为第一次迭代,它实现了核心功能,比如输入<A-1 B-1>和连线[A A(2)1-1] [B A(2)1-2],能正确输出A(2)1-0:1,算是完成了“能用”的目标。

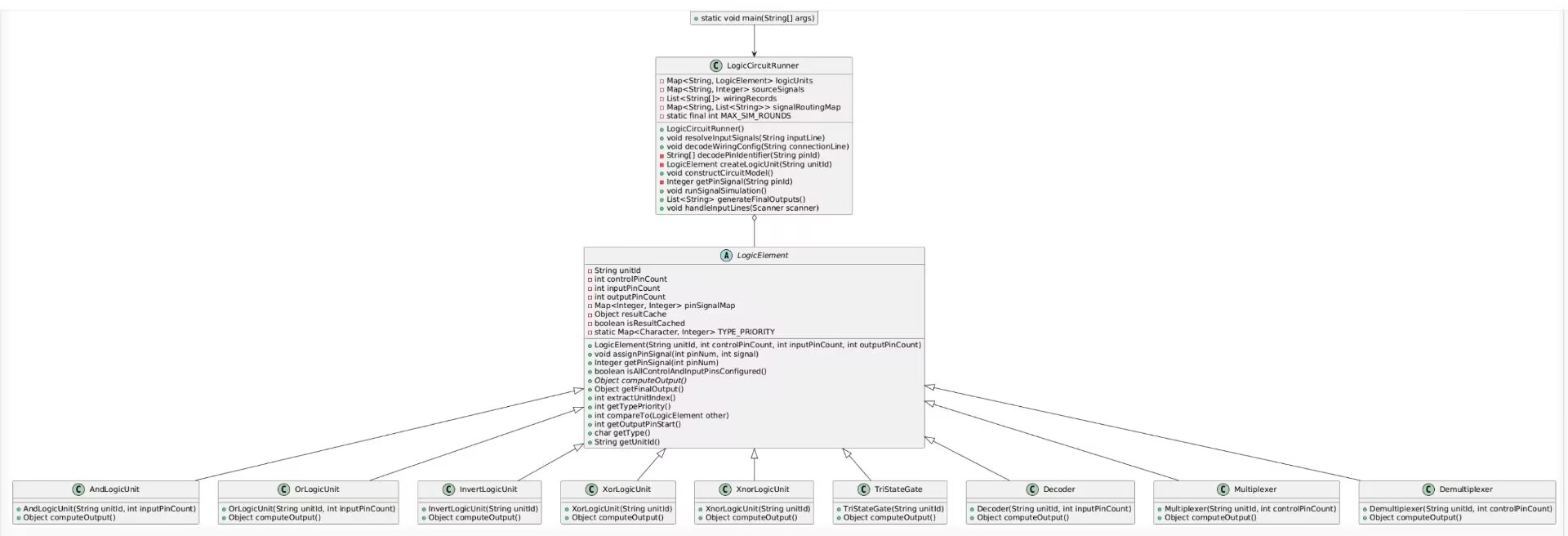

(二)第二次作业:复杂组合逻辑的“全面升级”(second.java)

1. 类设计的核心突破

第二次完全是“重构级”升级,完美适配了新增元件和复杂规则,核心改进有三点:

- 抽象类LogicElement优化:把引脚拆分为“控制引脚、输入引脚、输出引脚”三类,明确各自职责,

isAllControlAndInputPinsConfigured()专门检查前两类引脚是否配置,避免了第一次的“一刀切”判断;用TYPE_PRIORITYMap管理元件优先级,新增元件只需在Map中加一条记录,不用改核心逻辑,扩展性拉满; - 元件类扩展:新增TriStateGate(三态门)、Decoder(译码器)、Multiplexer(数据选择器)、Demultiplexer(数据分配器)四个类,各自实现

computeOutput(),充分利用多态特性,比如译码器要先判断控制条件,数据分配器要生成输出字符串; - Runner类精细化:解析逻辑更严谨(比如引脚标识符拆分用

lastIndexOf('-'),避免中间有短横线的错误),仿真时跳过输出引脚只更新控制/输入引脚,输出时根据元件类型适配不同格式(三态门输出-2,译码器输出“元件ID:引脚号”)。

2. 核心逻辑与优势

这次的信号仿真流程更贴合实际:先解析输入和连线,构建元件时收集所有涉及的元件ID,仿真时循环传递信号,直到没有信号变化或达到最大轮数(999次),最后按优先级排序输出。

最大的优势是“可扩展”和“适配性强”:比如新增一个元件,只需继承LogicElement并重写computeOutput(),在TYPE_PRIORITY中加个优先级,Runner的核心逻辑不用动;不同元件的输出格式差异,通过switch (unit.getType())精准处理,完全满足题目要求——比如三态门输出S1-2:1,译码器输出M(2)1:0,数据分配器输出F(3)1:-1------。

三、采坑心得:那些让我卡壳的“逻辑陷阱”

(一)第一次作业:引脚配置判断“想当然”

坑点:isAllPinsConfigured()用pinSignalMap.size() == pinQuantity判断所有引脚是否配置,但实际引脚编号是连续的(比如与门A(2)1的输入引脚是1、2),如果用户误连了引脚3,size会变成3,反而满足条件,导致计算错误。

测试结果:输入[A A(2)1-3] [B A(2)1-2],pinSignalMap.size()=2,等于pinQuantity=2,程序误以为配置完成,实际输入引脚1没信号,输出错误结果1。

原因:只看数量不看引脚编号的连续性,忽略了“引脚编号从1开始且连续”的题目约束。

解决:第二次作业改成按引脚范围检查(控制引脚0~controlPinCount-1,输入引脚从controlPinCount开始),精准判断是否所有必要引脚都有信号。

(二)第二次作业:控制引脚的“排序混乱”

坑点:译码器的控制引脚是0(S1)、1(S2)、2(S3),输入引脚从3开始,但仿真时信号传递顺序错误,先给输入引脚传信号,再给控制引脚传,导致译码器控制条件不满足,输出null。

测试结果:输入[C M(2)1-0] [D M(2)1-1] [E M(2)1-2] [A M(2)1-3] [B M(2)1-4](C=1、D=0、E=0,A=0、B=0),预期输出M(2)1:0,实际因控制引脚信号后传递,译码器输出无效,被忽略。

原因:信号传递时按连线记录顺序遍历,没有优先处理控制引脚的信号,导致元件计算时控制条件未就绪。

解决:在runSignalSimulation()中,先处理控制引脚相关的连线,再处理输入引脚,或者在元件计算前检查控制引脚是否就绪,确保控制条件优先满足。

(三)第二次作业:输出格式“适配错误”

坑点:数据选择器Z(k)的输出引脚编号是“控制引脚数+输入引脚数”(比如Z(1)1有1个控制引脚、2个输入引脚,输出引脚是3),但一开始误写为固定输出“-0”,导致输出格式错误。

测试结果:输入[C Z(1)1-0] [A Z(1)1-1] [B Z(1)1-2](C=0、A=1、B=0),预期输出Z(1)1-3:1,实际输出Z(1)1-0:1,不符合题目要求。

原因:没理解“输出引脚起始编号=控制引脚数+输入引脚数”的规则,直接沿用了第一次的固定“-0”格式。

解决:用getOutputPinStart()计算输出引脚编号,不同元件按需调用,比如基础逻辑门输出-0,三态门输出-2,数据选择器输出计算后的编号。

四、改进建议

(一)第一次作业:夯实基础,预留扩展空间

- 拆分引脚类型:即使是基础元件,也可以提前抽象“输入引脚”和“输出引脚”,避免后续迭代大幅重构;

- 优化引脚配置判断:不用size对比,而是按引脚编号范围检查(比如输入引脚1~n),减少无效输入导致的错误;

- 抽象优先级管理:用Map替代switch语句,后续新增元件时不用修改LogicElement的compareTo方法,更符合开闭原则。

(二)第二次作业:优化细节,提升健壮性

- 分离输出逻辑:不同元件的输出格式差异较大,可引入

OutputFormatter接口,让每个元件自己实现输出逻辑,Runner只需调用接口方法,减少switch语句的冗余; - 优化正则解析:比如解析元件ID的正则表达式(如

A\\((\\d+)\\)(\\d+)),可以预编译为Pattern常量,避免每次创建Matcher,提升解析效率; - 增加输入校验:题目中提到“一个输入引脚不能连接多个输出引脚”,但当前代码未处理,可在

decodeWiringConfig()中记录输入引脚的连接次数,重复连接时输出提示或忽略; - 简化信号仿真:当前仿真循环最多999次,可根据电路复杂度动态调整,或判断是否有未就绪的元件,避免无效循环。

(三)通用优化方向

- 引入接口分离职责:比如定义

PinConfigurable接口处理引脚配置检查,Computable接口处理计算逻辑,Outputable接口处理输出格式,让类职责更单一; - 日志打印辅助调试:在信号传递、元件计算时增加日志(比如“给A(2)1-1分配信号1”),方便定位仿真过程中的逻辑错误;

- 封装常用工具方法:比如引脚标识符解析、元件ID提取等,单独放在

LogicUtils工具类中,避免Runner类过于臃肿。

五、总结

(一)学到的东西

- 面向对象设计的“迭代思维”:第一次作业的抽象类只满足基础需求,第二次通过拆分引脚、引入Map管理优先级、扩展元件类,完美适配复杂需求,深刻体会到“预留扩展空间”的重要性——好的设计不是一蹴而就的,而是能支撑后续迭代;

- 复杂业务逻辑的“拆解能力”:面对“控制引脚+输入引脚+输出引脚”的复杂配置、不同元件的特殊计算规则,学会了“分而治之”——先封装公共逻辑,再处理特殊情况,比如把所有元件的公共属性放在LogicElement,特殊计算放在各自的computeOutput();

- 细节处理的“严谨性”:数字电路的仿真对细节要求极高,比如引脚编号的顺序、信号传递的优先级、输出格式的精准度,一个小错误就会导致整个电路计算失效,这让我养成了“先看题目规则,再写代码”的习惯。

(二)还要深入学习的方向

- 时序电路的处理:当前两次作业都是组合逻辑电路,后续还要学习带反馈的时序电路(如D触发器),需要掌握时钟信号、状态存储等知识;

- 异常输入的全面处理:题目提到后续迭代要增加异常输入检测,比如无效元件ID、重复引脚连接、引脚编号超出范围等,需要学习更完善的输入校验和异常处理机制;

- 性能优化:当电路元件数量多、连线复杂时,正则解析和信号仿真可能会变慢,需要学习缓存策略、并行计算等优化方法。

这两次作业虽然踩了不少“逻辑陷阱”,但每次解决问题后,都能明显感觉到自己在“面向对象设计”和“复杂业务逻辑处理”上的进步。从一开始只会写简单的逻辑判断,到后来能设计可扩展的抽象类、适配不同元件的特殊需求,这种“从功能实现到设计优化”的转变,比单纯掌握知识点更有价值,也为后续更复杂的数字电路模拟(如时序电路、子电路)打下了基础。

浙公网安备 33010602011771号

浙公网安备 33010602011771号