3.1 高级语言和机器指令中的运算

3.1.1 C语言中涉及的运算

1.按位运算

(1)按位运算符:符号 | 表示按位OR运算;符号& 表示按位AND运算;符号~ 表示按位NOT;符号^表示按位XOR运算。

(2)掩码操作:通过给定的一个位模式进行按位与,可以提取所需的位,然后可以对这些位进行“置1”“清0”“1测试”或”0测试“等,这里的位模式被称为掩码。

2.逻辑运算

(1)逻辑运算符:符号|| 表示OR运算;符号&& 表示AND运算;符号!表示NOT运算。

(2)与按位运算的区别:前者是非数值计算,,操作值只有:True,False,0表示True,1表示False;后者是一种数值计算,将两个操作数对应各二进位按照指定的逻辑运算规则进行计算。

3.移位运算

⑴移位操作有逻辑移位和算术移位两种。

⑵逻辑移位不考虑符号位,总是把高(低)位移出,低(高)位补0。对于无符号整数的逻辑左移,如果最高位移出的是1,则发生溢出。

⑶算术移位方式,左移时,高位移出,低位不0,每移一位,如果左移前、后符号为不同,则发生溢出;右移时,低位移出,高位补符号位。

⑷每左移一位,相当于数值扩大了一倍,所以左移可能会发生溢出,左移k位,相当于数值乘以2k;每右移一位,相当于数值缩小一半,右移k位,相当与数值除以2k。

4.位扩展和位截断运算

⑴进行位扩展时,扩展后的数值应保持不变。有两种位扩展方式:0扩展和符号扩展。

⑵0扩展用于无符号数,只要在短的无符号数前面添加足够的0即可。符号扩展用于补码表示的带符号整数,通过在短的带符号整数前添加足够多的符号位来扩展。

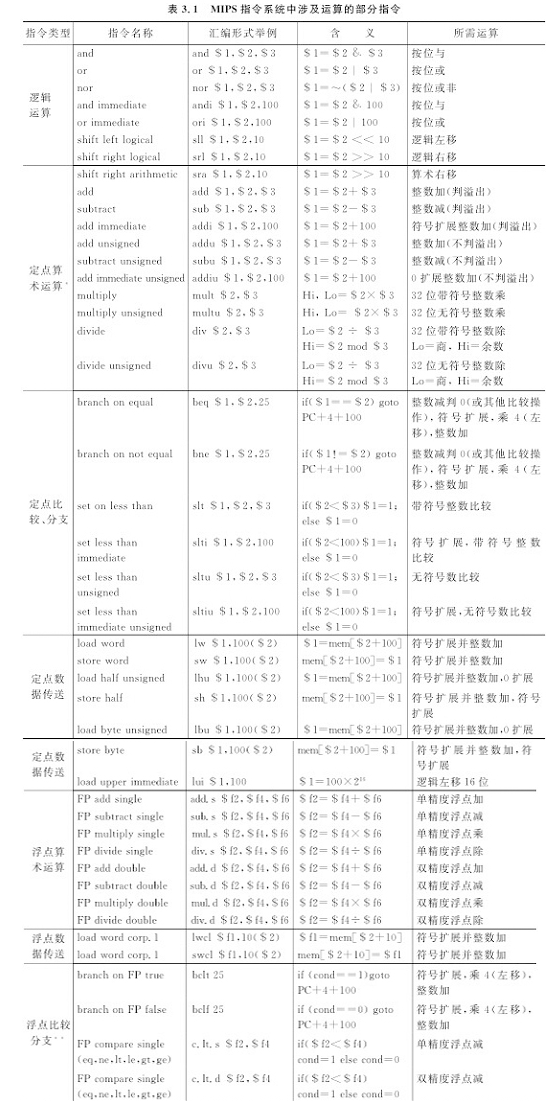

3.1.2 MIPS指令中涉及的运算

3.2 基本运算部件

一般情况下,用一个专门的算术逻辑部件(ALU)来完成基本逻辑运算和定点数加减算,各类定点乘除运算和浮点数运算则可利用加法器或ALU和移位器来实现,因此基本

运算部件是加法器、ALU和移位器,ALU的核心部件是加法器。

3.2.1 串行进位加法器

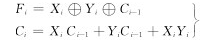

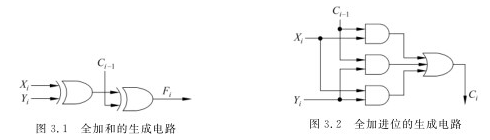

(1)全加器用来实现两个本位数加上低位进行位生成一位本位和以及一位向高位的进位;

(2)第i位的加法运算是指第i位的加数Xi,Yi和低位来的进位Ci-1三者相加,得到本位和Fi和第i位的进位输出Ci。

Fi和Ci的逻辑表达式

Fi、Ci被分别称为“全加和”和“全加进位”。

串行进位方式:对于图3.4所示的n位加法器,X与Y逐位相加,位间进位串行传送。

行波进位加法器:串行进位加法器中的最低位C0,它把进位逐步从低位扩展到最高位。

加法运算时间随两个加数位数n的增加而增加。当n较大时,串行进位的加法器将显著变慢。

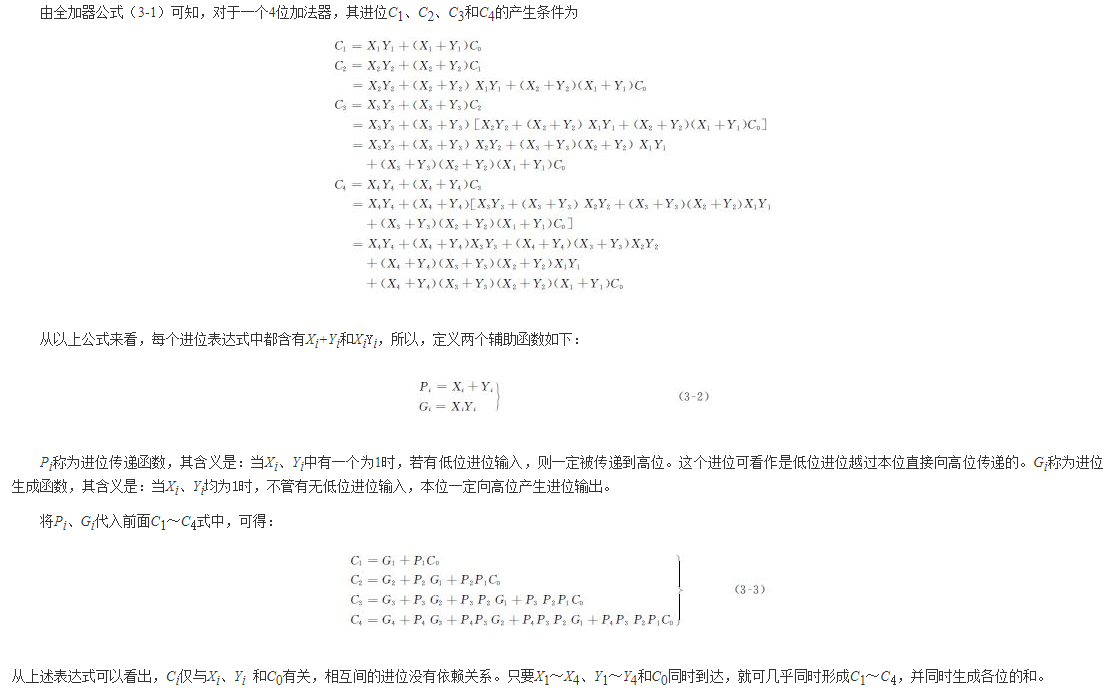

3.2.2 并行进位加法器

实现上述逻辑表达式(3-3)的电路称为先行进位(也称超前进位)部件,简称CLA部件。通过这种进位方式实现的加法器成为全先行进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

由图3.5可看出,从X、Y,到产生P、G需要1级门延迟,从P、G、C。到产生所有进位CG~CG需要2级门延迟,产生全部和需要1+2+3=6级门延迟(假定一个异或门等于

3级门延迟)。所以4位全先行进位加法器的关键路径长度为6级门延迟。从式(3.3)可知,更多位数的CLA部件只会增加逻辑门的输入端个数,而不会增加门

的级数,因此,如果用全先行进位方式构建更多位数加法器,从理论上讲,应该还是6级门延迟。但是由于CLA部件中连线数量和输入端个数的增多,使得实现电路中需要具有大驱

动信号和大扇入门。因而,当位数较多时,全先行进位实现方式不太现实。

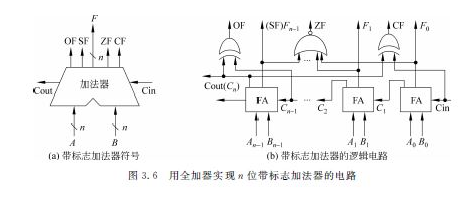

3.2.3 带标志加法器

n位无符号数加法器只能用于两个n位二进制数相加,不能进行无符号整数的减运算,也不能进行带符号整数的加/减运算。要能够进行无符号整数的加/减运算和带符号整数的

加/减运算,还需要在无符号数加法器的基础上增加相应的逻辑门电路,使得加法器不仅能计算和/差,还要能够生成相应的标志信息。

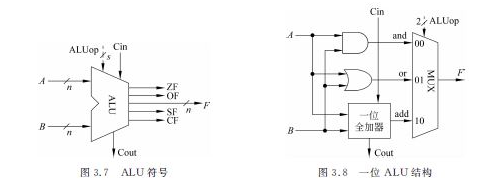

3.2.4 算数逻辑部件

ALU是一种能够进行多种算术运算与逻辑运算的组合逻辑电路,采用先行进位方式。

ALU中也可实现左(右)移一位和两位的操作,当然也可用一个移位寄存器实现移位。但这两种方式每次都只能固定移动一位或两位,有时移位指令要求一次移动若干位,对

于这种一次左移或右移多位的操作,通常用一个做在LU之外的桶型移位器实现。桶形移位器不同于普通移位寄存器,它利用大量多路选择器来实现数据的快速移位,移位操作能

够一次完成。在LU单独设置桶型移位器,还可简化ALU的控制逻辑,并实现移位操作和LU操作的并行性。

问题

各种加法器看不懂,不知道具体操作是如何进行的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号